Error check bit protocol converter

A protocol converter and error checking technology, which is applied in the direction of instrumentation, response error generation, error detection/correction, etc., can solve problems such as random failure of protocol conversion circuits, achieve high diagnostic coverage, and reduce common cause failure rate Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Preferred embodiments of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

[0026] Commonly used error check bits are divided into:

[0027] Error detection code (EDC), which can detect errors of no more than two bits in the data;

[0028] Error Correcting Code (ECC), which can detect no more than two bit errors in data and correct one bit error in data at the same time.

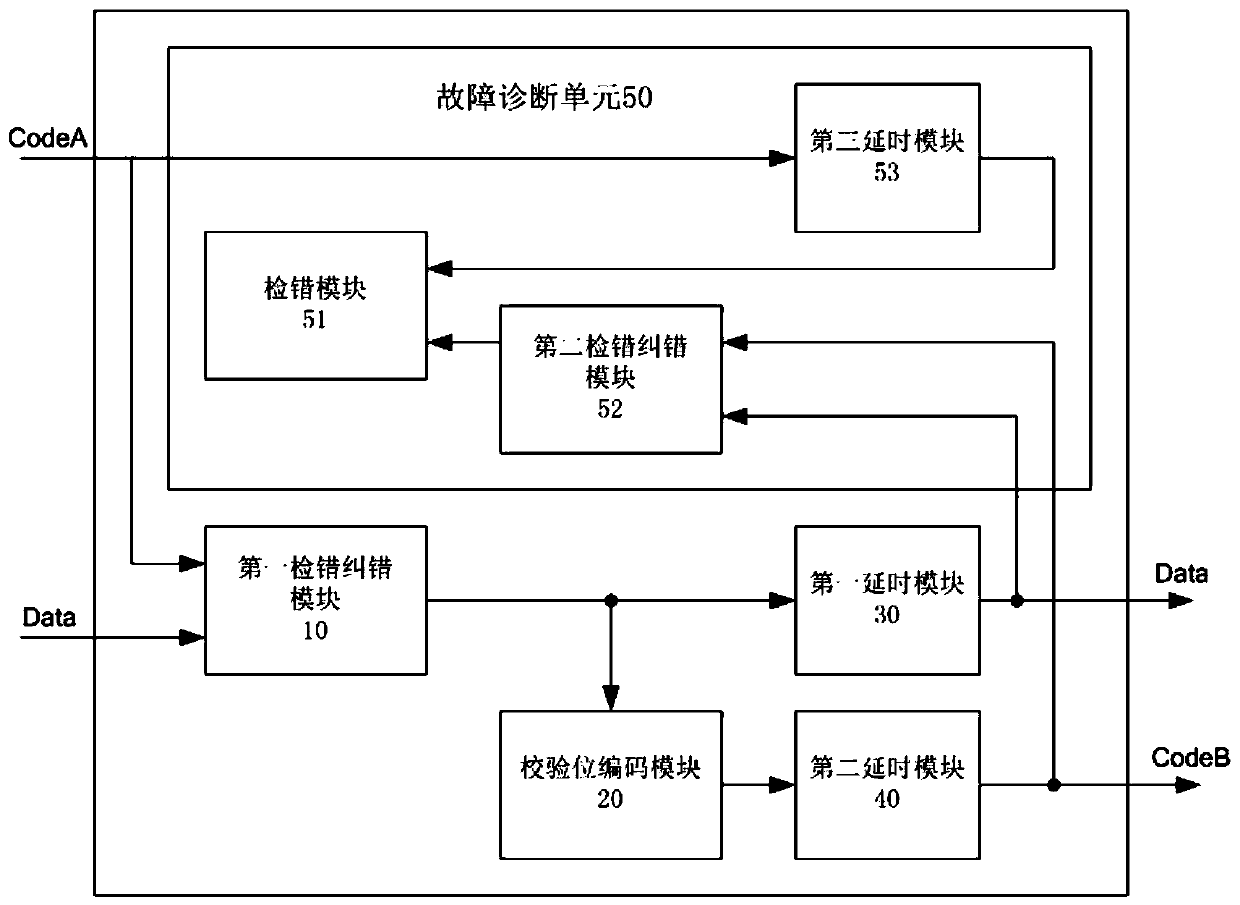

[0029] figure 1 It is a functional block diagram of the error-check bit protocol converter according to the present invention, as figure 1 As shown, the error check digit protocol converter of the present invention includes a first error detection and correction module 10, a check digit encoding module 20, a first delay module 30, a second delay module 40, and a fault diagnosis unit ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More