High-speed data architecture based on network-on-chip and data transmission method

A technology of high-speed data and architecture, applied in the direction of digital transmission system, transmission system, data exchange network, etc., can solve the problems of global clock synchronization difficulty, ADC sampling rate and resolution can not be improved at the same time, to improve clock synchronization accuracy , Improve data transmission speed, improve the effect of data sampling rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

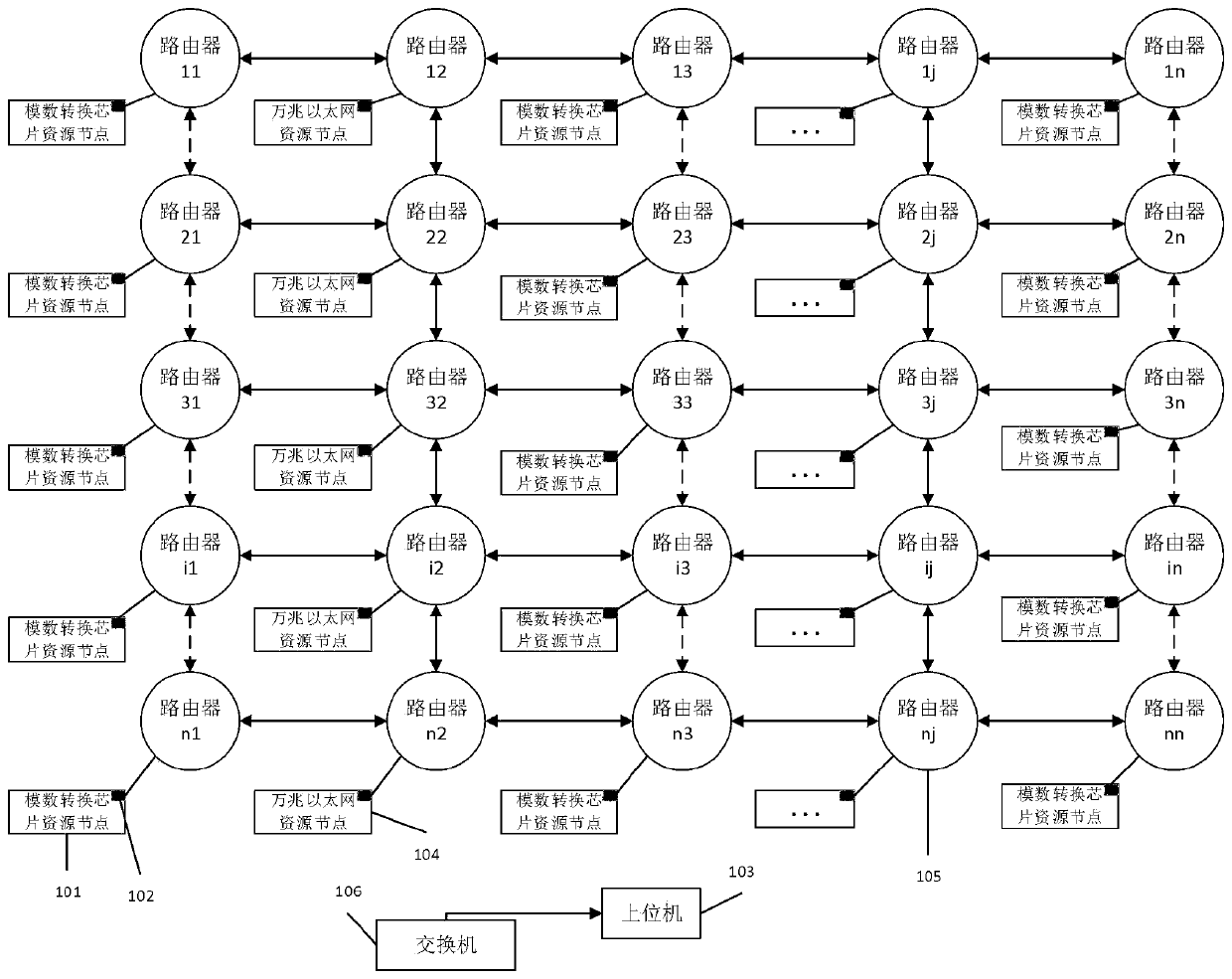

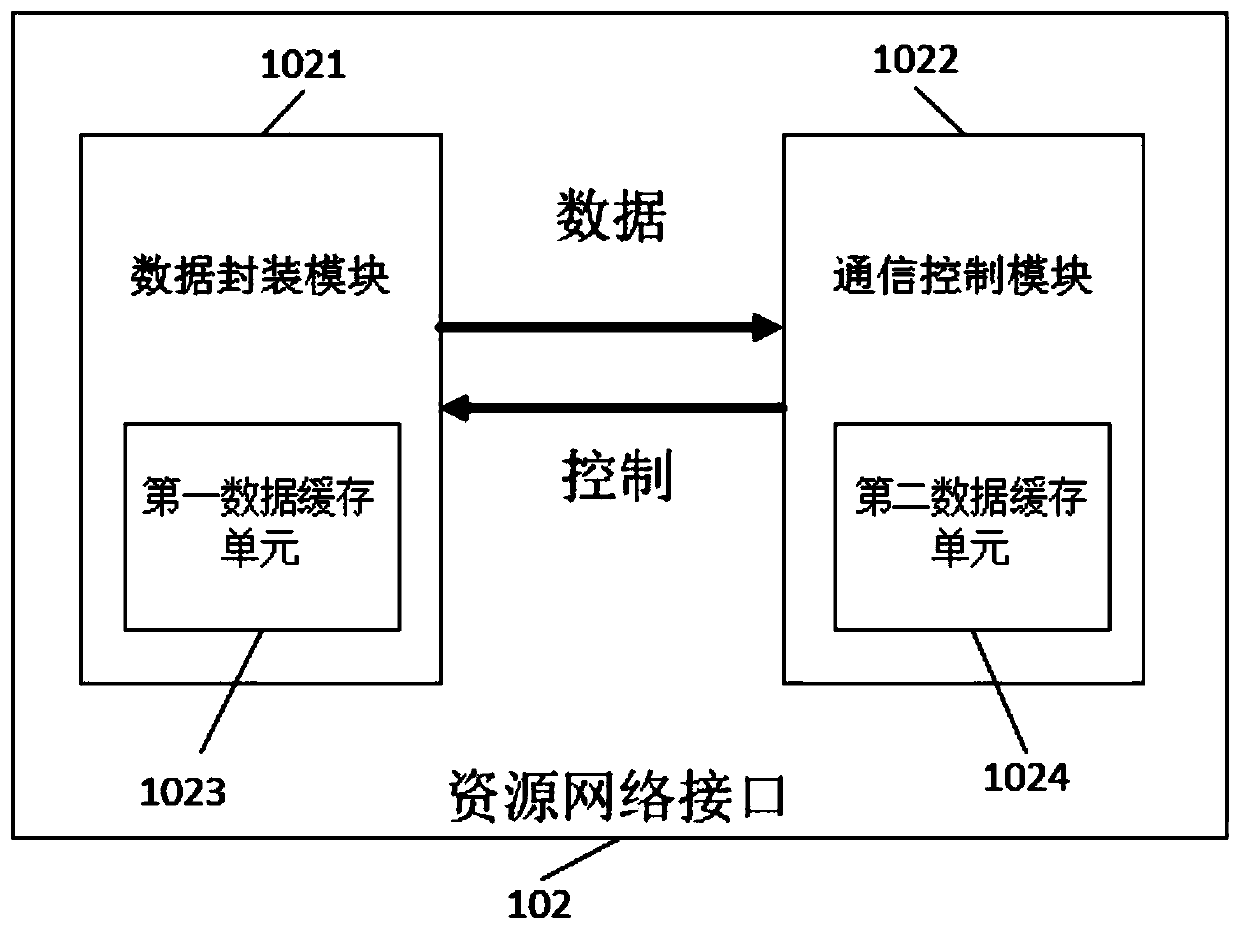

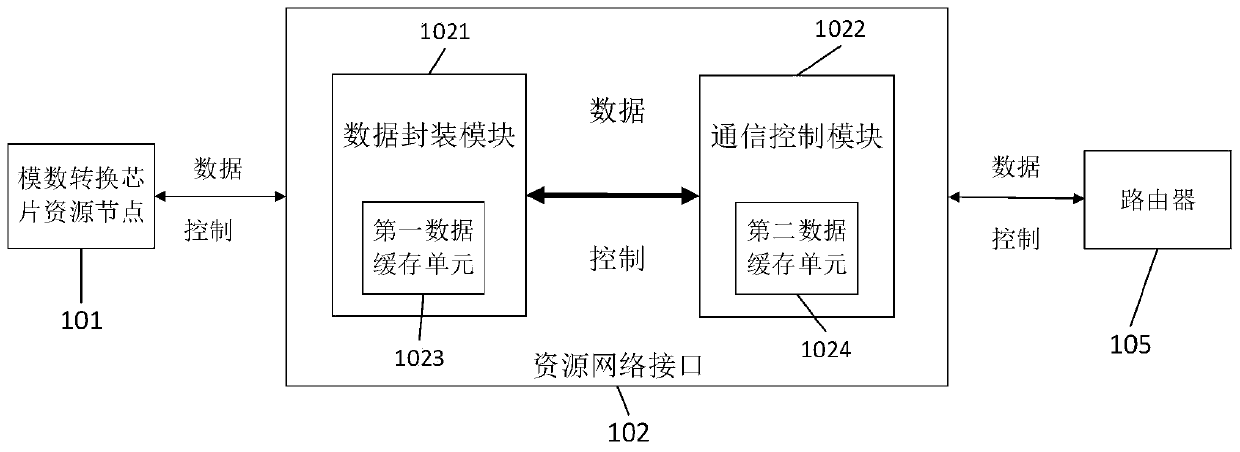

[0051] see figure 1 , is a schematic structural diagram of a network-on-chip-based high-speed data architecture provided by the present invention, including an analog-to-digital conversion chip resource node 101, a 10 Gigabit Ethernet resource node 104, a resource network interface 102, a router 105, and a switch 106. There are multiple routers 105 arranged in a matrix, the resource node and the resource network interface 102, the resource network interface 102 and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com