Input vector-oriented RTL-level circuit reliability calculation method

A calculation method and input vector technology, applied in the direction of calculation, electrical digital data processing, special data processing applications, etc., can solve problems such as fast and effective evaluation of reliability that is no longer applicable, and achieve the effect of ensuring high precision characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The present invention will be further described below in conjunction with the accompanying drawings.

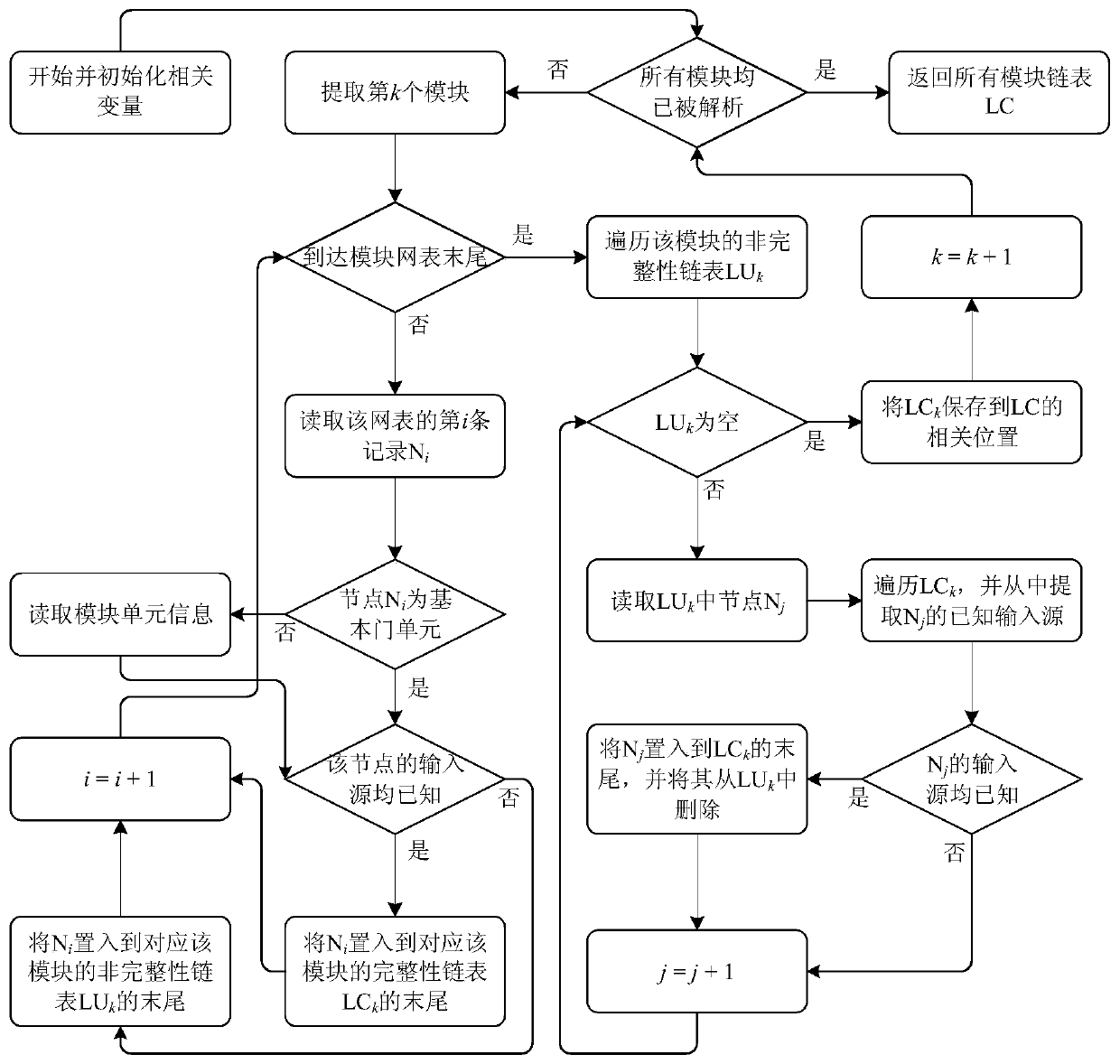

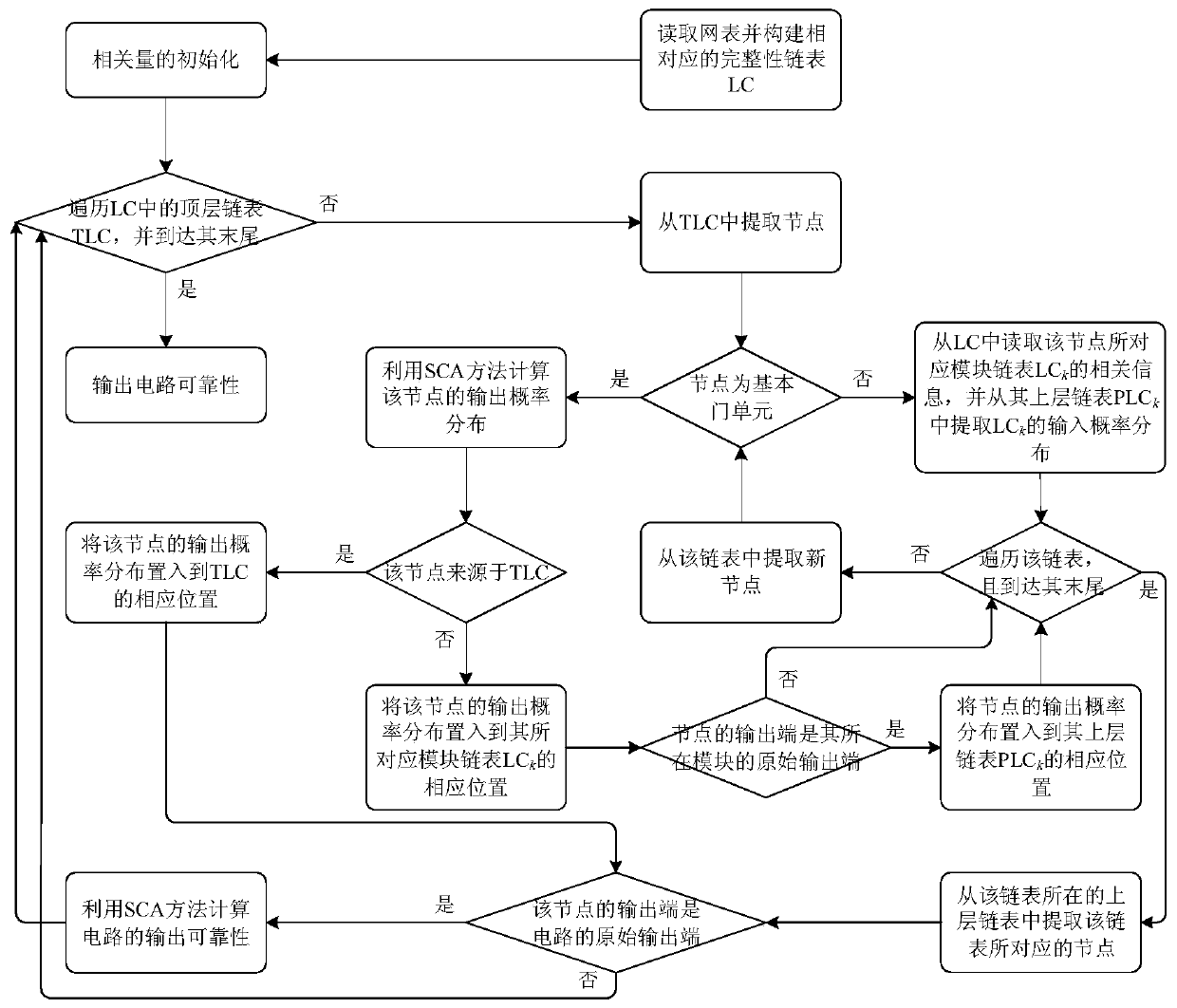

[0035] refer to figure 1 and figure 2 , an input vector-oriented RTL-level circuit reliability calculation method, comprising the following steps:

[0036] Step 1: Netlist analysis and initialization of related quantities, the process is as follows:

[0037] 1.1) Read the RTL-level circuit netlist and initialize the relevant variables;

[0038] 1.2) If all modules have been parsed, return the module linked list LC, and go to step 2; otherwise, extract the kth module of the circuit;

[0039] 1.3) If the end of the module netlist is reached, go to 1.7); otherwise, read the i-th record N of the netlist i ;

[0040] 1.4) If N i If it is a basic door unit, go to 1.5); otherwise, read the module unit information and go to 1.5);

[0041] 1.5) If the input sources of the node are known, then N i Put into the integrity linked list LC corresponding to the module k end ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More