Optimal design method for packaging high-speed signal via hole

A high-speed signal, optimized design technology, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of multi-dimensional parameter collaborative analysis that cannot be packaged, and does not consider the impact, so as to reduce return loss and improve overpass Hole impedance, effect of improving transmission characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The technical solution of the present invention will be further described and illustrated through specific embodiments below, so that the technical solution will be clearer and clearer. Those skilled in the art can easily understand other advantages and effects of the present invention from the contents disclosed in this specification. The present invention can also be implemented or applied through other different specific implementation modes, and various modifications or changes can be made to the details in this specification based on different viewpoints and applications without departing from the spirit of the present invention.

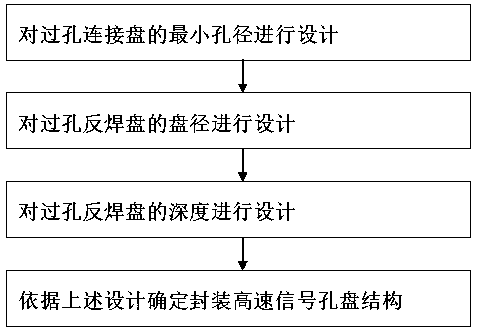

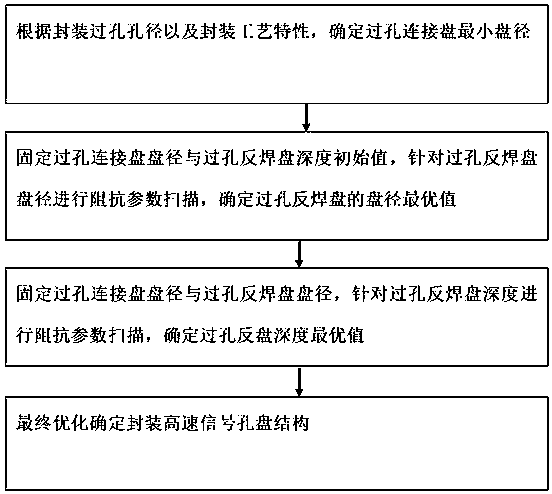

[0023] This embodiment relates to a method for optimizing the design of vias for packaging high-speed signals, such as figure 1 shown, including:

[0024] (1) Design the minimum aperture of the via land;

[0025] (2) Design the diameter of the via anti-pad;

[0026] (3) Design the depth of the via anti-pad;

[0027] (4) According to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More