Semiconductor structure and manufacturing process thereof

A manufacturing process and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., and can solve problems such as low trap density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0094] The semiconductor structure in this embodiment is a 3D NAND memory, and its specific manufacturing process includes:

[0095] providing a substrate 10 of monocrystalline silicon;

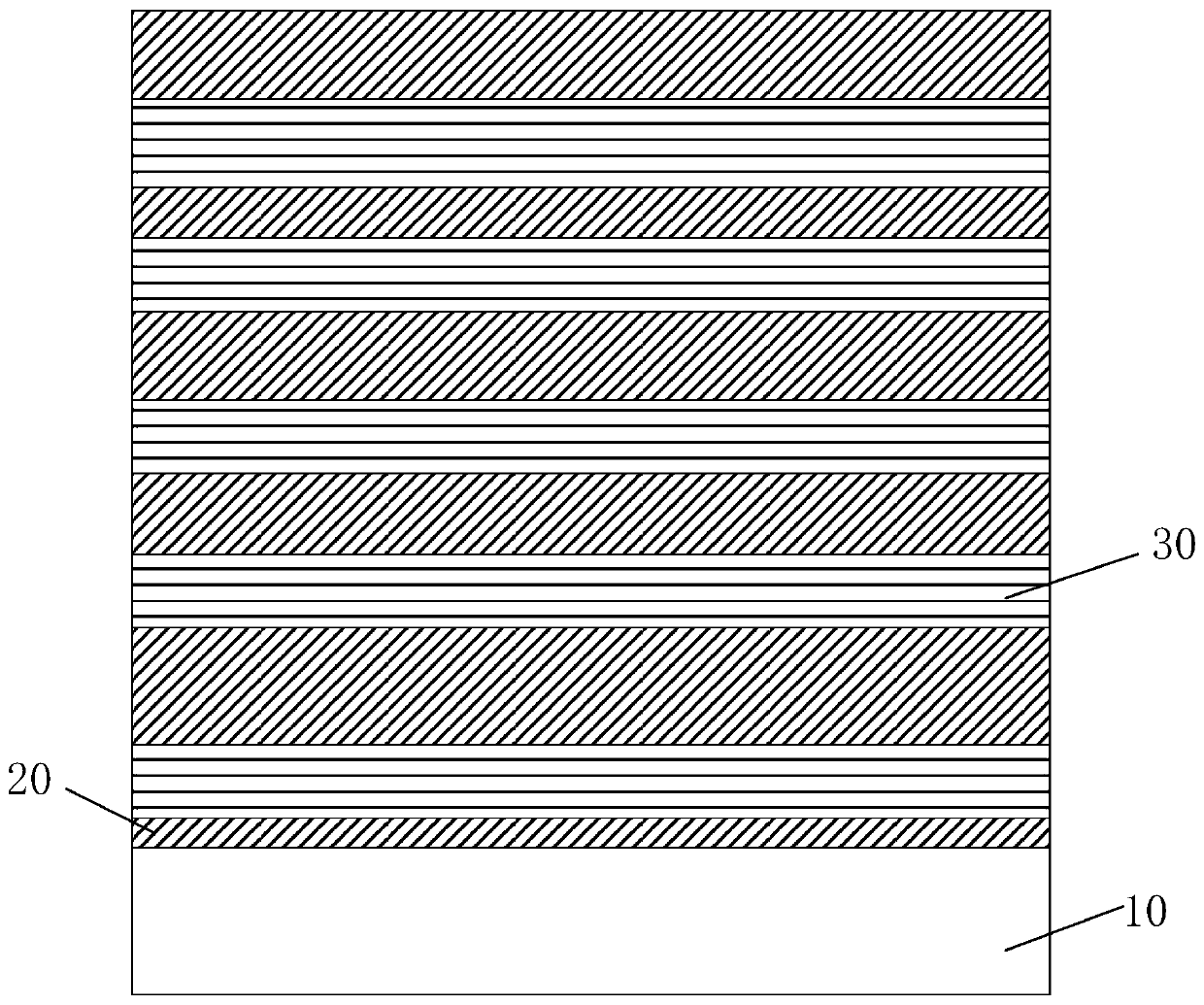

[0096] The first insulating dielectric layer 20 and the sacrificial layer 30 are alternately deposited on the substrate 10 to form a preliminary stack structure, thereby forming figure 1 In the shown structure, wherein the first insulating dielectric layer 20 is formed in contact with the substrate 10, the first insulating dielectric layer 20 is a silicon oxide layer, and the sacrificial layer 30 is a silicon nitride layer;

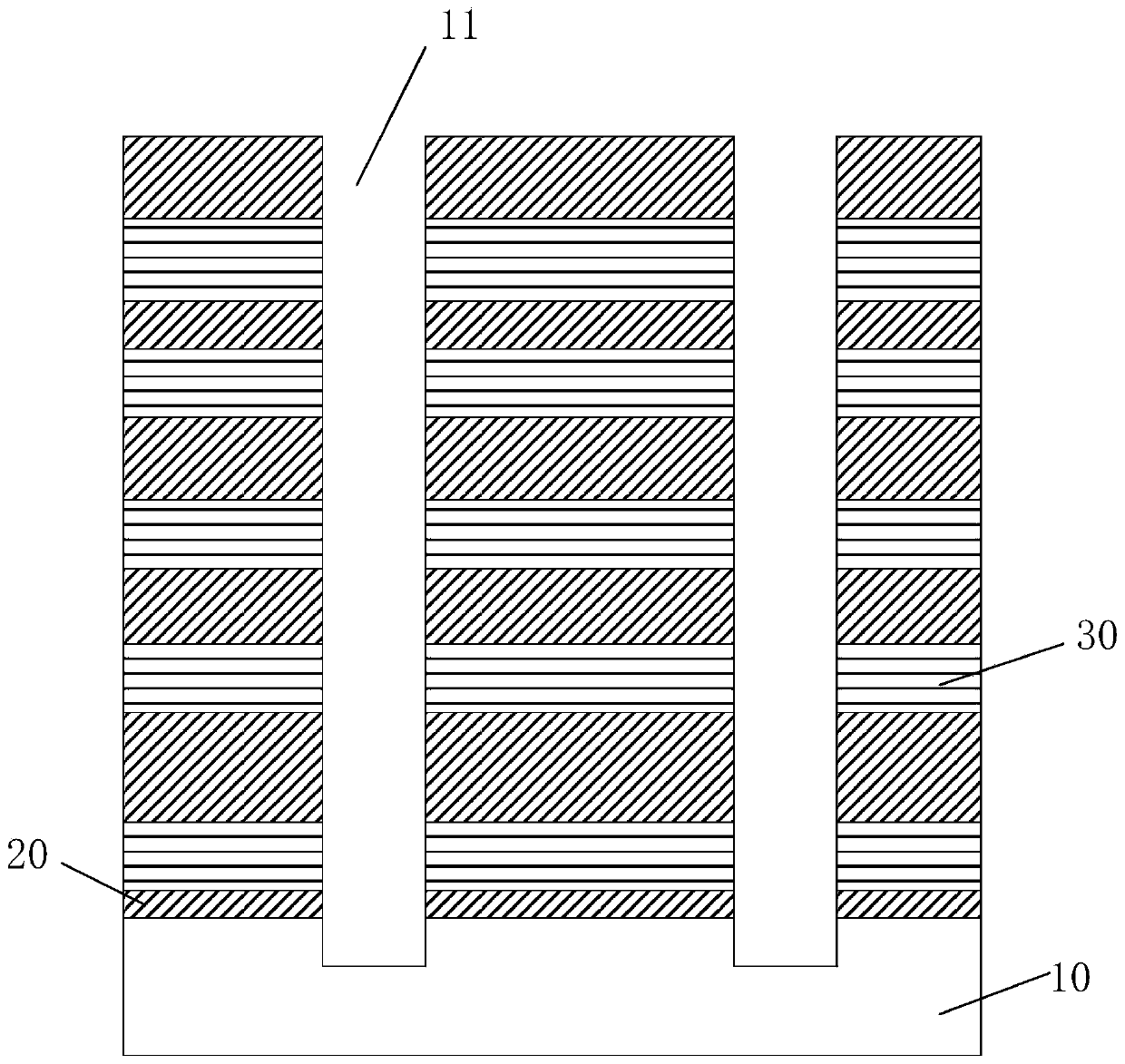

[0097] Etching and removing parts of each of the above-mentioned first insulating dielectric layers 20, parts of each of the above-mentioned sacrificial layers 30, and part of the above-mentioned substrate 10, so that part of the above-mentioned substrate 10 is exposed, forming the following: figure 2 channel hole 11 shown;

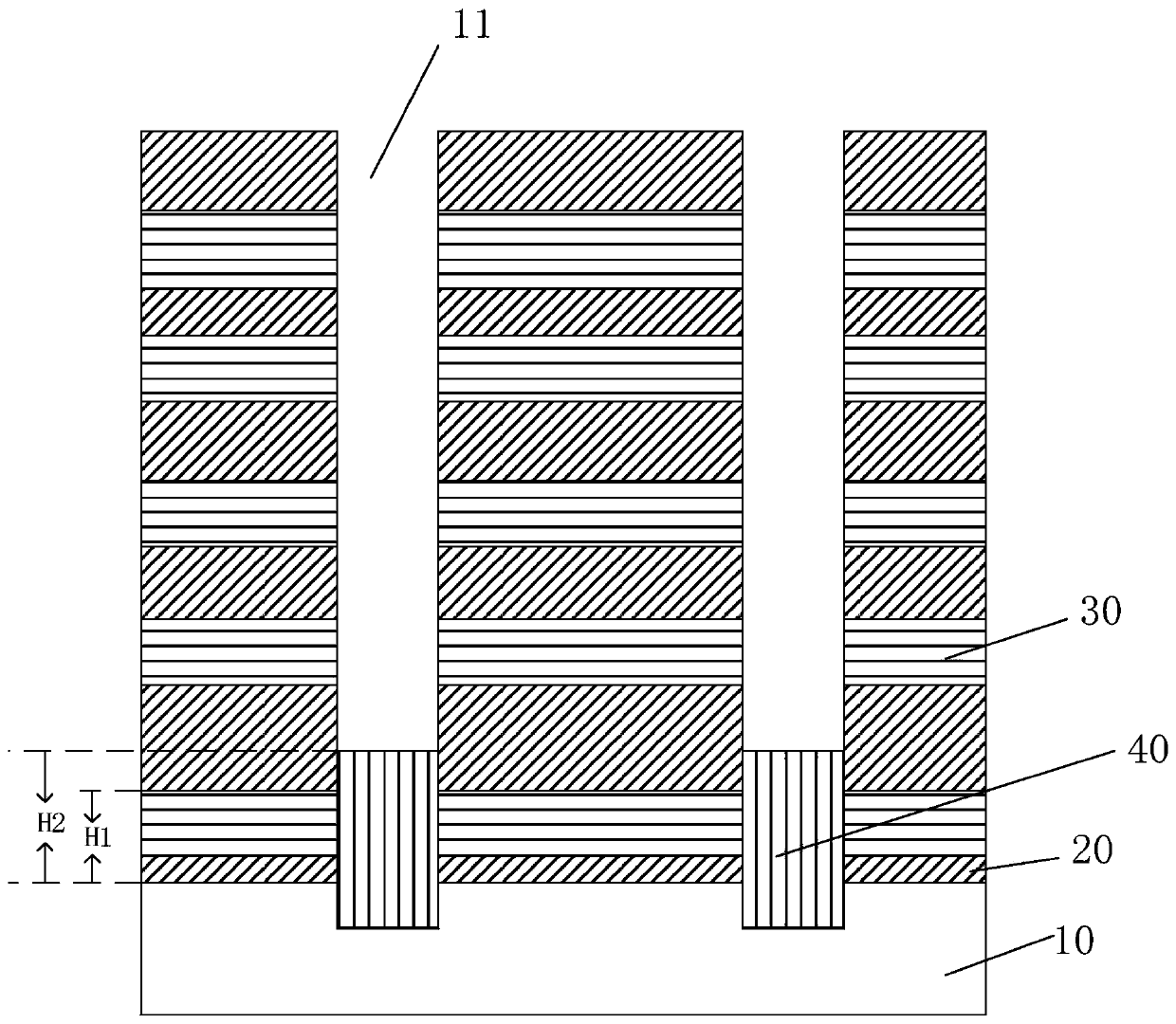

[0098]An epitaxial layer 40 of monocrystal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More