Controllable random fault injection method applied to simulation verification of processor chip

A technology of fault injection and simulation verification, applied in random number generators, electrical digital data processing, digital data processing components, etc., can solve the timing of uncontrollable errors, difficulty in finding design errors, scalability, and controllability and poor randomness to achieve the effect of improving reusability, improving efficiency and accuracy, and sufficient verification results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] Below in conjunction with specific embodiment, further illustrate the present invention. It should be understood that these examples are only used to illustrate the present invention and are not intended to limit the scope of the present invention. In addition, it should be understood that after reading the teachings of the present invention, those skilled in the art can make various changes or modifications to the present invention, and these equivalent forms also fall within the scope defined by the appended claims of the present application.

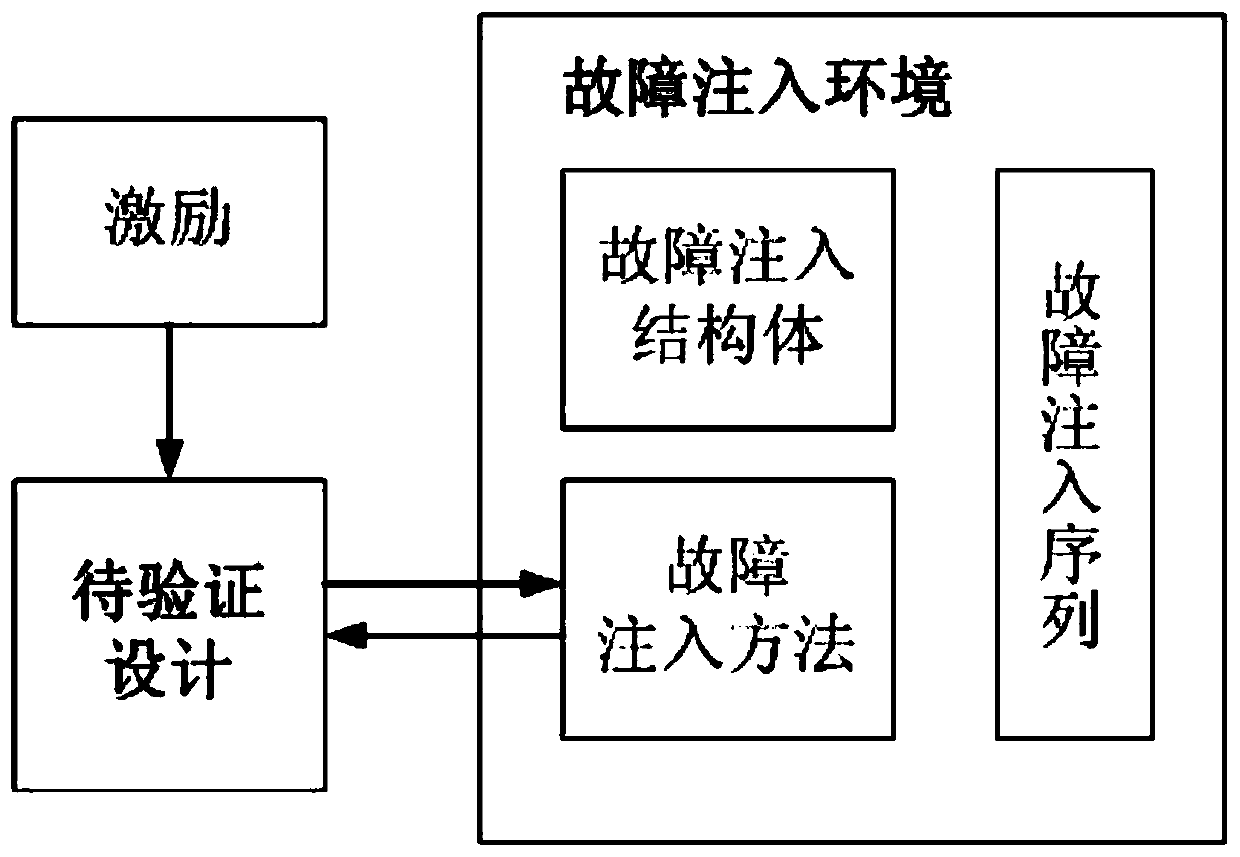

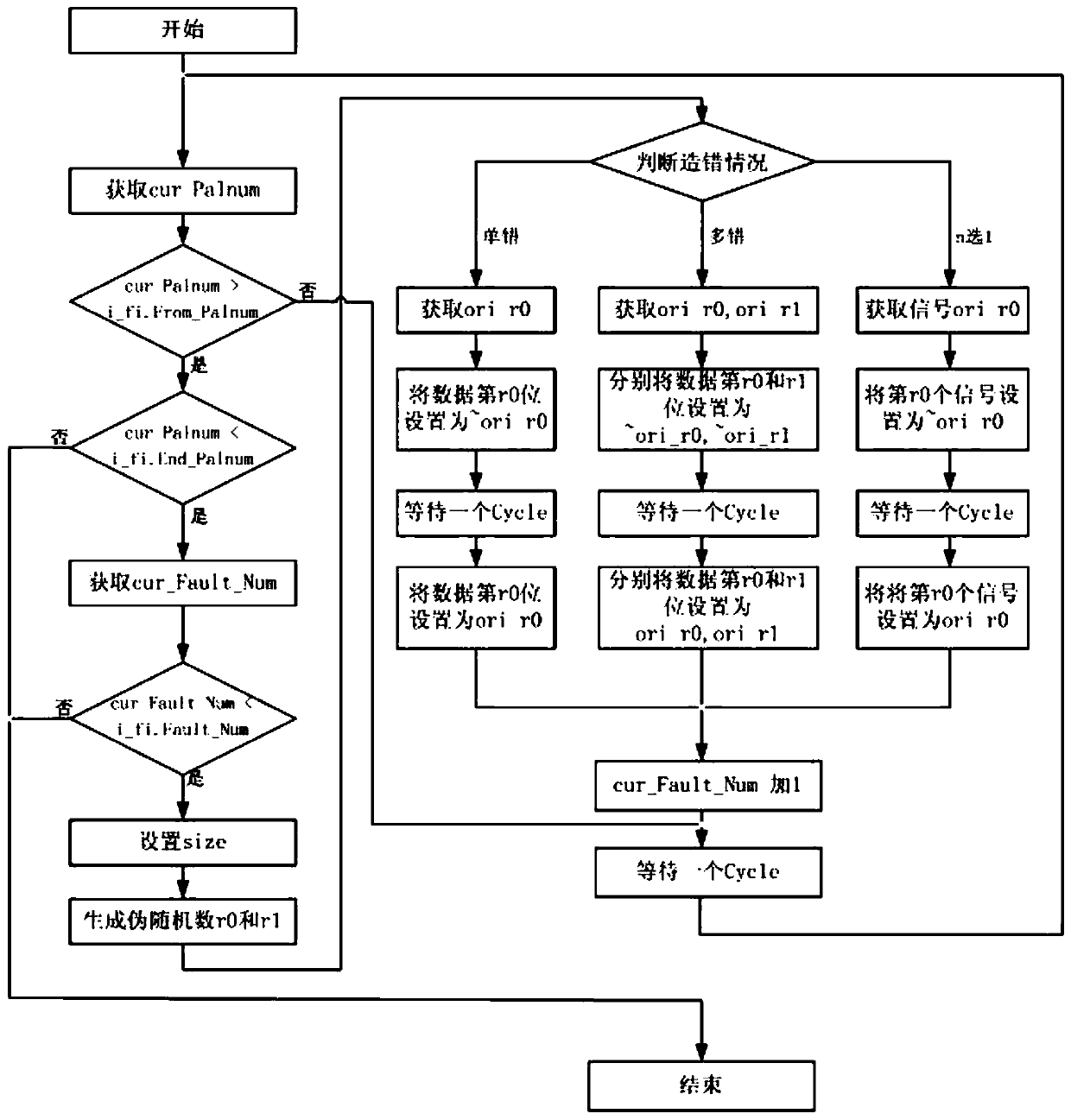

[0023] The embodiment of the present invention relates to a controllable random fault injection method applied to processor chip simulation verification, which specifically includes the following steps:

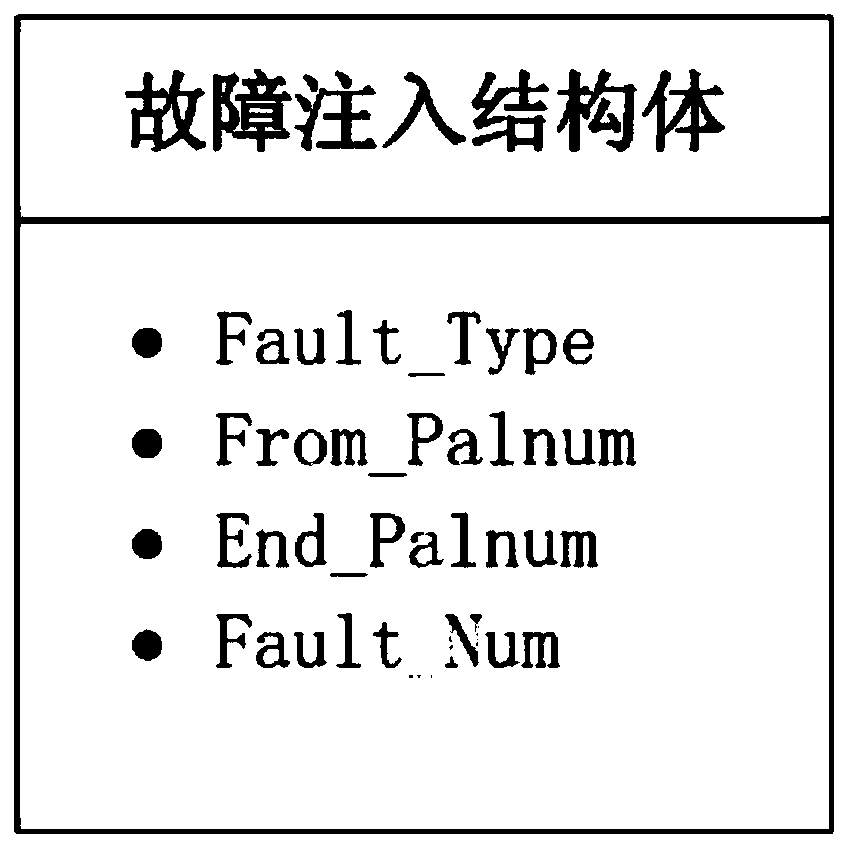

[0024] Step 1: Define the fault injection structure. The internal structure of the fault structure is as follows figure 1 As shown, the meaning of each internal variable is as follows:

[0025] 1) Fault_Type: Fault type, ind...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More