Time-interleaved ADC mismatch optimization method based on random truncation

A technology of time interleaving and optimization method, applied in the direction of analog/digital conversion calibration/test, analog-to-digital converter, electrical components, etc. The effect of improving spurious-free dynamic range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] Below in conjunction with accompanying drawing, further illustrate the present invention through embodiment.

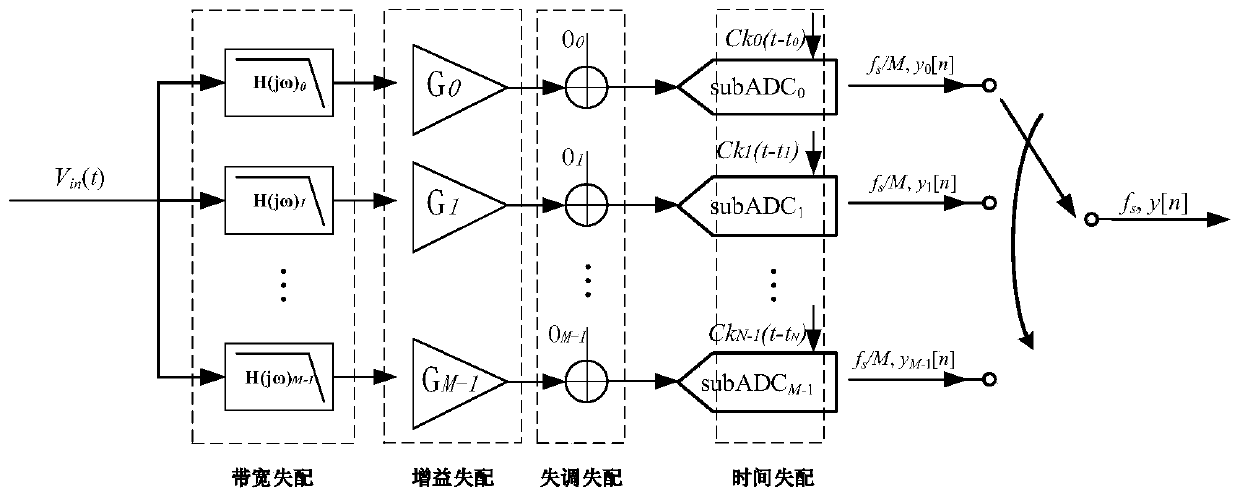

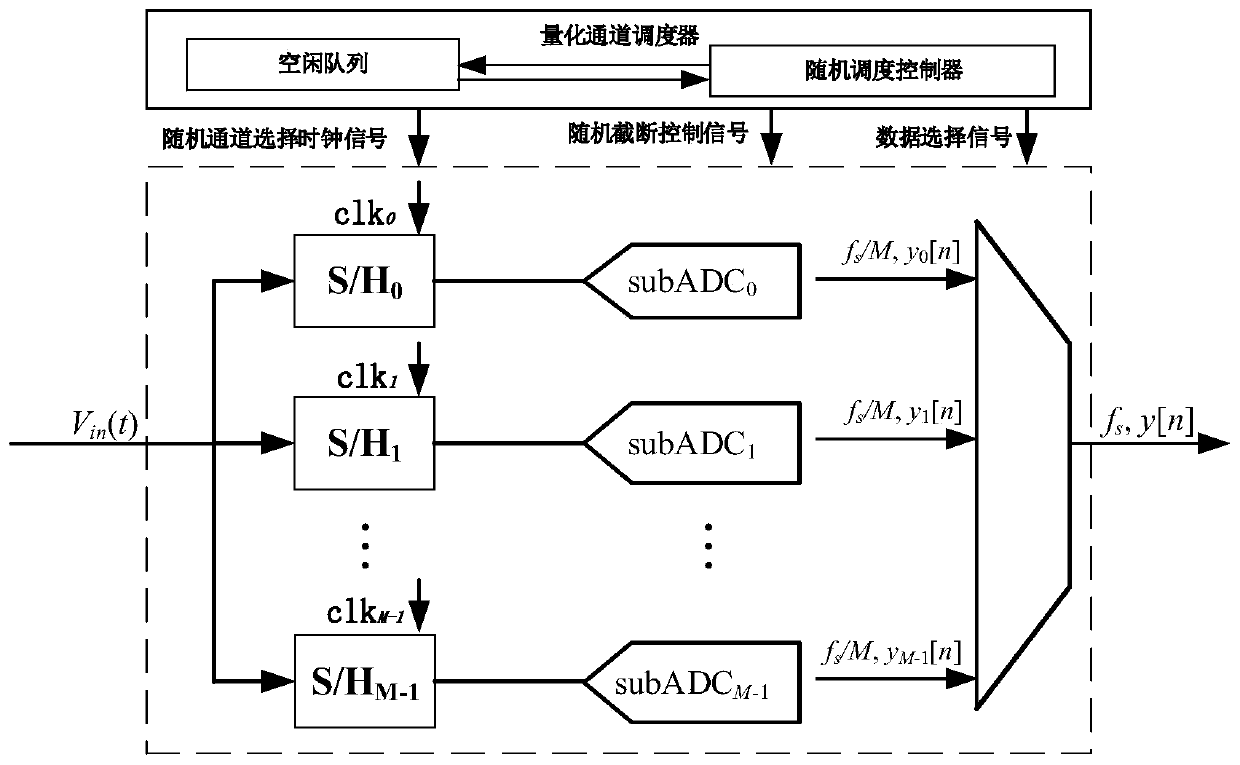

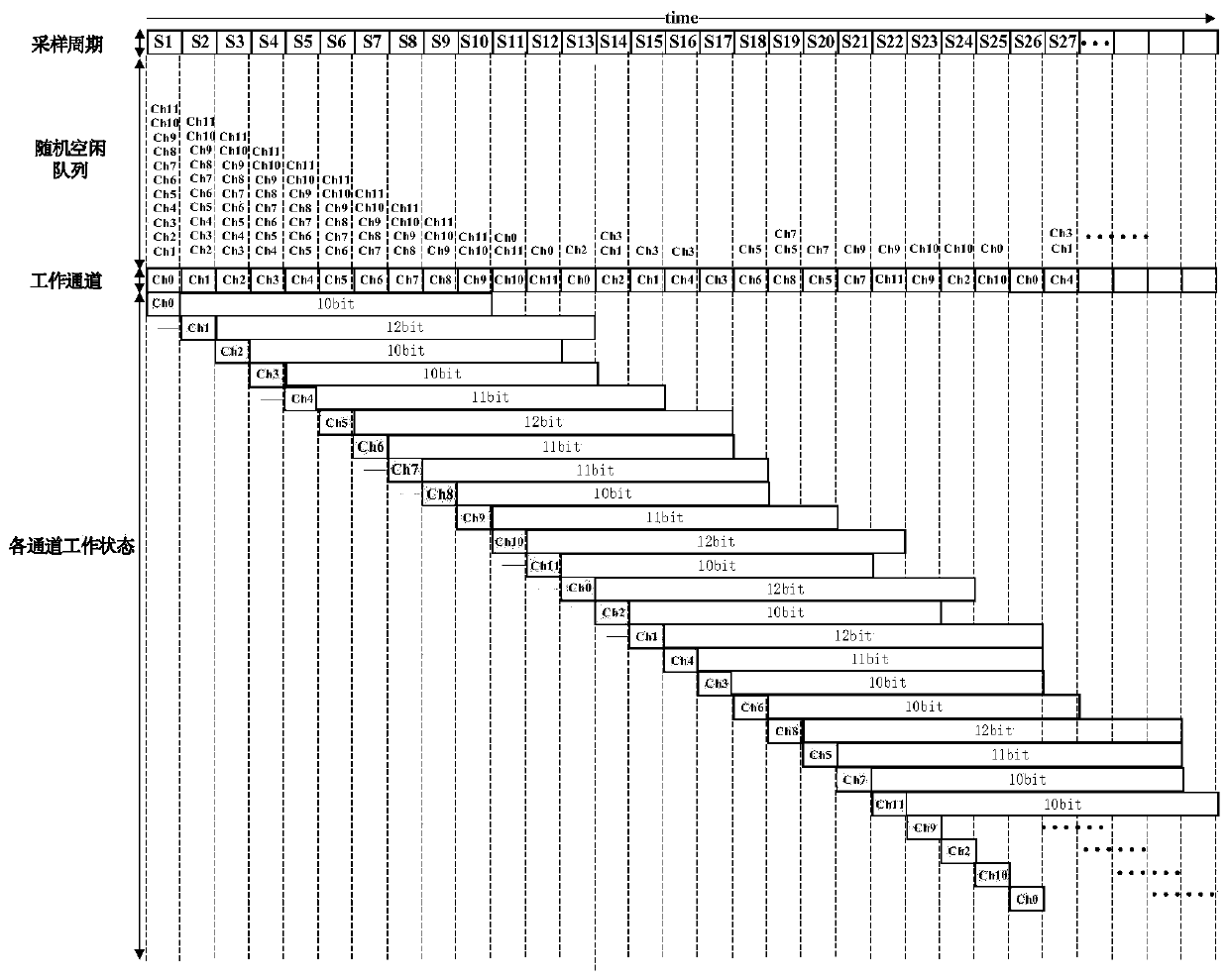

[0025] For the mismatch of the time-interleaved ADC, after being corrected by the correction technology, there are still residual mismatches, and these mismatches will have an increasingly serious impact on the performance of the time-interleaved ADC as the number of channels increases. Based on this, the present invention proposes a time-interleaved ADC mismatch optimization method based on random truncation. The time-interleaved ADC includes M sub-channels, M is a positive integer, and the precision of each sub-channel is N bits, and N is a positive integer. First, in the method proposed by the present invention, when a sampling and quantization period of the time-interleaved ADC starts, there are multiple sub-channels for selection in the idle queue, so that each channel can be randomly scheduled for quantization, thereby realizing random equalization optimiz...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More