Gallium nitride MOSFET packaging stress-strain distribution sensing structure

A technology for packaging stress and strain distribution, which is applied in the measurement of electric/magnetic solid deformation, the measurement of the property and force of applied piezoelectric resistance materials, and electromagnetic measurement devices. It can solve the problem that the structure of GaN MOSFET chips varies greatly and cannot be accurately Reflect the actual situation of the GaN MOSFET chip functional structure and the influence of electrical characteristics, etc., to achieve the effect of simple and easy detection method and process, simple and easy preparation process, and compatibility between preparation process and packaging process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

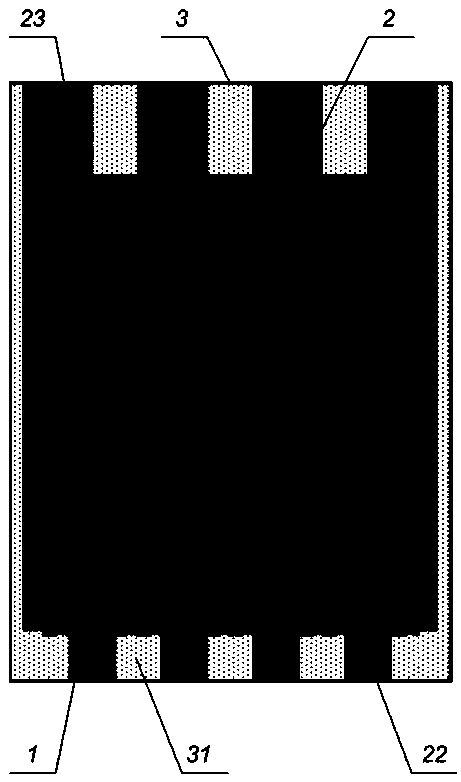

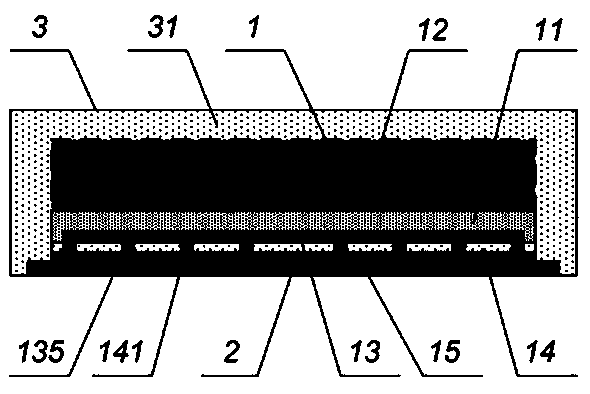

[0041] The present invention includes a chip 1, a lead frame 2, and an encapsulation layer 31 covering the chip and the lead frame,

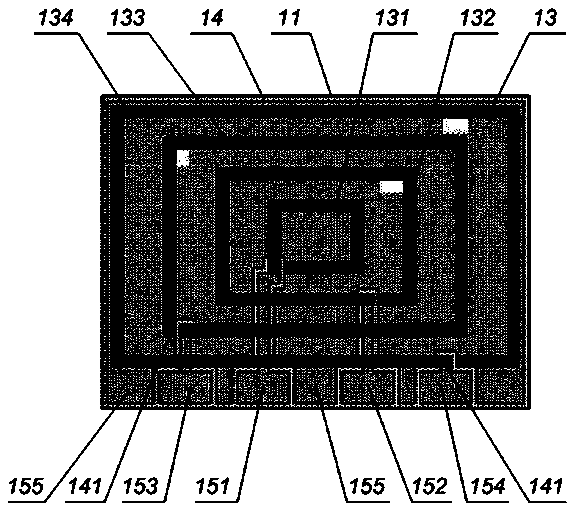

[0042] The chip includes a substrate 11, a gallium nitride MOSFET structure layer 12 fabricated on the substrate, a piezoresistor 13 fabricated on the bottom of the substrate, an insulating layer 14 covering the bottom surface of the substrate, and electrodes fabricated on the insulating layer layer 15,

[0043] The piezoresistor 13 includes at least two piezoresistive rings nested sequentially from the inside to the outside, wherein the odd-numbered piezoresistive rings have a gap one in the lower part, and the even-numbered piezoresistive rings have a gap two in the lower part. The gaps 1 and 2 are arranged in a staggered manner, and the horizontal spacing and the vertical spacing between adjacent piezoresistive rings ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More