FPGA-based SDIO interface test equipment and method

An interface test and equipment technology, applied in the field of SDIO interface test equipment, can solve the problems of high test cost, low flexibility, and inability to test, and achieve the effect of simplifying hardware design, increasing flexibility, and reducing test cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] FPGA-based SDIO interface test equipment of the present invention is to use FPGA to design an SDIO card based on SDIO3.0 agreement, and this SDIO card can customize the parameter of card (such as the maximum bit width supported, whether there is a memory function), This makes this universal SDIO card meet the test requirements. If it is necessary to add tests, it is only necessary to modify the software driver, such as reconfiguring parameters, and the hardware platform does not need to be redesigned.

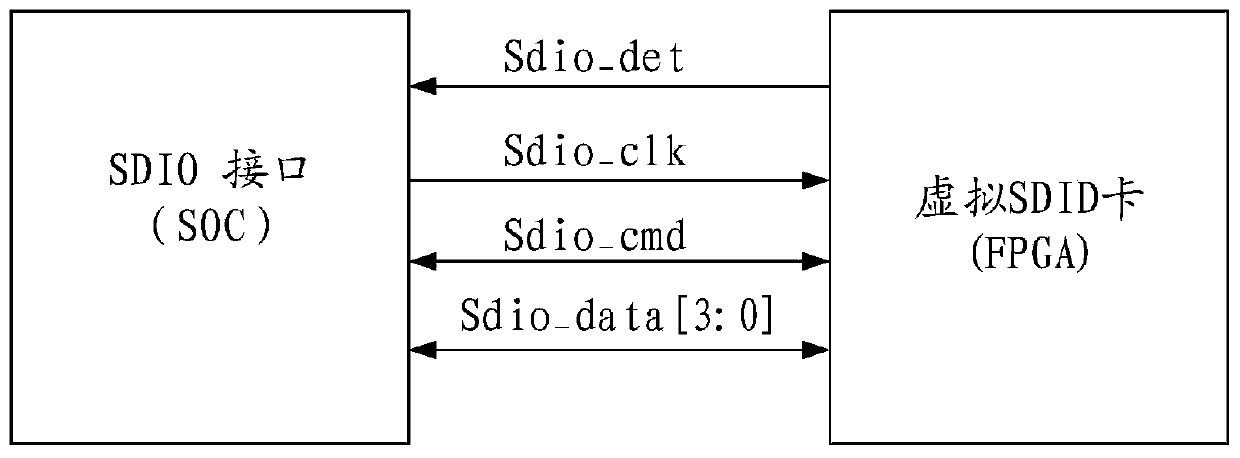

[0031] see figure 1 As shown, during the test, the SDIO card is connected to the SDIO interface of the SOC through corresponding pins; the pins include sdio_det, sdio_clk, sdio_cmd and sdio_data[3.0].

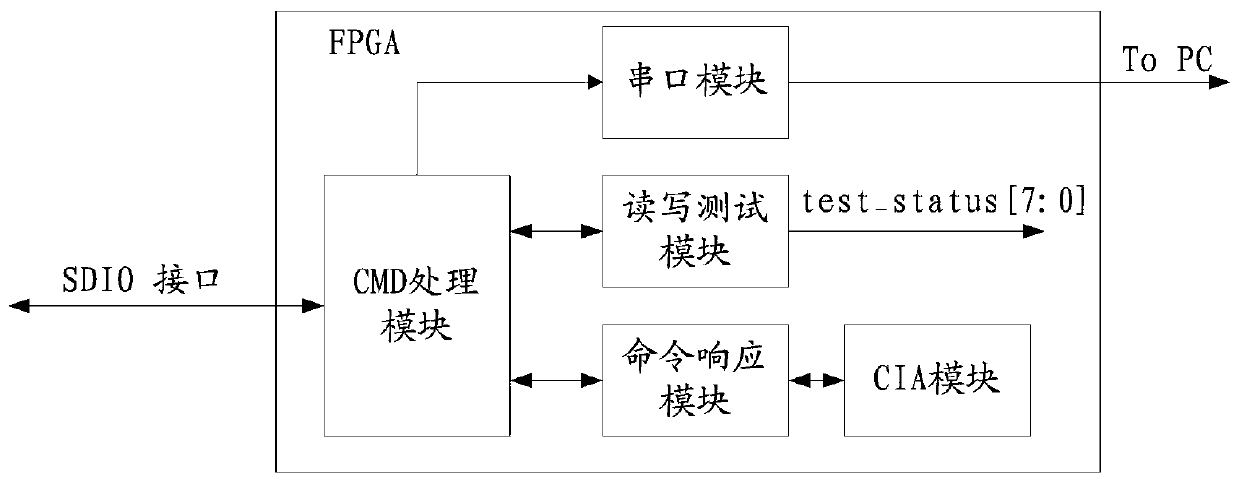

[0032] Another example figure 2 As shown, on the hardware structure, the SDIO card includes a CMD processing module, a CIA module, a command response module and a read-write test module, and the CMD processing module is connected to the order response module and the re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More