FPGA-based variable symbol sampling rate raised cosine filter

A raised cosine filter and sampling rate technology, applied in the field of filters, can solve the problems of fixed filter structure and inability to adapt to symbol sampling rate, etc., and achieve the effect of fast sampling speed and easy implementation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The technical solution of the present invention will be further described in detail below in conjunction with specific examples, but the protection scope of the present invention is not limited to the following description.

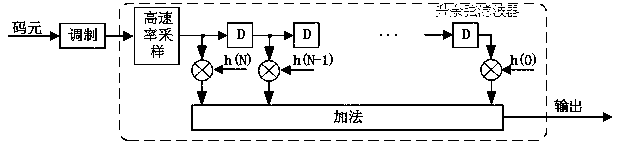

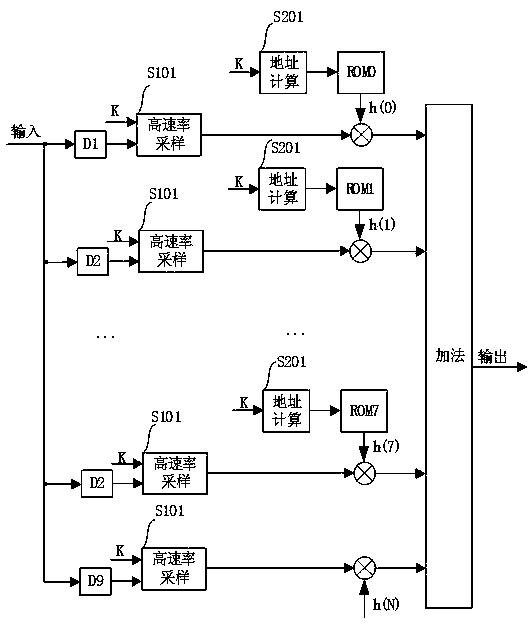

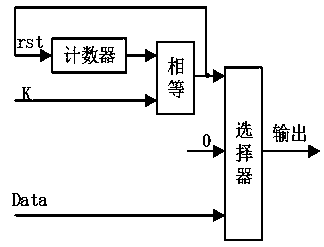

[0027] Such as figure 2 As shown, a variable symbol sampling rate raised cosine filter based on FPGA includes L+1 high-speed sampling modules S101 and L address calculation modules S201, and satisfies N=KL, where K is the number of sampling points for each symbol, L indicates that the filter truncation time length is L symbols, and the value of L is 4-8. The number of filter coefficients is N+1; L+1 high-speed sampling modules S101 are sequentially delayed by one clock cycle for sampling, and the output terminals of L+1 high-speed sampling modules S101 are each connected to the input terminal of a multiplier, and L+1 The output terminals of the multipliers are connected to the same adder, and the adder will add the L+1 road signals input in paral...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More