FPGA-based multi-encoder protocol free conversion IP core and method

A technology of encoders and protocols, applied in the field of free conversion of IP cores of various encoder protocols, to achieve the effects of wide application range, high synchronization, and high integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

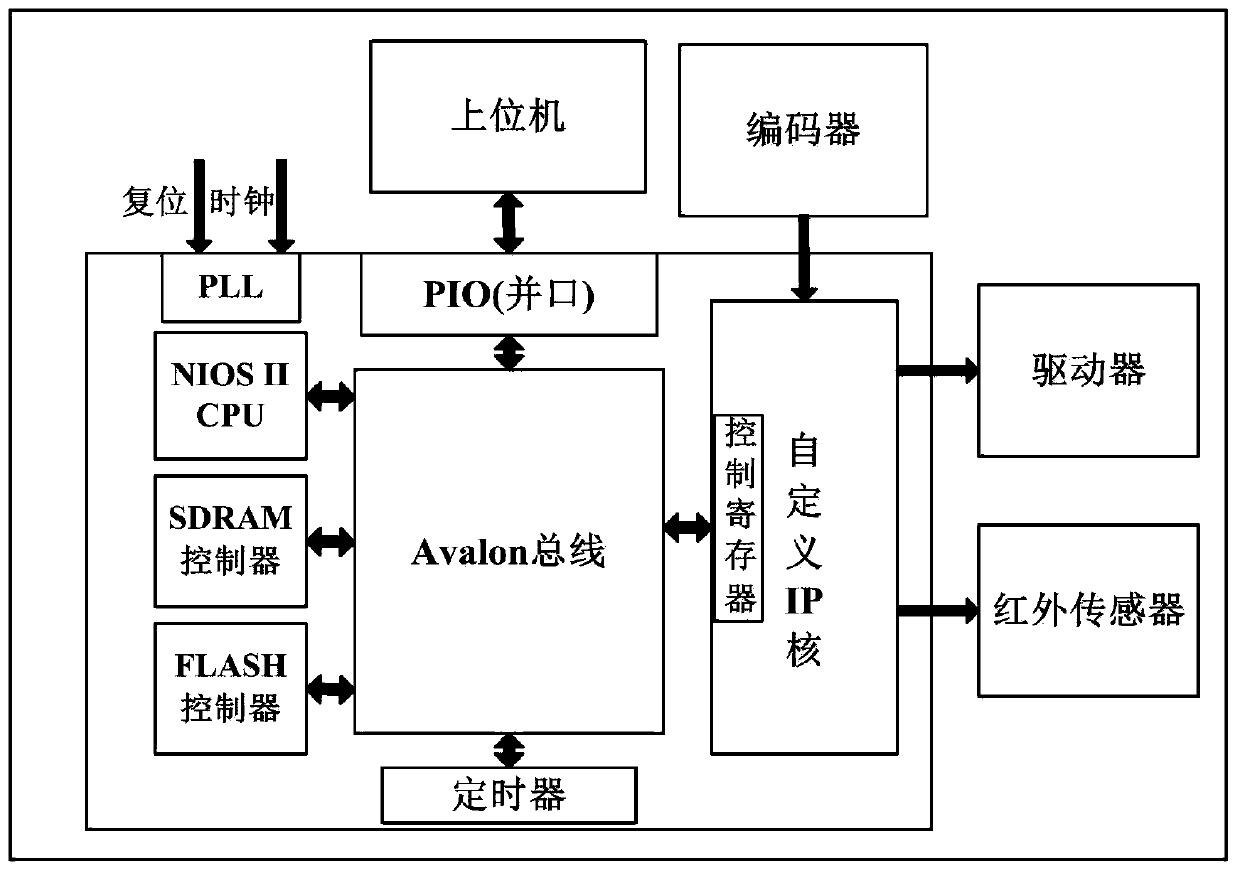

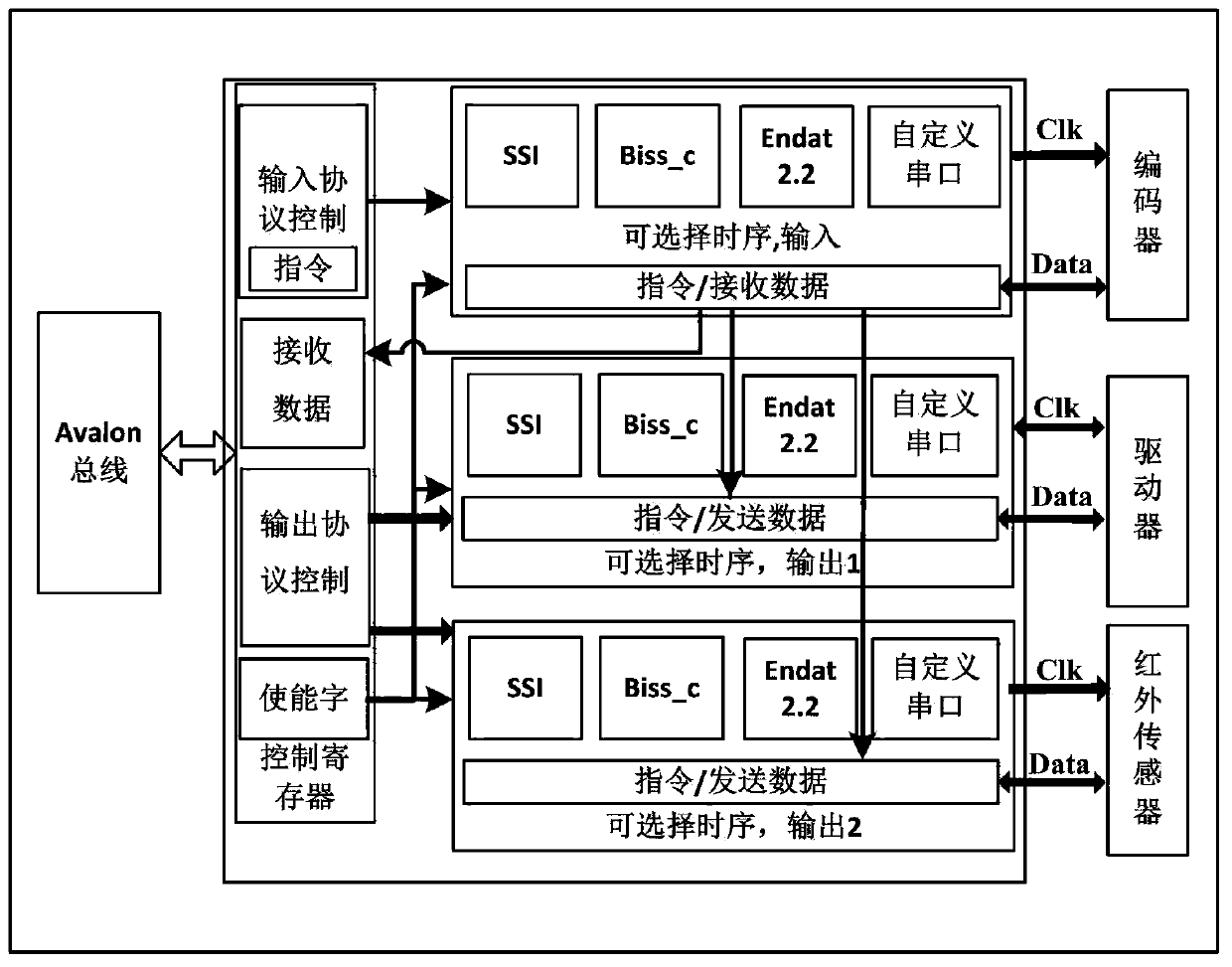

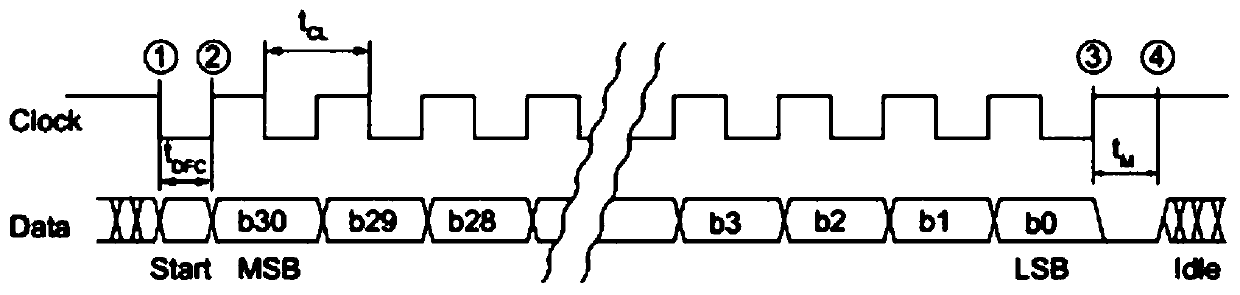

[0054] see figure 1 As shown, the embodiment of the present invention provides an FPGA-based IP core for free conversion of various encoder protocols, including: a basic IP core module, a peripheral IP core module, and a custom IP core module connected to each other through the Avalon bus.

[0055] Among them, the peripheral IP core module is used to obtain the control word written by the host computer. The basic IP core module is used to configure the control register of the self-defined IP core module according to the control word, so as to realize the selection of the input and output protocols, thereby enabling the corresponding state machine. Specifically, when the basic IP core module configures the control registers of the custom IP core module, the configuration information includes the input protocol selection (including baud rate settings, information digits, and command settings) enabling signals; the output protocol selection (including baud rate setting, bit sett...

Embodiment 2

[0077] Based on the same inventive concept, an embodiment of the present invention also provides a method for free conversion of multiple encoder protocols based on the above-mentioned IP core, and the method includes the following steps:

[0078] A. The peripheral IP core module obtains the control word written by the host computer; in actual operation, the content of the control word can include the number of input and output ports, protocol selection, baud rate selection, serial port enable, serial port command word settings, etc.

[0079] B. The basic IP core module configures the control register of the self-defined IP core module according to the acquired control word, realizes the selection of input and output protocols, and enables the corresponding state machine.

[0080] C. The custom IP core module performs encoder data acquisition, protocol conversion and output data to the corresponding destination machine; and the data acquisition and data output process are all g...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com