A Requirement Modeling and Verification Method for Hardware Logic Design

A technology of hardware logic and verification method, applied in the direction of CAD circuit design, etc., can solve problems such as inability to verify, achieve the effect of inspection accuracy, clear logic, and shorten the circuit design cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The specific embodiments of the present invention will be described in detail below with reference to the accompanying drawings. The described embodiments are only some of the embodiments of the present invention, but not all of the embodiments.

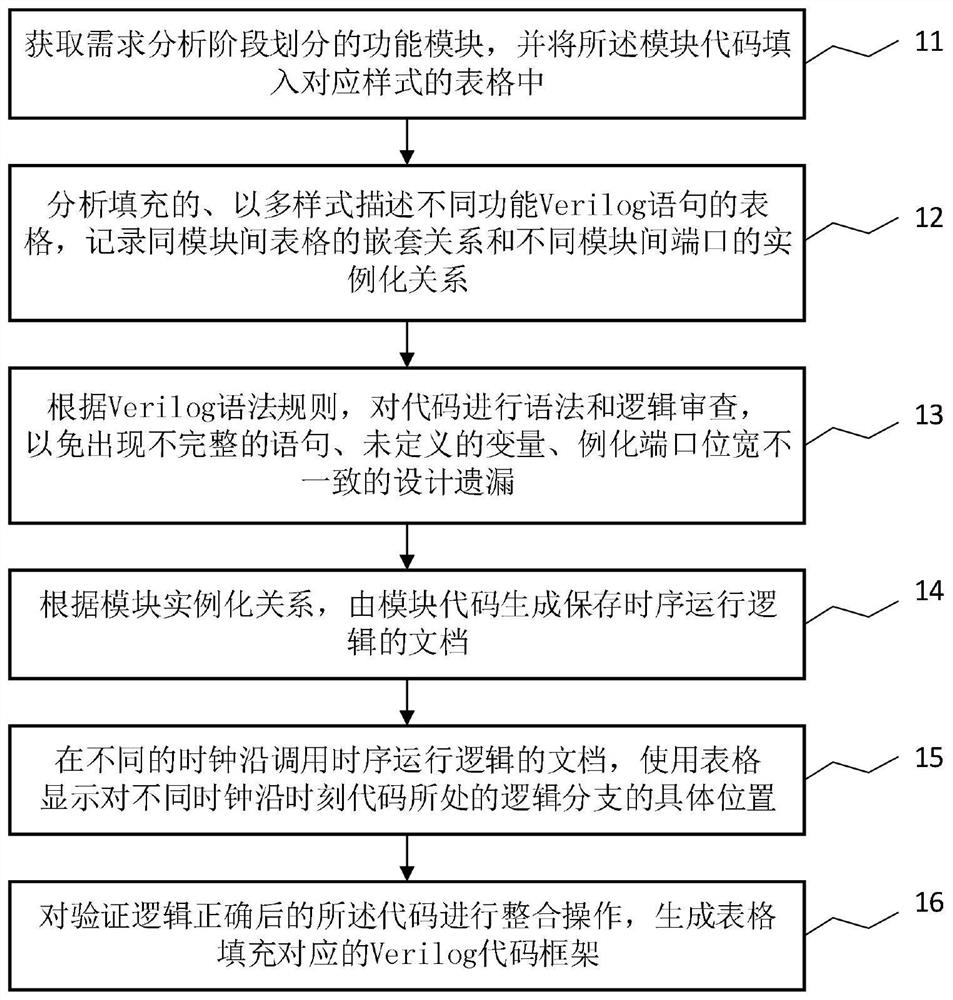

[0035] A requirement modeling and verification method for hardware logic design, such as figure 1 The detailed implementation steps are as follows:

[0036] 11. Obtain the functional modules divided in the requirement analysis stage, and fill in the module codes into the corresponding style table. This embodiment is a design of a serial communication controller, and the functional module is composed of three modules: a top module, a receiving module and a sending module.

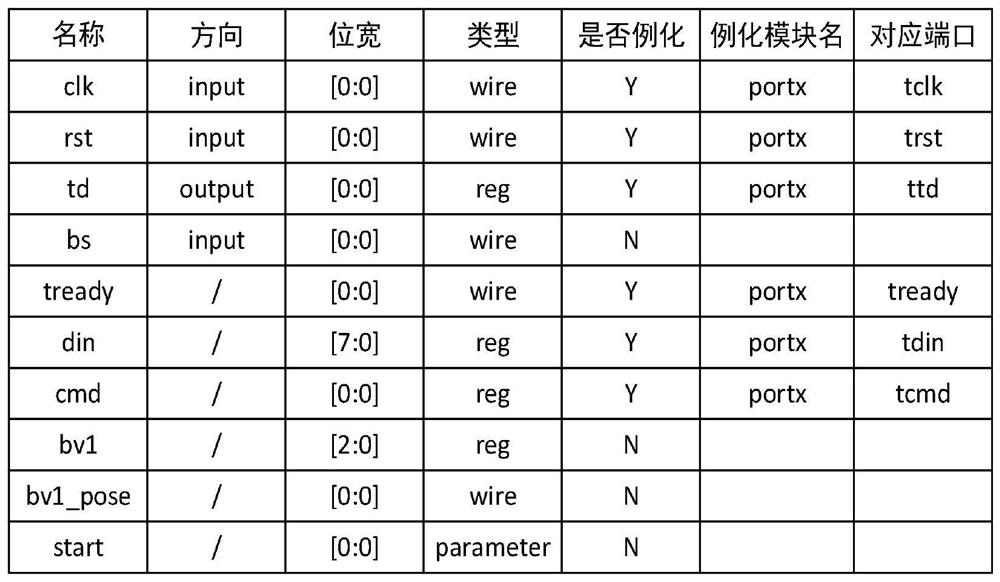

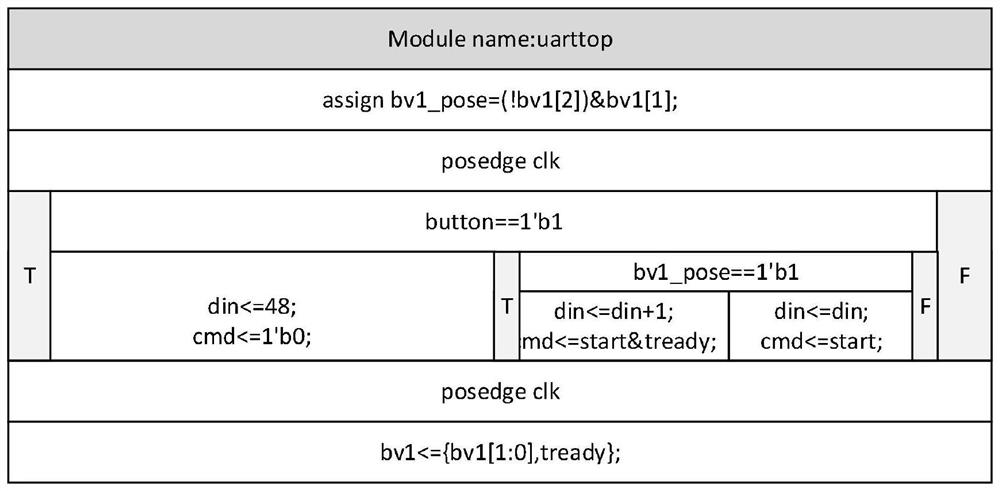

[0037] 12. Analyze the filled tables that describe different functional Verilog HDL statements in multiple styles, and record the nesting relationship between tables in the same module and the instantiation relationship between ports between different modu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More