Forward error correction decoding decoder based on burst error detection

A forward error correction and burst error technology, applied in the field of forward error correction decoder architecture, can solve the problems of low decoding efficiency, low throughput rate, waste of hardware resources, etc., so as to shorten the decoding time and improve the throughput. rate, the effect of shortening the delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] A four-degree parallel forward error correction decoder (RS-FEC) architecture for the RS decoding algorithm-mCS-RiBM algorithm. The improvements include the following aspects:

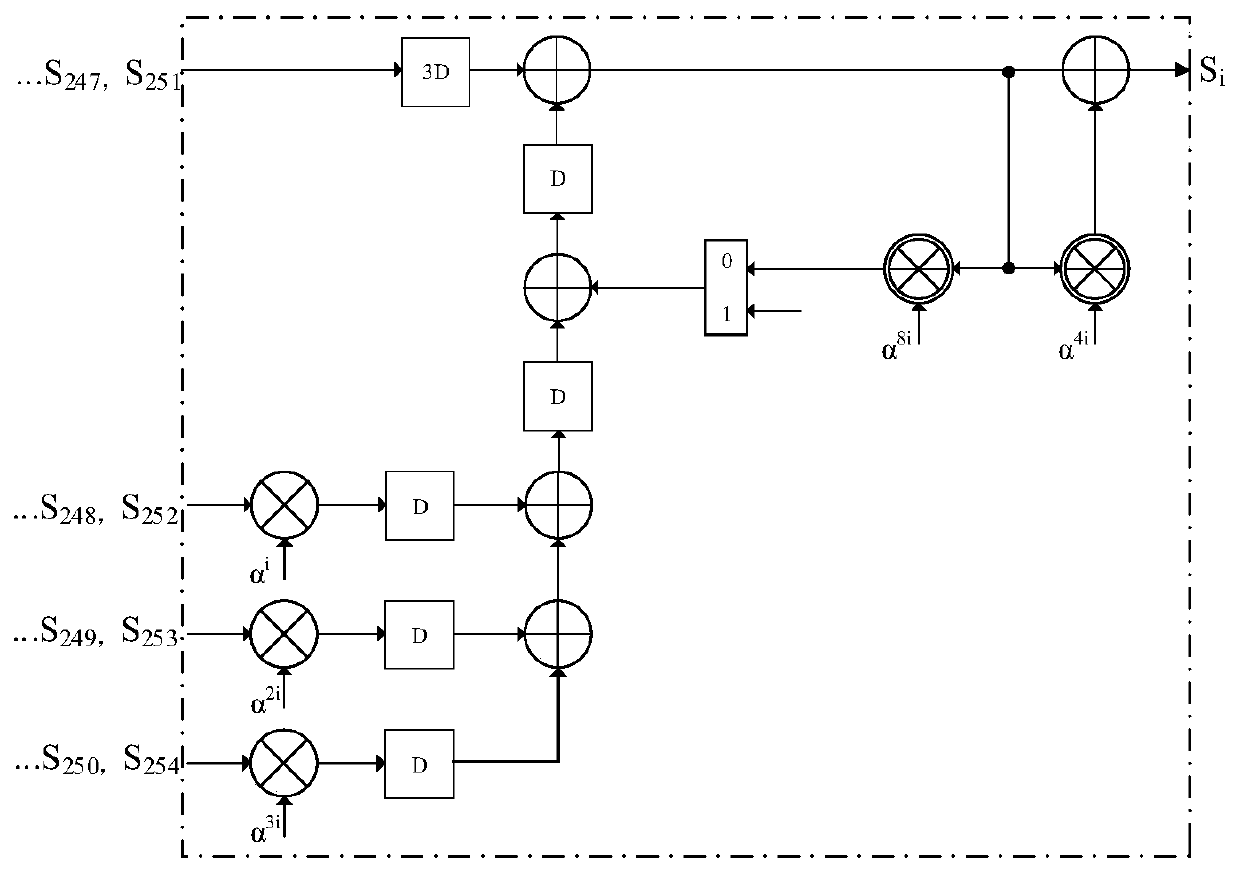

[0026] (1) The function of the SC module is implemented using a parallel structure. From the perspective of reducing the critical path, the syndromes are divided into odd parts and even parts to be calculated separately, and finally summed to calculate 2t syndromes. The parallelism factor of the syndrome calculation circuit is 4, and the symbols of each channel are input in order from high to low. In one clock cycle, the syndrome calculation module processes 4 symbols at the same time. After n / 4 After the clock cycle, the calculated syndrome is sent to the KES module;

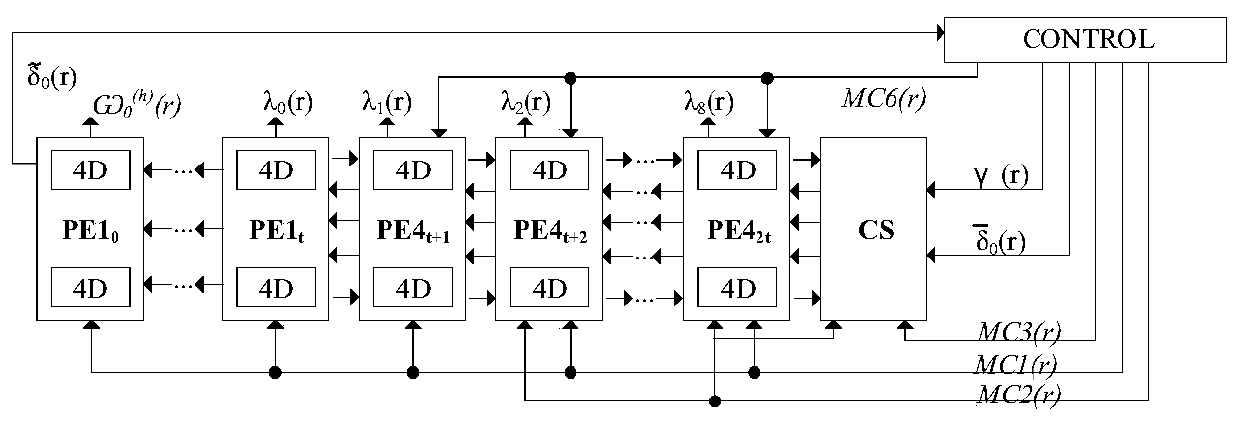

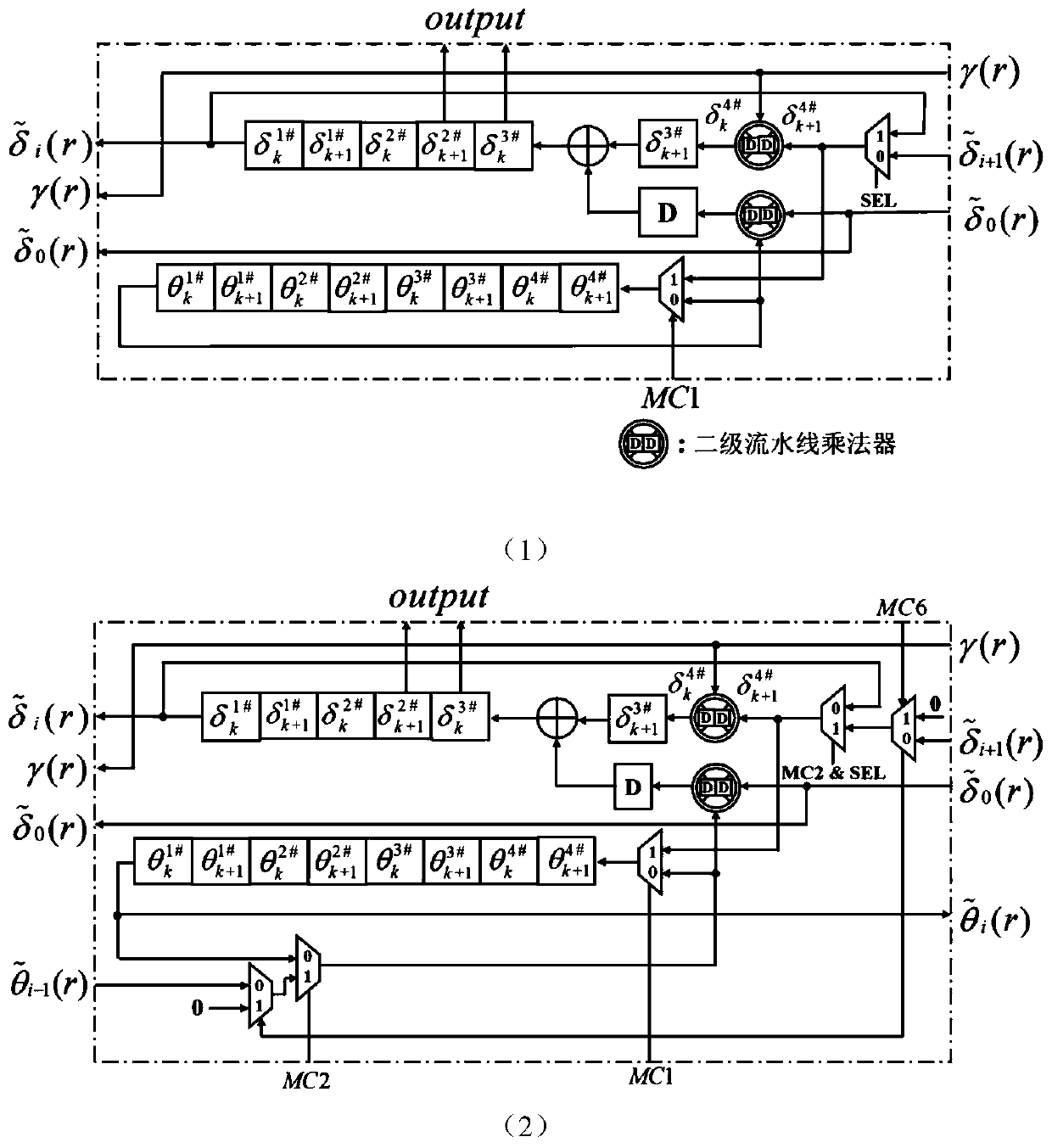

[0027] (2) Since the number of channels of the sub-decoder is 4, it is necessary to increase the 1 pair of registers of each processing unit in the original KES module to 4 pairs. Ordinary multipliers are replaced with pipeline ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More