A method and system for generating SPWM wave by using FPGA

A technology for generating modules and sine waves, which is applied in the direction of output power conversion devices, electrical components, single-network parallel feeding arrangements, etc., and can solve problems such as obvious hysteresis effect, insufficient response, and tediousness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

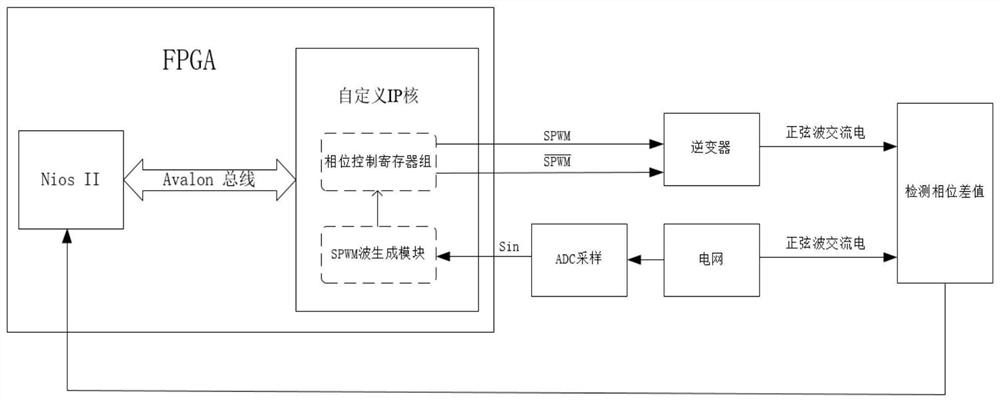

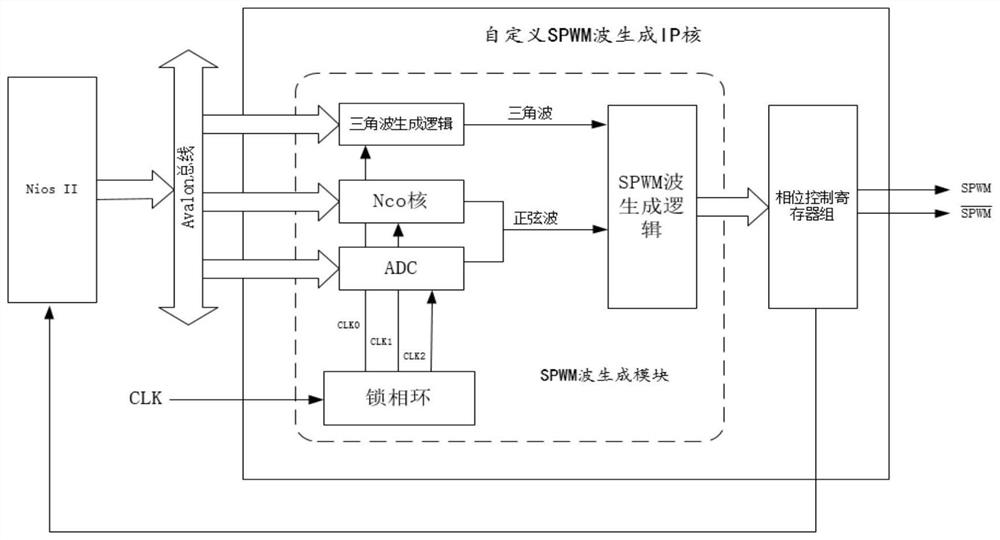

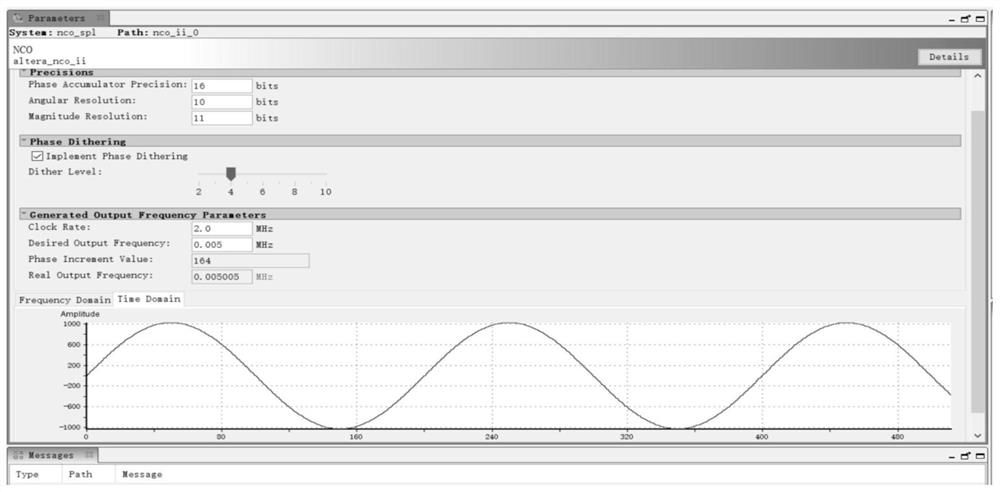

[0043] Such as figure 1 Shown in the overall framework of the system, the self-defining IP core of the present invention is a kind of IP core with Avalon bus, which can be easily attached to the NiosII processor, allowing the NiosII soft core to control the self-defining IP core through the Avalon bus, so that the The IP core generates the required SPWM waves according to user requirements. The core part of the FPGA system is the self-defined SPWM wave generation IP core, which is also the key point of this patent. The IP core is mainly composed of initial control register, sine wave selection register group, SPWM wave generation logic module, phase control register group module, and Avalon read and write control logic module. It can output high-precision, easy-to-real-time control, and phase-adjustable SPWM waves. The initial control register is used to control whether the IP core starts working and stops working; this IP core contains two methods for generating sine waves. ...

Embodiment 2

[0079] This embodiment takes the control of a three-phase inverter circuit inverter grid connection as an example to explain the specific design scheme and parameters of the IP core proposed by this patent, so first we use the Nios II processor to control the IP core to use the external high-speed parallel ADC pair The peripheral circuit samples the power grid to obtain a sine wave signal. It is assumed here that we can set a clock clk0 with a frequency of 1M Hz for the triangular wave generation module to generate a triangular wave with a frequency of 10K Hz, and then set a clock clk2 with a frequency of 10K Hz for high-speed parallel ADC to sample the sine wave on the power grid, specifically How to determine the clock frequency has been mentioned above, and will not be described in detail here. The system samples the specific AC circuit through the ADC module to obtain SIN1, SIN2 and SIN3, and needs to use the IP core designed by this patent to generate corresponding SPWM w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More