APB bridge for realizing synchronous mode, APB bridge for realizing asynchronous mode and control method thereof

An APB bridge and asynchronous mode technology, applied in the direction of instrumentation, electrical digital data processing, etc., can solve the problems that the offset cannot be clearly determined, the phase relationship is difficult to determine, and sampling errors, etc., to shorten the SOC design, speed up the project progress, The effect of enhancing code reusability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

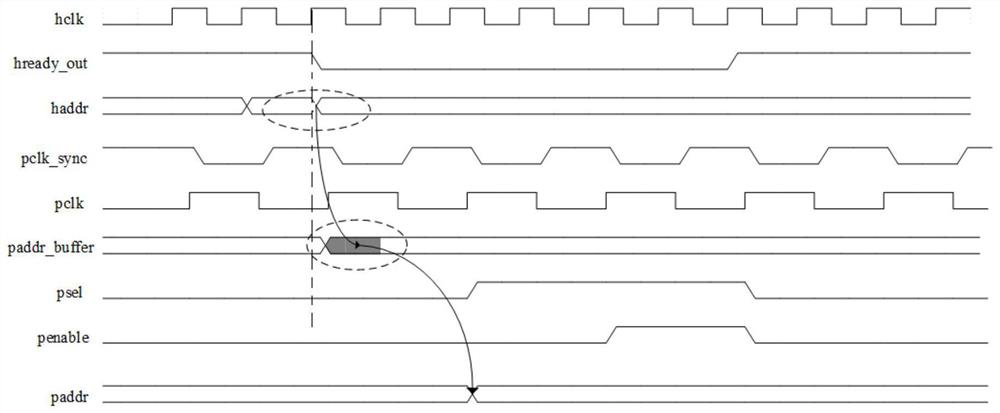

Embodiment 1

[0032] In the technical solutions disclosed in one or more embodiments, such as figure 2 As shown, an APB bridge that implements synchronous mode, the architecture diagram is as follows figure 2 As shown, it includes an AHB buffer area, an APB buffer area, a control logic unit and a state machine; the AHB buffer area is connected to the AHB bus for realizing storing data transmitted from the AHB bus, and the AHB buffer area is connected to the APB buffer area, and the control logic The units are respectively connected to the APB buffer area and the state machine, and the APB buffer area is connected to the APB bus for data interaction; the control logic unit is used to control the data storage and reading of the data in the AHB buffer area and the APB buffer area according to the same control clock .

[0033] The AHB buffer area is used to store the data transmitted from the AHB bus. The data transmitted from the AHB bus includes the write / read bus address (haddr) transmitt...

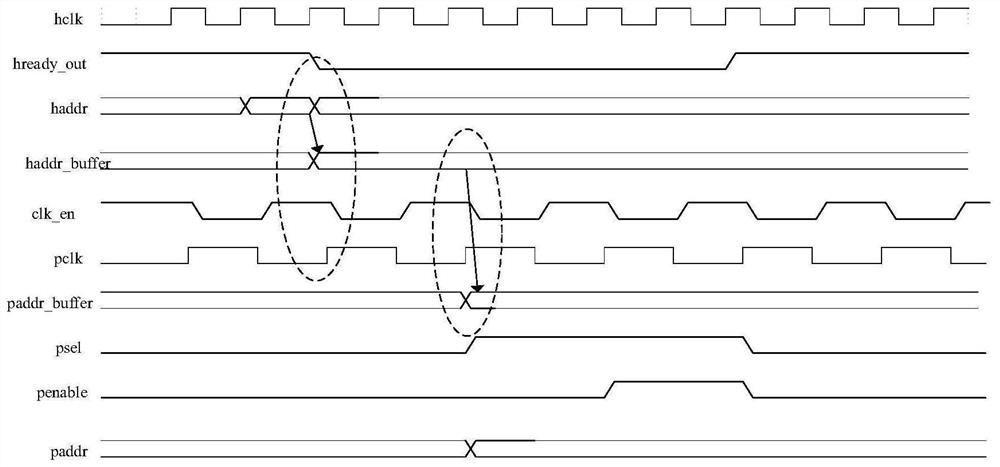

Embodiment 2

[0054] In the technical solutions disclosed in one or more embodiments, such as Figure 5 As shown, the present embodiment provides a kind of APB bridge that realizes asynchronous mode, comprises asynchronous prefetch FIFO, selector, state machine and APB cache area; Described asynchronous prefetch FIFO is connected with state machine through selector, and described state machine Connect to the APB slave through the set interface, and the asynchronous prefetch FIFO is connected to the AHB bus and the APB buffer respectively; the state machine is used to control the data reading and writing of the APB slave connected to the APB bus according to the data in the APB buffer.

[0055] The asynchronous prefetch FIFO is configured to implement commands and data sent from the AHB clock domain to the APB clock domain synchronously. It can be set, when the asynchronous prefetch FIFO write command and read command are valid, the data is valid at the time, which speeds up the transmission...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com