A turbo code decoder and processing method based on reverse butterfly calculation

A butterfly computing and decoder technology, applied in the Turbo code decoding structure and processing field based on reverse butterfly computing, can solve the problems of turbo code decoder power consumption, low storage capacity, etc.

Active Publication Date: 2021-09-14

SOUTHWEST UNIV

View PDF7 Cites 0 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

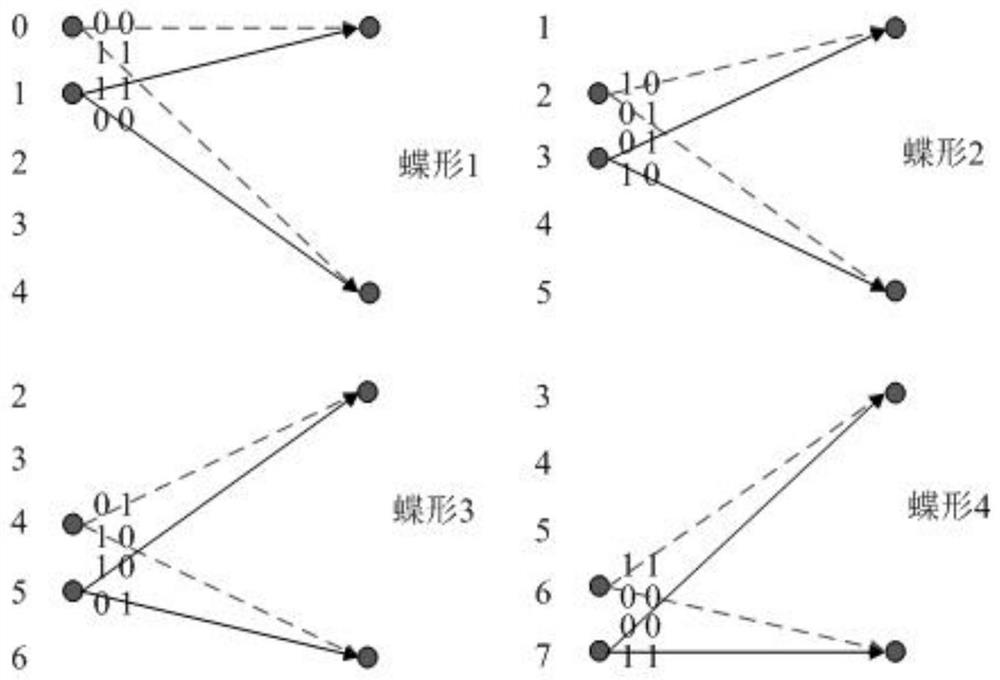

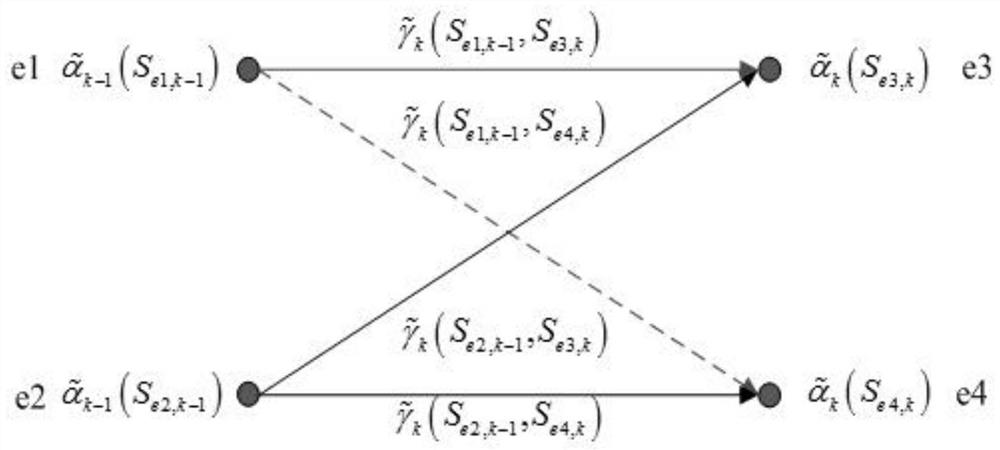

[0007] The present invention mainly solves the power consumption problem of the Turbo code decoder in the wireless communication system, and proposes a low-storage Turbo code decoder structure based on reverse calculation by dividing the grid into four basic units. Store those that satisfy the reverse calculation, and directly reverse the calculation when it meets the next need

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment 1

[0077] Take the FPGA implementation of the Turbo code decoder under the LTE-Advanced standard as an example; the selected code length is 1024, the code rate is 1 / 3, the FPGA chip uses the EP4CE75F23C8 target device, the programming language is Verilog HDL, and the QuartusⅡ13.1 platform is used Carry out Turbo code decoder implementation. The use of the total storage capacity obtained by simulating the full compilation of the forward state metric calculation part shows that the total storage capacity consumed by the traditional direct storage of 8 state metrics is 2560 bits, while the total storage capacity consumed by our proposed method is The storage capacity is 896bits, so the SMC is effectively reduced by 65%.

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

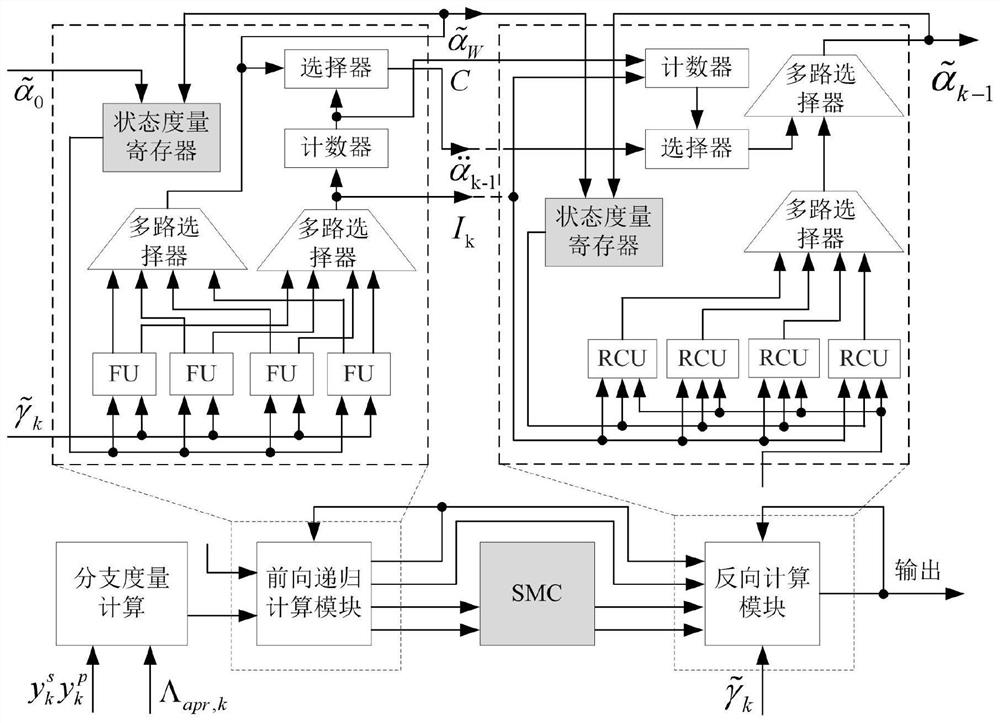

The invention provides a Turbo code decoder based on reverse butterfly calculation and a processing method, including a branch metric calculation module, a forward recursive calculation module, an SMC module and a reverse calculation module. The redundant calculation complexity introduced by the present invention is low, and the hardware overhead introduced by the forward recursive module and the reverse calculation module is only simple addition, shift and comparison operations, which is convenient for hardware implementation. The invention greatly reduces the capacity of the SMC through the innovative definition and calculation of sign bits, and realizes accurate reverse recalculation, which can significantly reduce the capacity of the SMC, and at the same time, the loss of decoding performance is small, and the power consumption is lower than that of the existing decoding. Encoder is lower.

Description

technical field [0001] The invention belongs to the field of wireless communication systems, and in particular relates to a turbo code decoding structure and processing method based on reverse butterfly calculation. Background technique [0002] In recent years, due to its good error correction performance and decoding performance close to the Shannon limit, Turbo codes have greatly reduced the SMC capacity and realized accurate reverse recalculation through innovative sign bit definition and calculation. In wireless communication applications, the decoder is considered to be the main bottleneck of the power consumption of the signal receiving terminal, and more than half of the power consumption of the decoder is mainly used for accessing the SMC. Therefore, a low-power Turbo code decoder structure that reduces SMC capacity and maintains better decoding performance has become the focus of people's research. [0003] In order to reduce the power consumption of the Turbo cod...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Patents(China)

IPC IPC(8): H03M13/29

CPCH03M13/2957

Inventor 詹明罗小红肖鸣郭靖

Owner SOUTHWEST UNIV