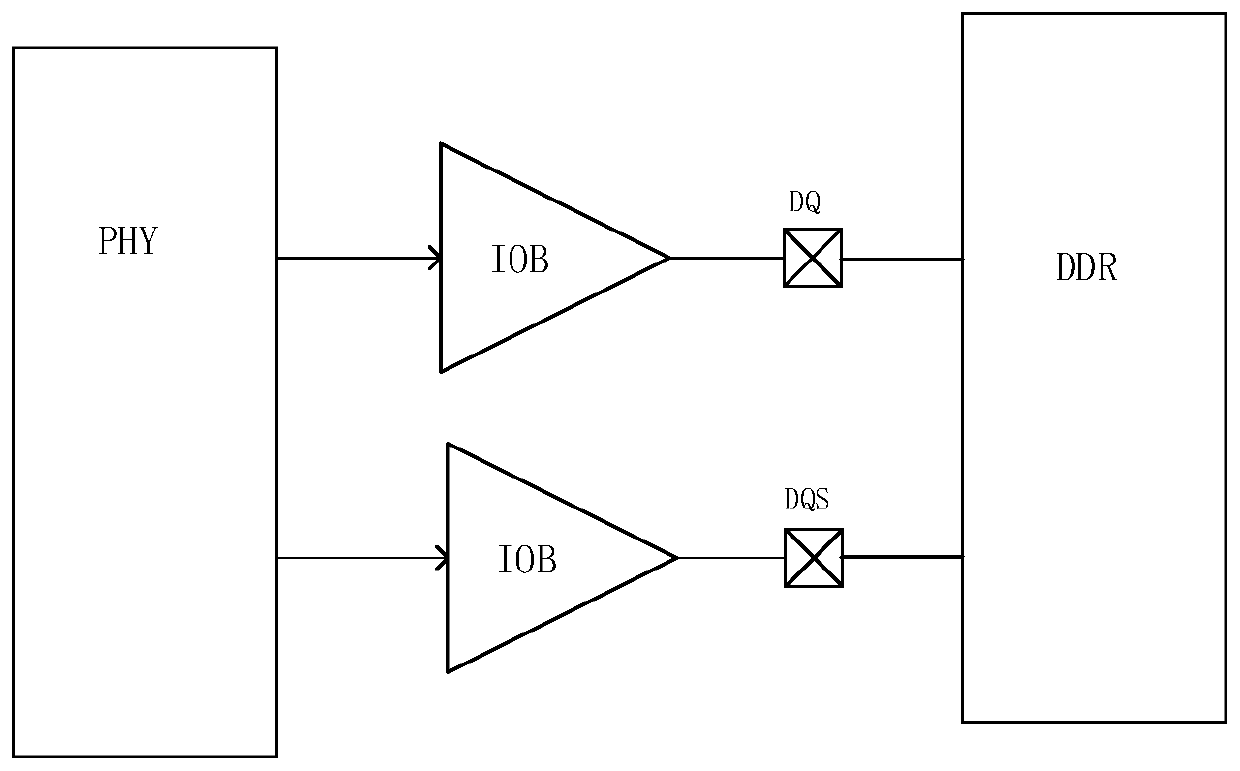

Method and system for training DQ and DQS signal duty ratios of DDR memory controller

A technology of memory controller and control signal, applied in the direction of digital memory information, static memory, instrument, etc., can solve the problems of DQ and DQS signal duty cycle distortion, to solve the signal duty cycle distortion, improve read and write speed and reliability effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

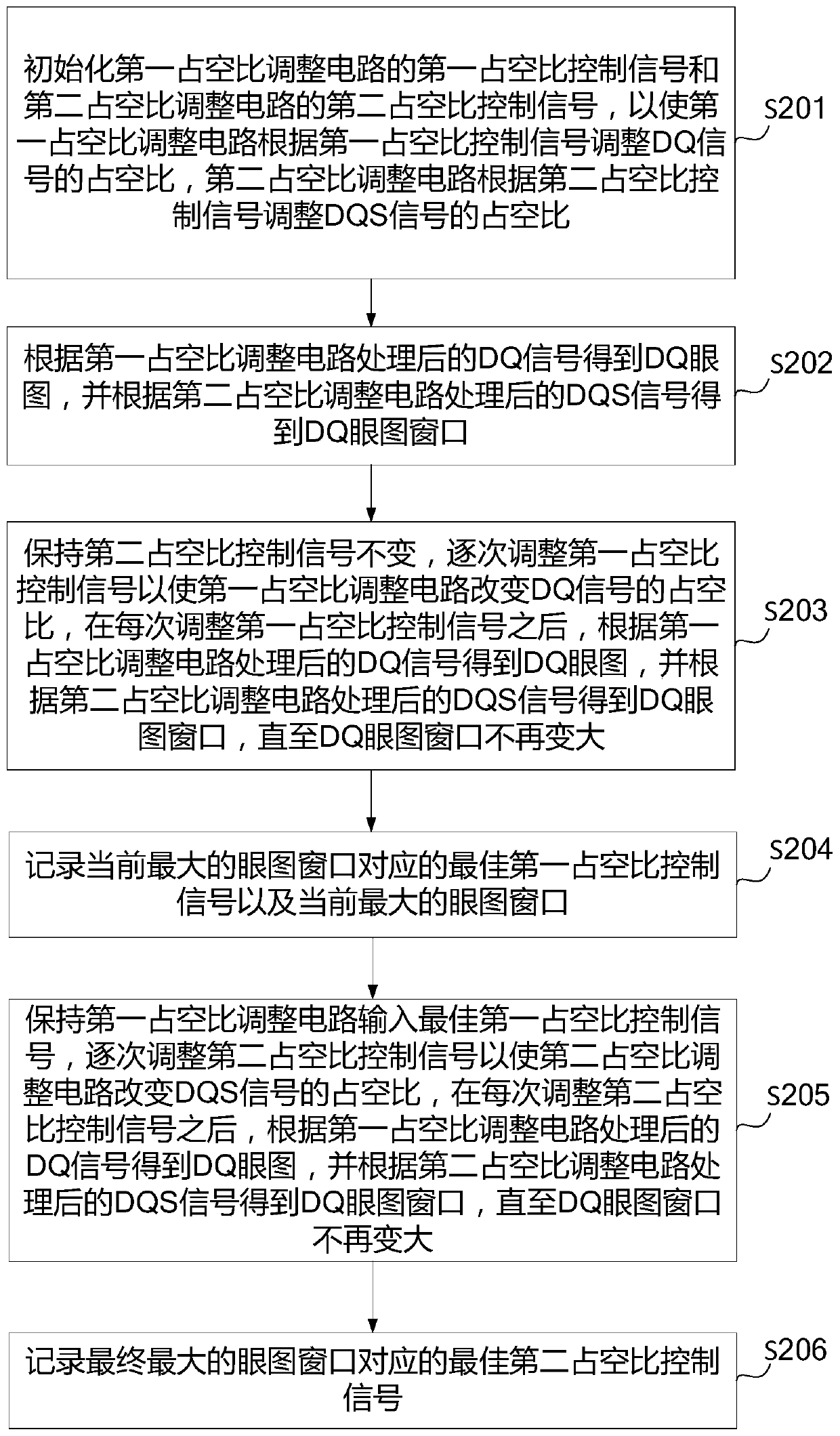

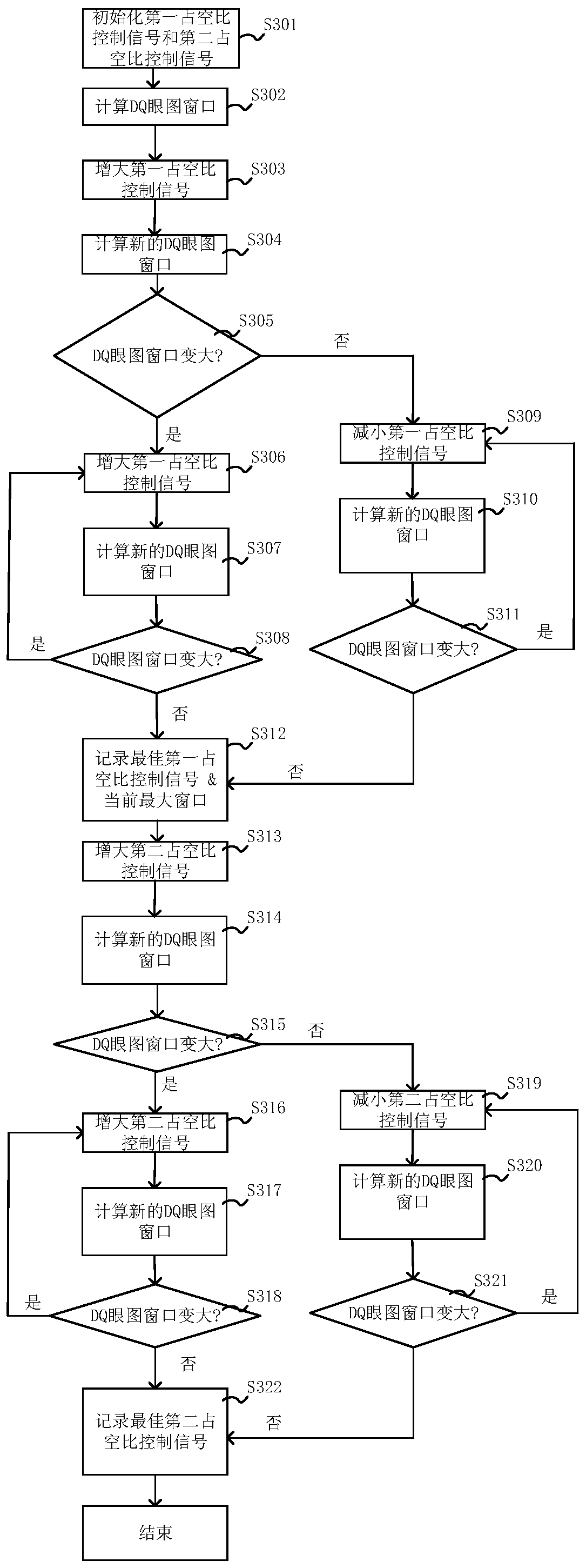

[0062] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the drawings in the embodiments of the present invention. Obviously, the described embodiments It is only some embodiments of the present invention, but not all embodiments. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0063] This embodiment provides a DQ and DQS signal duty cycle training method of a DDR memory controller, such as figure 2 As shown, the method includes:

[0064] S201. Initialize the first duty ratio control signal of the first duty ratio adjustment circuit and the second duty ratio control signal of the second duty ratio adjustment circu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More