Static heterogeneous reconfigurable array layout method based on multi-stage simulated annealing

A technology of simulated annealing and layout method, applied in the field of interconnect structure of reconfigurable arrays, can solve the problems of reduced routing rate, inability to accurately respond to position constraints, and inability to routing, and achieve the effect of improving routing rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

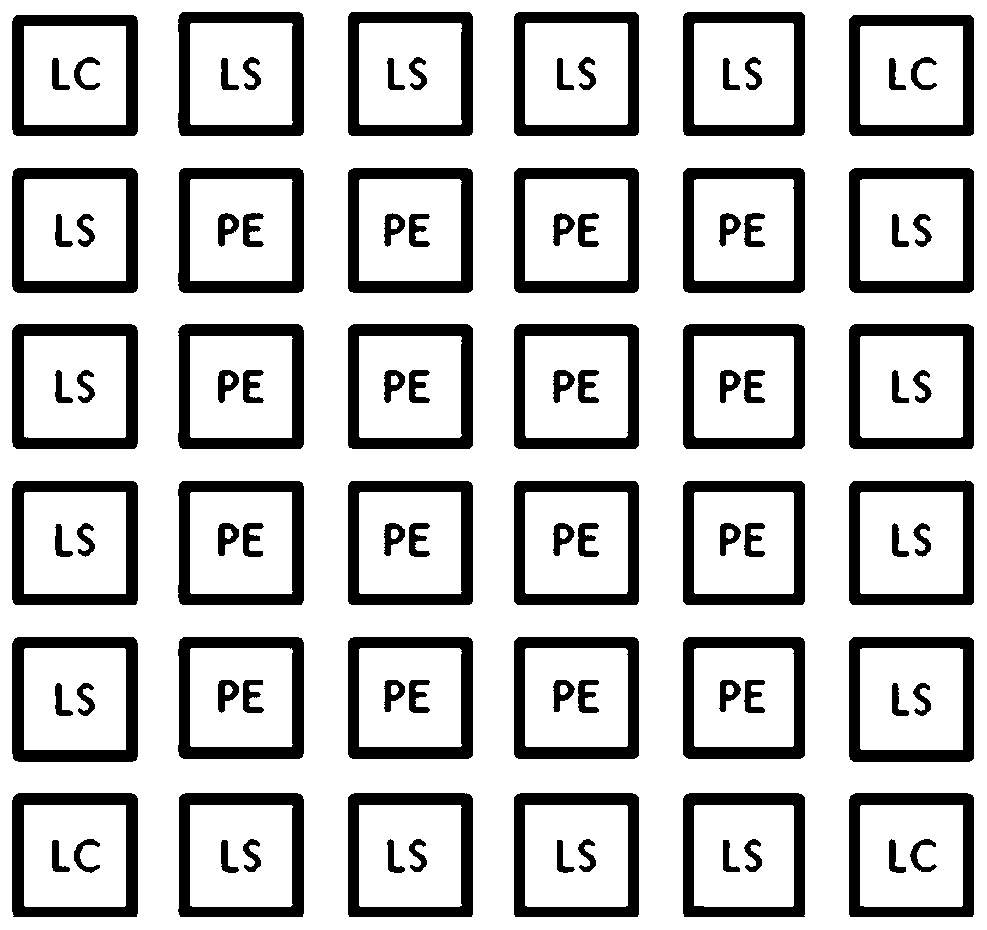

[0032] Such as Figure 5 Lays out a dataflow graph into an array as shown. The array is a common heterogeneous array, and the array resources are divided into three categories, loop control, storage processing and general computing. The general-purpose computing unit, that is, PE (Processing Element), is the most numerous unit in the array; while the storage processing unit, that is, LS (Load and Store), is often distributed at the outermost periphery of the array, and its function is the most important, but it is more important than other types. The location constraints of resources are stricter; while the loop control unit LC (Loop Control) is a type of resource that is more important than PE, but the priority is not as good as LS.

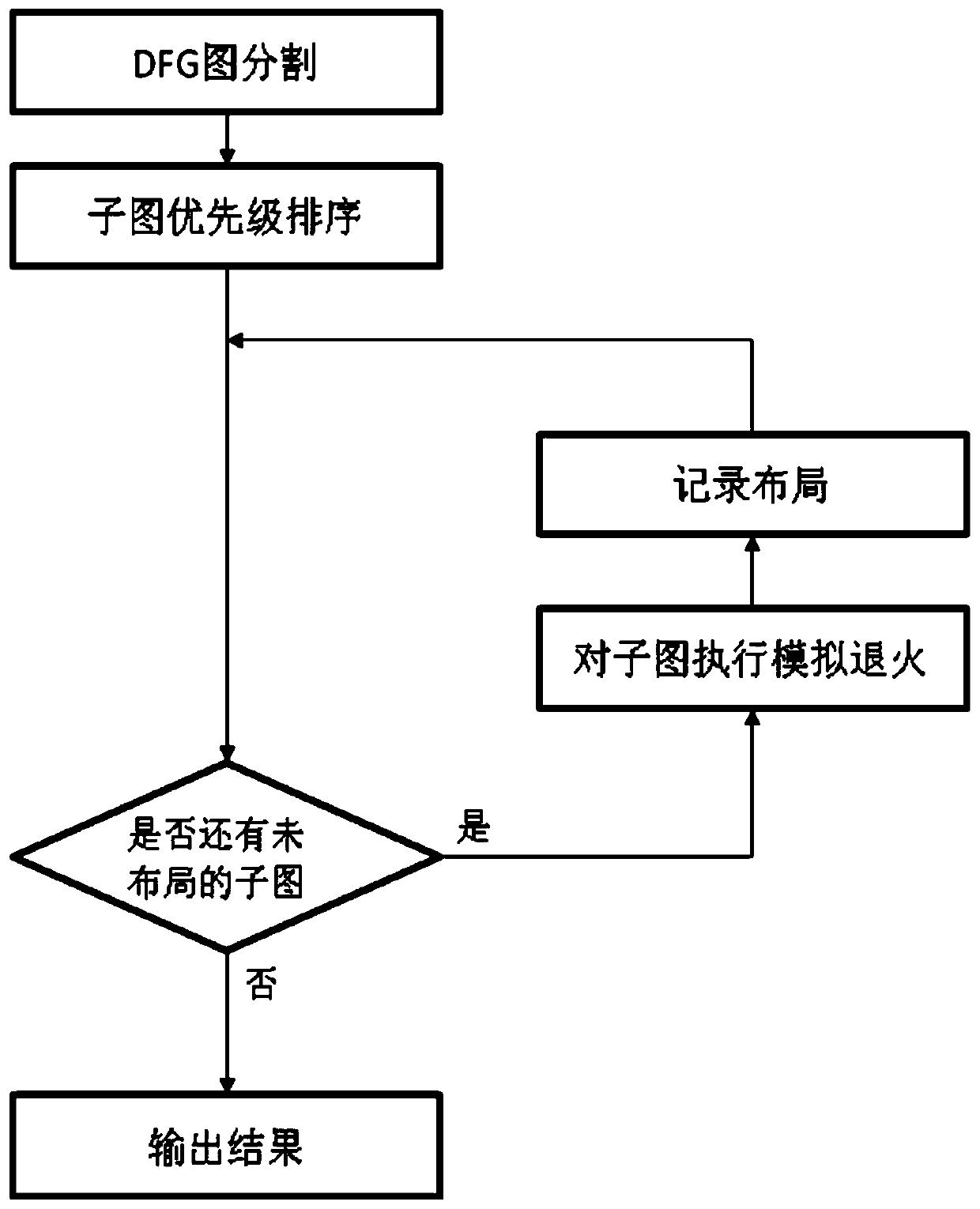

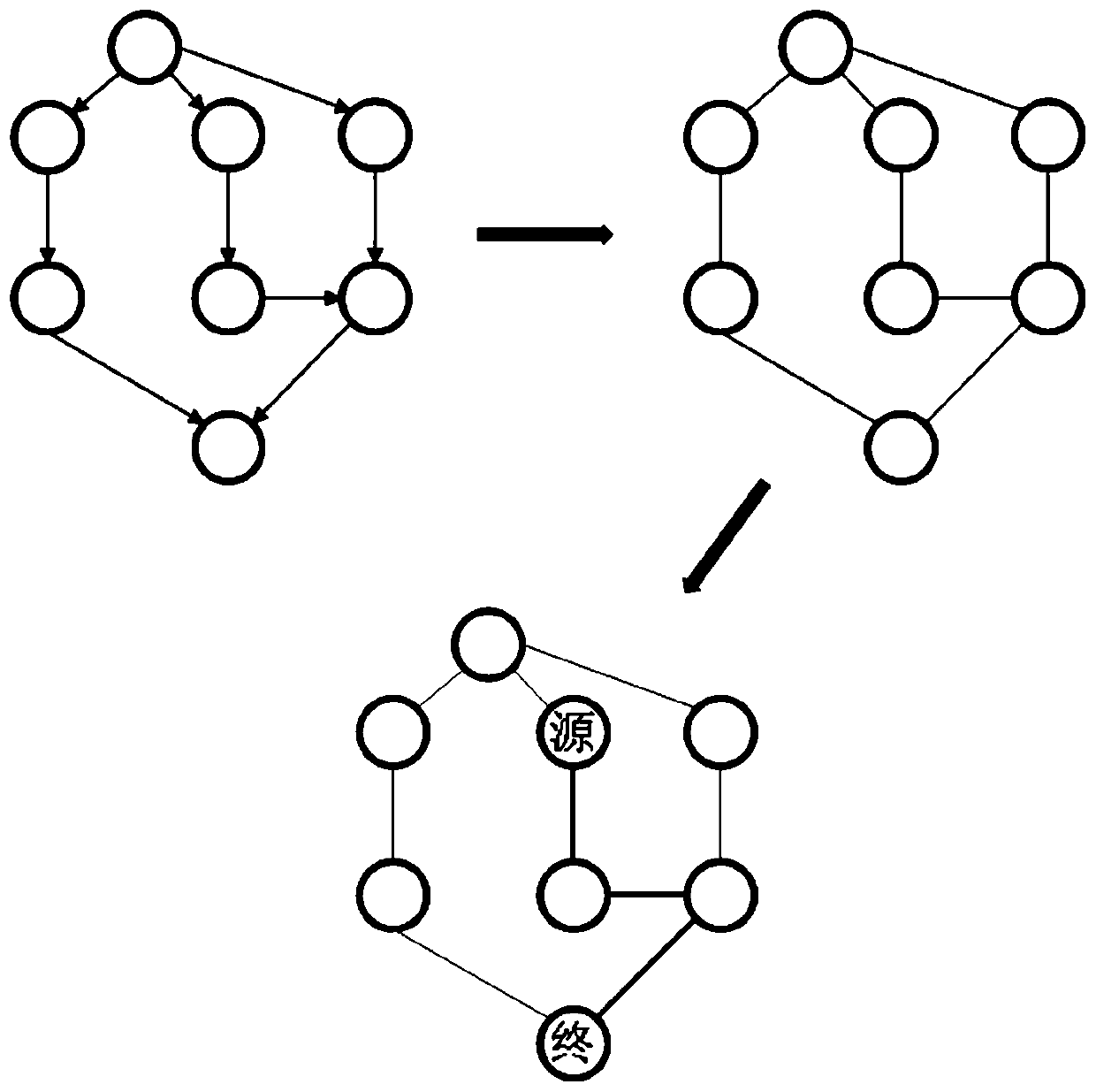

[0033] In the multi-stage simulated annealing method, according to the importance of the resources of the heterogeneous reconfigurable array in the array, the layout process is divided into multiple stages according to different resource types....

Embodiment 2

[0041] The present invention mainly proposes a static heterogeneous reconfigurable array layout method based on multi-stage simulated annealing. Taking six applications in MachSuite that are suitable for acceleration of static heterogeneous reconfigurable arrays as an example, from the two aspects of deployment rate and algorithm time Analyze the algorithm and interconnection quality from two angles, reflecting the technical effect of this patent:

[0042] Routing rate: The scale of the array structure used in this embodiment is 10×10. For each combination of algorithm and interconnection structure, the algorithm is repeatedly executed 50 times, and the number of successful completion of layout and wiring is recorded, and the proportion is taken as the ratio of routing. Rate. Table 1 shows different algorithms under different interconnection resource structures, such as Figure 4 , using the comparison of the pass rate of the two algorithms.

[0043] Table 1 Comparison of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More