Bus real-time synchronous control device

A technology of real-time synchronization and control device, applied in the direction of synchronization device, program control, computer control, etc., can solve problems such as less than ideal effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 2

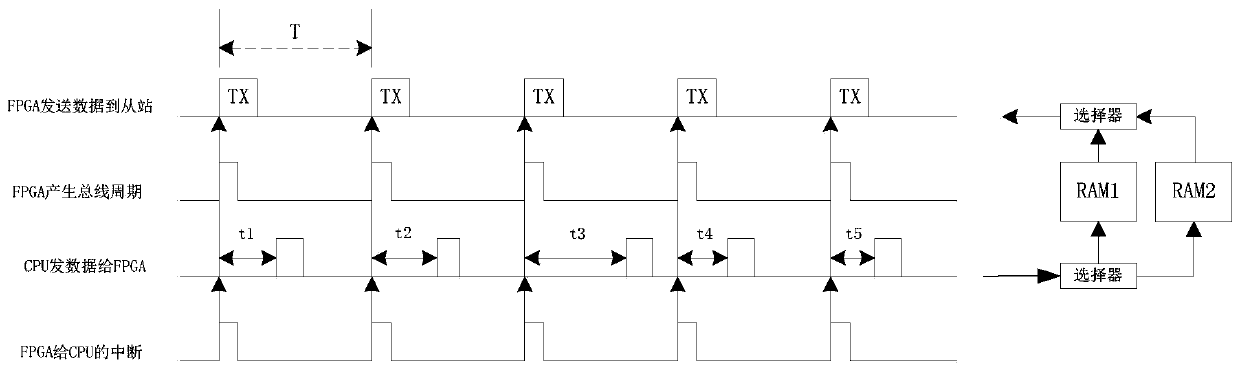

[0031] Embodiment 2, on the basis of Embodiment 1, sample ZYNQ series XC7Z020 high-performance SOC of Xilinx, this device integrates dual A9 processors and a large-capacity FPGA. The dual A9 core adopts the Linux system operating system, and the measured real-time performance is between -100us-100us. One of the A9 cores is used for user interaction, Internet of Things and other functions, and the other A9 core is used for the calculation of motion control algorithms and EtherCAT protocol stack processing. FPGA completes timing transmission and reception of EtherCAT protocol, generation of synchronous clock, 100M Ethernet pipe, data cache, etc. A9 and FPGA communicate through the AXI bus. The bus clock is 100M, the bus data bit width is 32, and the communication speed is very fast. The A9 write cache time can be very short, which hardly affects the real-time calculation of the motion algorithm. The FPGA has a 4Mb FIFO space, and the CPU only needs to send the data to the FIFO ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More