Anti-coupling-interference power supply generation circuit

A technology for coupling interference and generating circuits, which is applied in the field of power generating circuits and can solve problems such as exceeding the breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

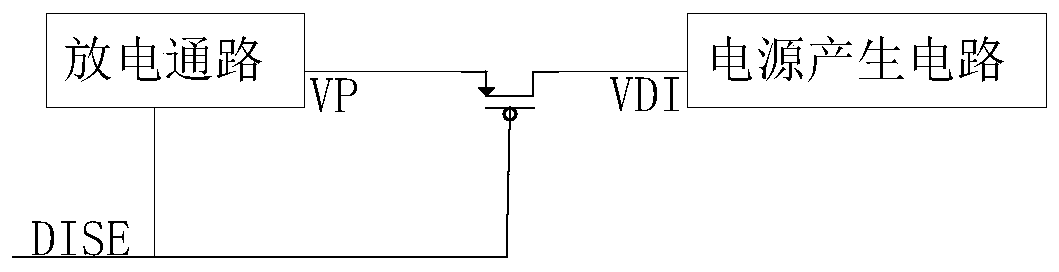

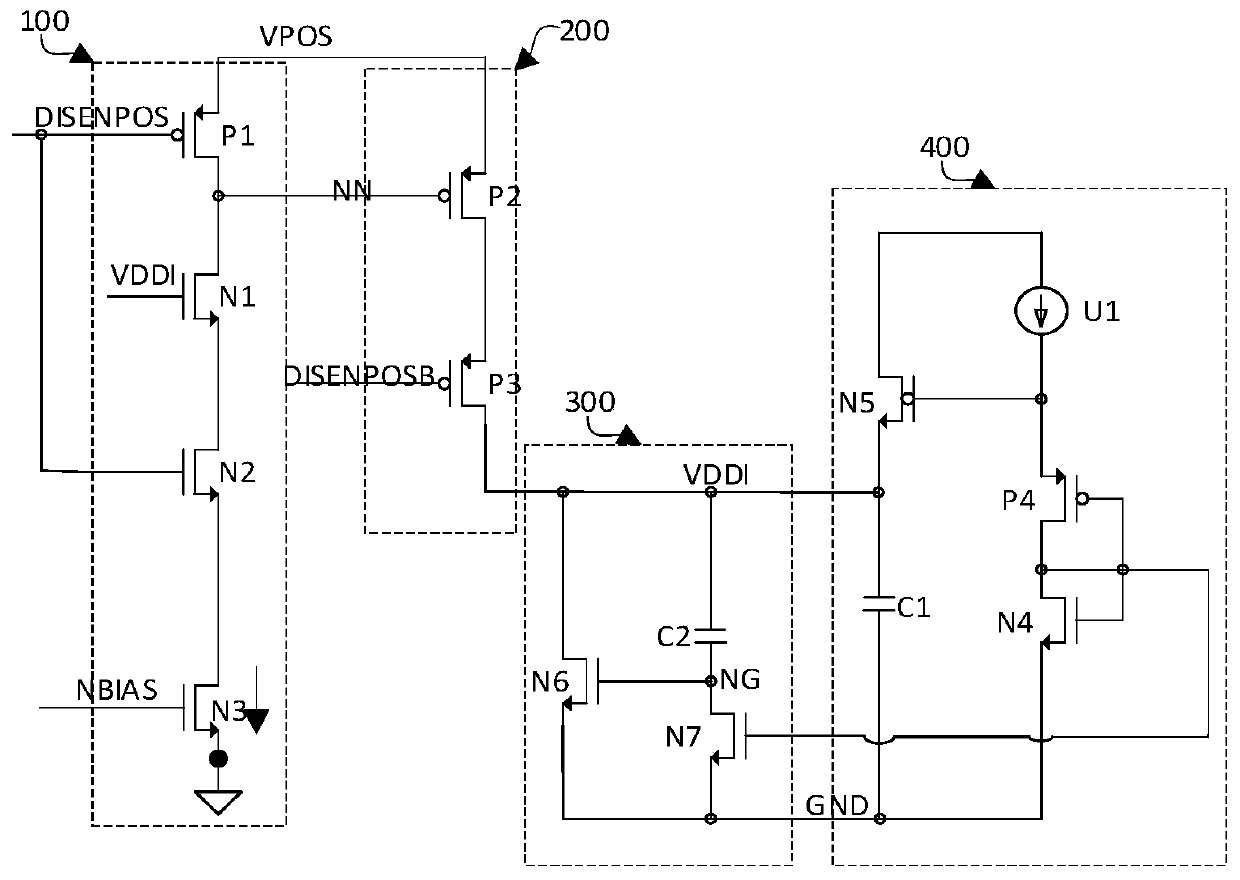

[0035] This embodiment provides an anti-coupling interference power generating circuit, refer to figure 2 , the anti-coupling interference power generation circuit includes:

[0036] The first discharge path 100, the high-voltage input node VPOS of the first discharge path 100 is connected to the first voltage, the first voltage is a high voltage, and the control terminal of the first discharge path 100 is connected to the first control signal DISENPOS for the first In the discharge stage, the high-voltage input node VPOS is discharged;

[0037] The second discharge path 200, the second discharge path 200 is connected between the first discharge path 100 and the power generation path 400, the control terminal of the first discharge path 100 is connected to the second control signal DISENPOSB, the transfer node NN of the second discharge path 200 connected to the first discharge path 100; used to discharge the high voltage input node VPOS to the potential of the power output ...

Embodiment 2

[0043] This embodiment is on the basis of embodiment 1, with reference to figure 2 An anti-coupling interference power generation circuit is provided, and the anti-coupling interference power generation circuit includes:

[0044] The first discharge path 100, the first discharge path 100 includes the first PMOS transistor P1, the first NMOS transistor N1, the second NMOS transistor N2 and the third NMOS transistor N3 connected in series; the gate of the first PMOS transistor P1 is the first discharge The control terminal of the channel 100, the source of the first PMOS transistor P1 is connected to the first voltage, the drain of the first PMOS transistor P1 is connected to the drain of the first NMOS transistor N1; the gate of the first NMOS transistor N1 is connected to the power supply output node VDDI , the source of the first NMOS transistor N1 is connected to the drain of the second NMOS transistor N2; the gate of the second NMOS transistor N2 is connected to the gate o...

Embodiment 3

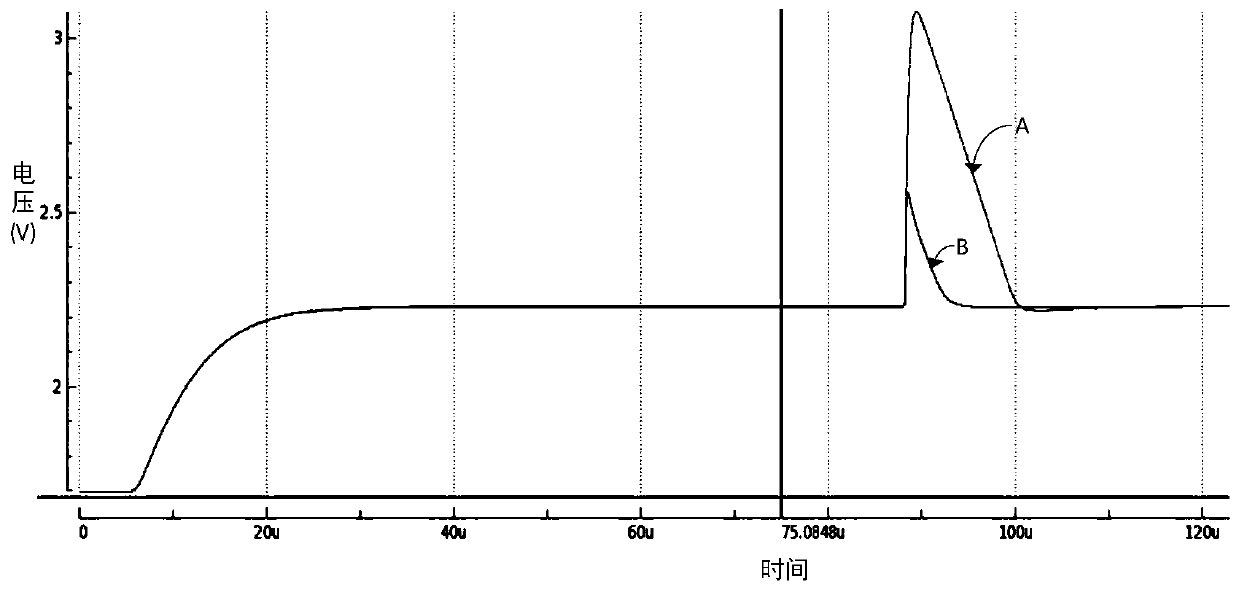

[0054] In this embodiment, on the basis of implementation 2, in order to prevent the potential of the anti-coupling interference control node NG from turning on the sixth NMOS transistor N6 in the initial state, the anti-coupling interference control node NG is quickly pulled down when the potential of the anti-coupling interference control node NG is raised. The potential of the coupling interference control node NG, the anti-coupling interference circuit 300 also includes a seventh NMOS transistor N7, the gate of the seventh NMOS transistor N7 is connected to the power generation channel 400, the source of the seventh NMOS transistor N7 is grounded, and the seventh NMOS transistor N7 The drain of N7 is connected to the anti-coupling interference control node NG.

[0055] Specifically, the gate of the seventh NMOS transistor N7 is connected to the gates of the fourth PMOS transistor P4 and the fourth NMOS transistor N4, and the seventh NMOS transistor N7 can be mirrored to gen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More