Chip-on-film (COF) package structure

A technology of film-on-chip packaging and packaging colloid, which is applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve the problems of arching and gaps, poor heat dissipation efficiency, and the inability to effectively confirm that the heat dissipation patch is closely attached to the chip and packaging colloid Combination and other issues to achieve good cooling efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The present invention will be described more fully with reference to the accompanying drawings of this embodiment. However, the present invention can also be embodied in various forms and should not be limited to the embodiments described herein. The thickness, size or size of layers or regions in the drawings may be exaggerated for clarity. The same or similar reference numerals denote the same or similar elements, and the following paragraphs will not repeat them one by one.

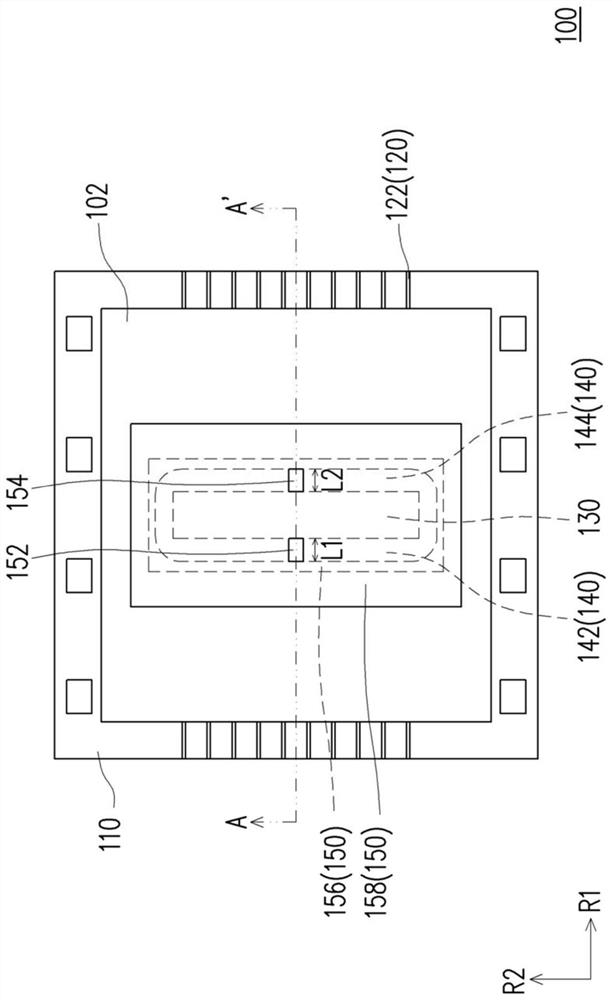

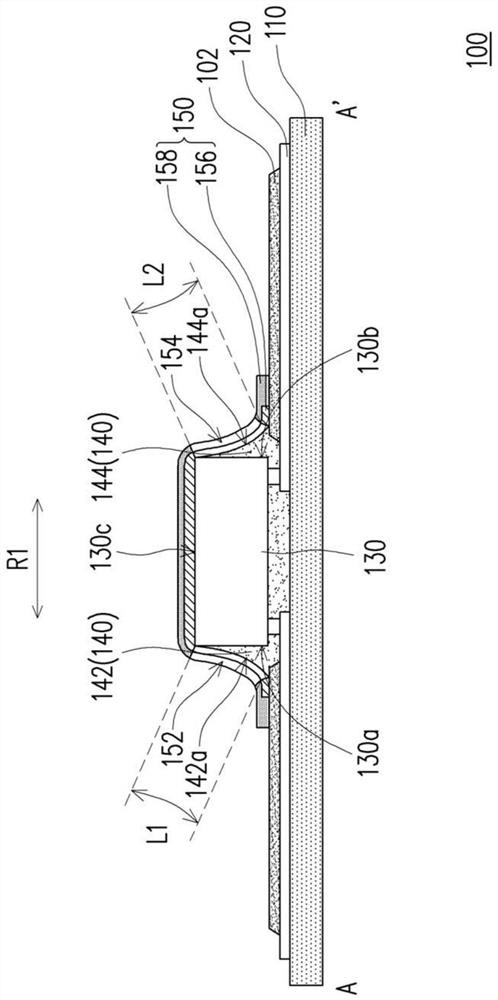

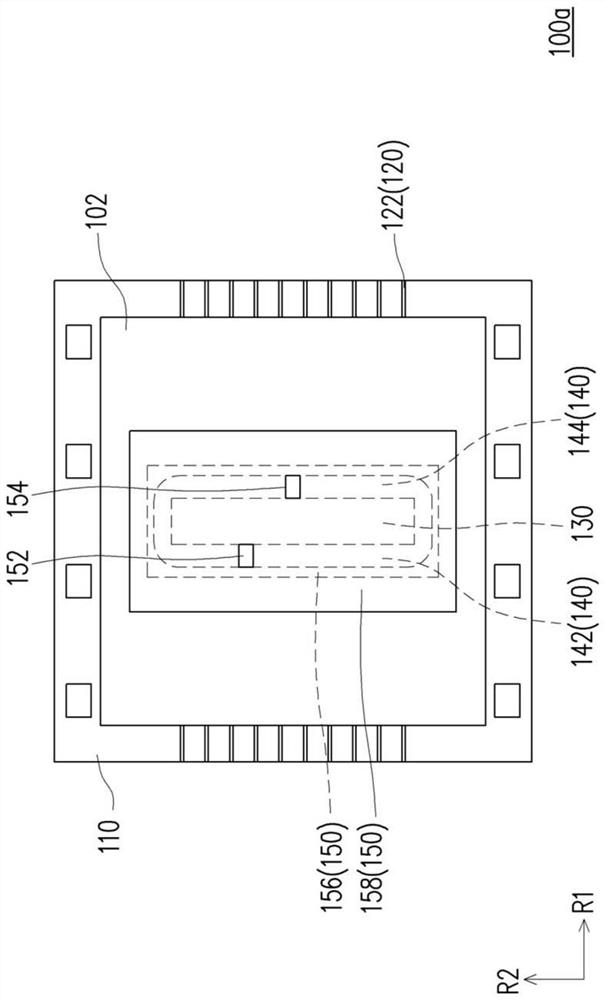

[0043] Figure 1A is a schematic top view of a chip-on-film packaging structure according to an embodiment of the present invention. Figure 1B yes Figure 1A Schematic cross-sectional view along section line A-A'. Please also refer to Figure 1A and Figure 1B , in this embodiment, the thin film chip-on-chip packaging structure 100 includes a flexible substrate 110 , a wiring layer 120 , a chip 130 , an encapsulant 140 and a heat dissipation patch 150 . The material of the flexible substrat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More