Semiconductor packaging body and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of wafer-level chip-scale package warpage, thick packaging colloid, and unfavorable wafer-level Chip size package miniaturization and other issues to achieve the effect of good heat dissipation efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

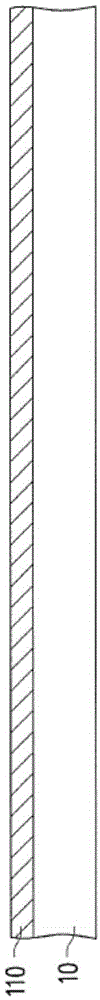

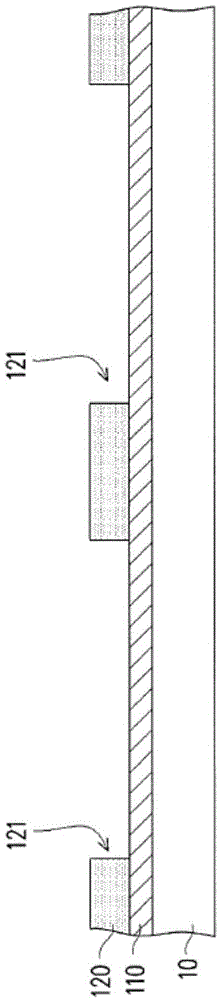

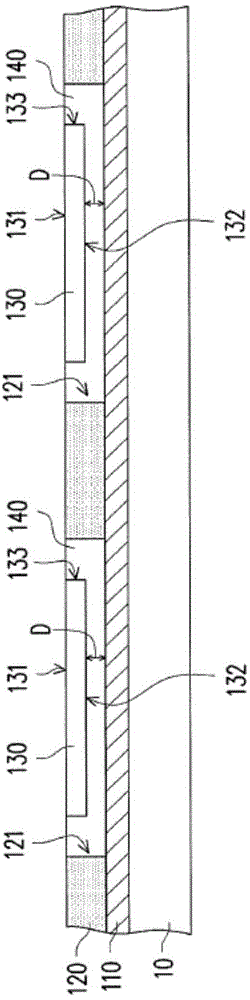

[0045] Figure 1A to Figure 1G A manufacturing flow of a semiconductor package according to an embodiment of the present invention is shown. Please refer to Figure 1A Firstly, the carrier 10 is provided, and the heat dissipation material layer 110 is formed on the carrier 10 . For example, the carrier 10 can be a plate made of hard material or flexible material, or a release film (such as a thermal release adhesive film, an ultraviolet light release adhesive film or other suitable adhesive films), but the present invention is for The material of the carrier 10 is not limited in any way. Here, the heat dissipation material layer 110 is temporarily fixed on the carrier 10 by, for example, gluing, so as to facilitate subsequent manufacturing processes. In this embodiment, the heat dissipation material layer 110 may be made of aluminum, magnesium, copper, silver, gold or other metals or metal alloys with good thermal conductivity, or graphite or other non-metallic materials wit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More