A method and device for scheduling ultra-high-order single-cycle packets

A scheduling method and single-cycle technology, applied in transmission systems, electrical components, etc., can solve problems such as difficulty in meeting the high-performance scheduling requirements of commercial routers, and reduce implementation overhead and scheduler logic design complexity, small hardware costs, and avoidance. The effect of communication overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

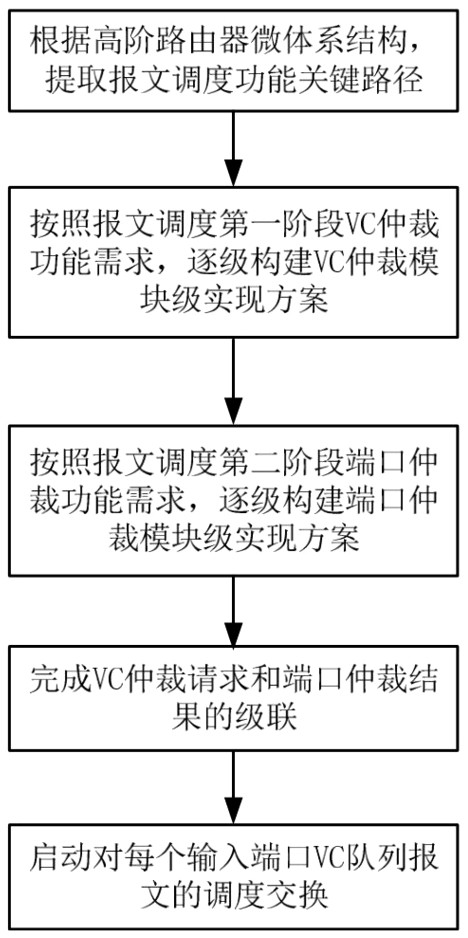

[0042] like figure 1 As shown, the ultra-high-order single-period packet scheduling method in this embodiment includes the following steps:

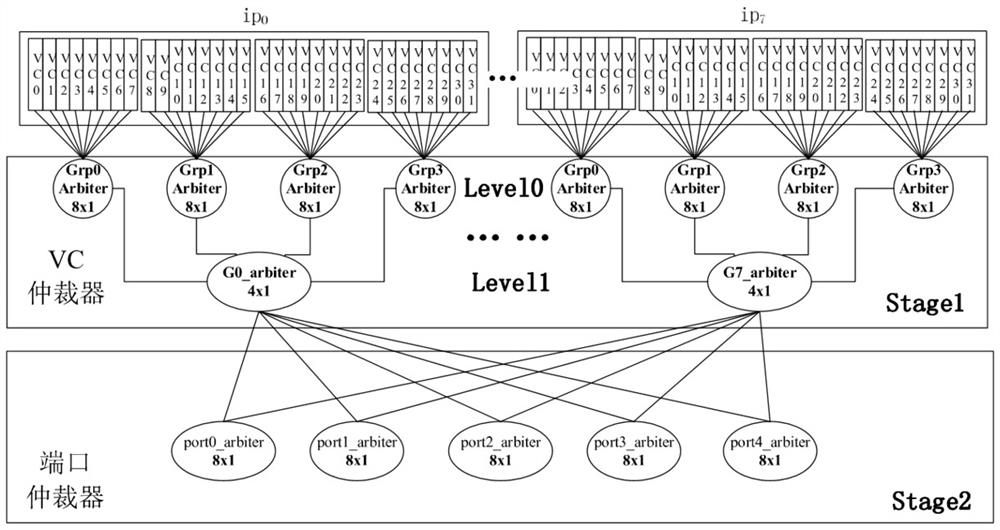

[0043] Step 1: According to the micro-architecture characteristics of the high-level router, extract the key path of its message scheduling, and divide the message scheduling into the VC arbitration function in the first stage and the port arbitration function in the second stage;

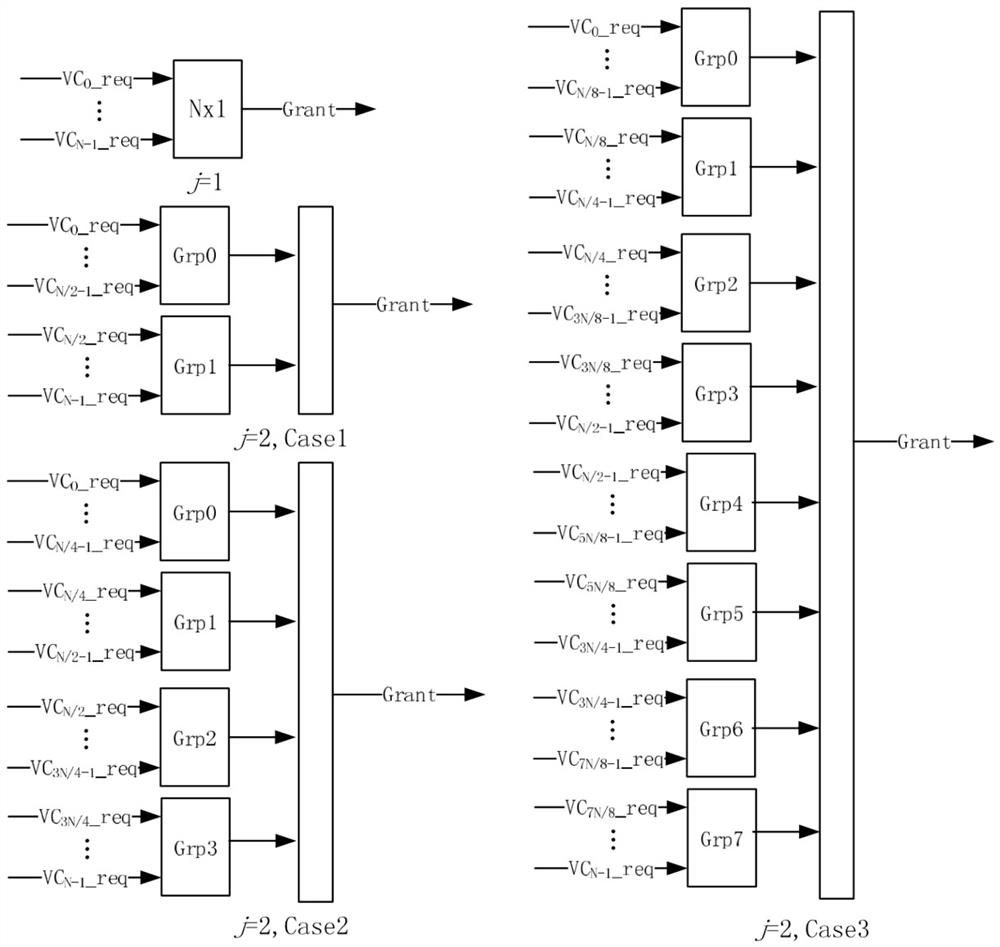

[0044] Step 2: According to the VC arbitration function requirements in the first stage of message scheduling, a distributed and hierarchical design method is used to evaluate and build a VC arbiter module-level implementation scheme step by step;

[0045] Step 3: According to the port arbitration function requirements in the second stage of message scheduling, a distributed and hierarchical design method is used to evaluate and build a port arbiter module-level implementation plan step by step;

[0046] Step 4: connect the port arbitration request generate...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More