JTAG debugging circuit and computer debugging tool

A technology for debugging circuits and debugging tools, applied in computing, electrical digital data processing, instruments, etc., can solve the problems of complex JTAG link design and rising cost, and achieve the effect of improving design efficiency and reducing product defect rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] In order to make the object, technical solution and advantages of the present invention clearer, the embodiments of the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

[0021] It should be noted that all expressions using "first" and "second" in the embodiments of the present invention are to distinguish two entities with the same name but different parameters or parameters that are not the same, see "first" and "second" It is only for the convenience of expression, and should not be construed as a limitation on the embodiments of the present invention, which will not be described one by one in the subsequent embodiments.

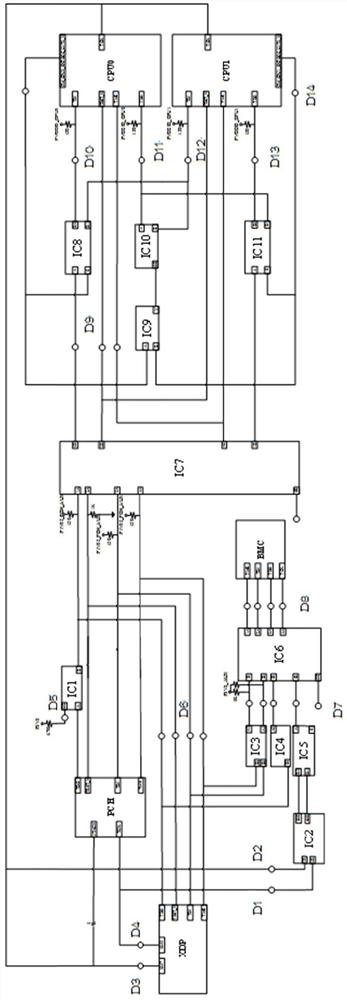

[0022] Based on the above purpose, the first aspect of the embodiments of the present invention proposes a JTAG debugging circuit. figure 1 What is shown is a schematic diagram of an embodiment of the JTAG debugging circuit provided by the present i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More