Parallel layer distribution method based on through hole perception under super-large-scale integrated circuit

A technology of large-scale integrated circuits and distribution methods, which is applied in the fields of electrical digital data processing, instruments, calculations, etc., can solve the problems of increasing the line network and increasing the running time of the layer distribution algorithm, and achieve the goal of reducing the number of through holes and improving efficiency Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The technical solution of the present invention will be specifically described below in conjunction with the accompanying drawings.

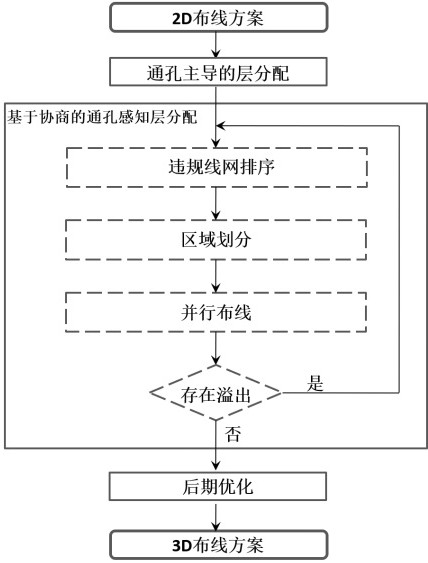

[0045] The present invention provides a parallel layer allocation method based on through-hole perception under VLSI, comprising the following steps:

[0046] Step S1, via-dominated layer allocation stage:

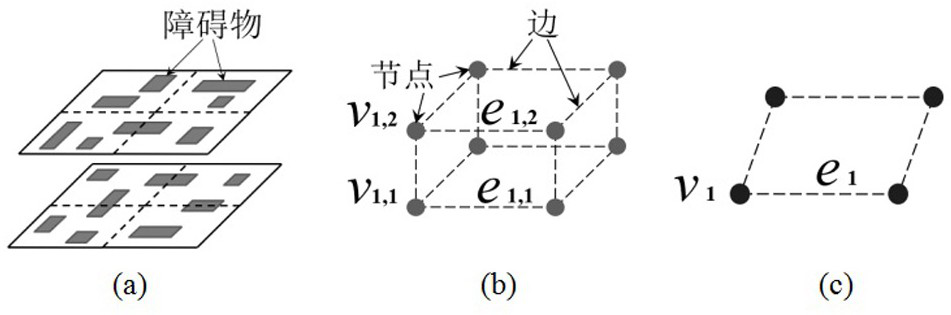

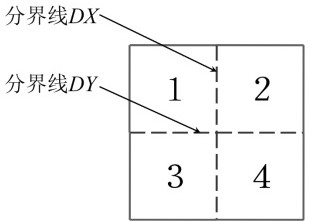

[0047] Divide the wiring area, divide the line network that can be wired in parallel, and carry out the parallel wiring of the layer allocation based on the principle of the least number of through holes;

[0048] Step S2, negotiation-based via-aware layer allocation stage:

[0049] Sorting, dismantling, and rewiring the illegal nets appearing in the parallel wiring scheme of step S1 in an iterative manner until there is no illegal net;

[0050] Step S21, sorting the illegal wire nets appearing in the parallel wiring scheme of step S1;

[0051] Step S22, divide the wiring area for the illegal wire net, divide the wire net that can ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More