CPU instruction implementation method supporting multi-data access

A multi-data and instruction technology, applied in the fields of computer software, instruction compiler design, and CPU instruction set design, can solve problems such as inefficiency and complex implementation methods

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The present invention will be described in further detail below with reference to the accompanying drawings and examples.

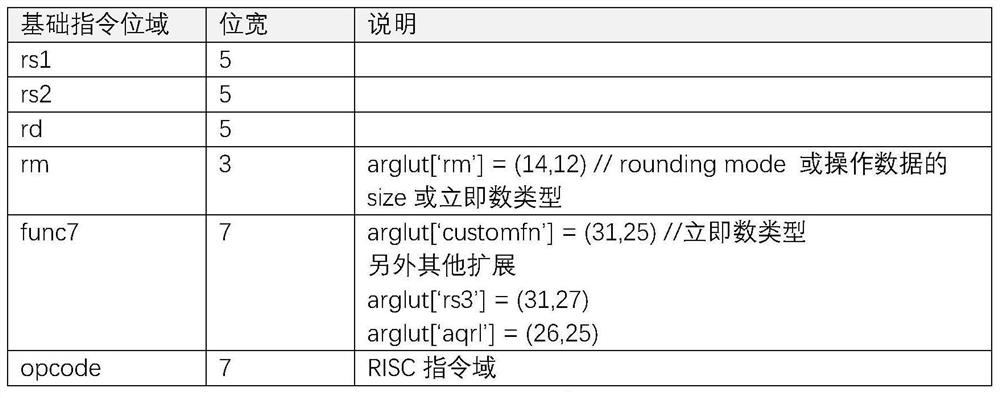

[0035] figure 1 It is the basic instruction bit field definition based on the basis of RISC and the commonly used instruction set. In this definition, the expression form of 32 instruction bits is taken as an example.

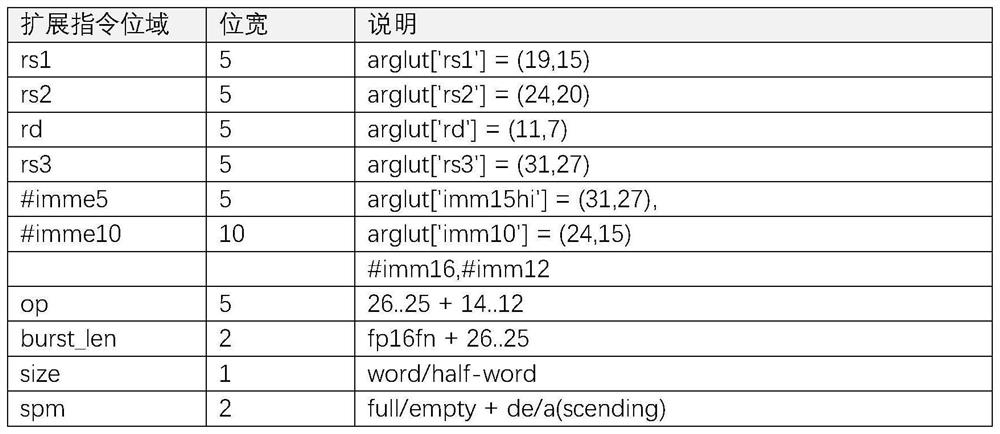

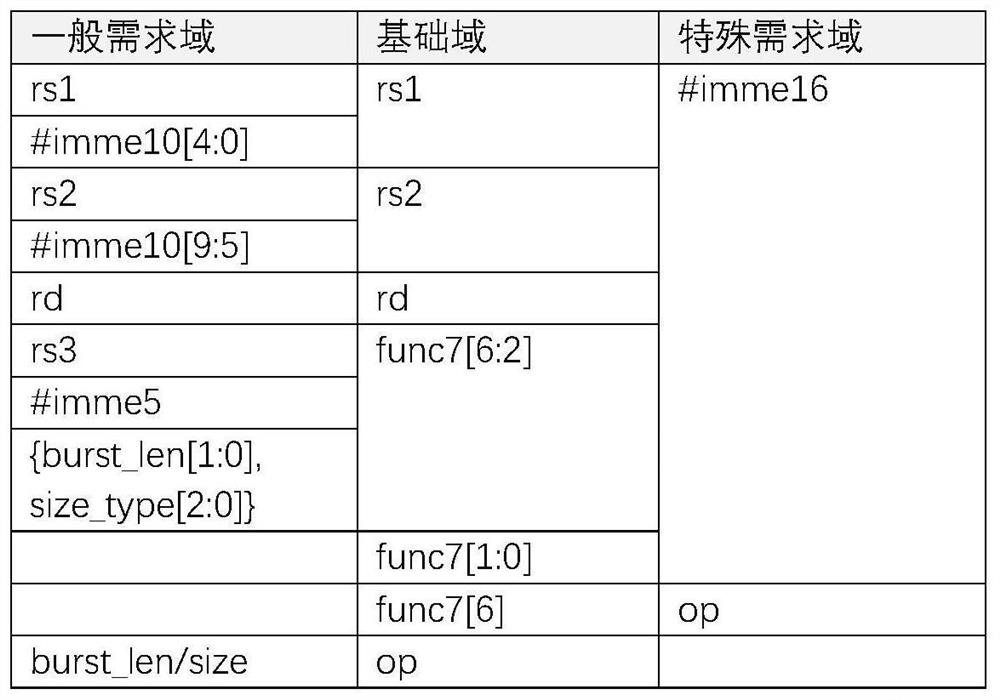

[0036] On this basis, the requirements for supporting multiple data access are very diverse, and the required multiple data operation instructions have the following characteristics:

[0037] According to the data type of the access operation, it is divided into two categories: the minimum support for the byte data required for calculation, such as half float is 2 bytes in length; the most commonly supported single-shot data transmission length that the bus can support, such as 4 bytes commonly used in embedded length.

[0038] According to the length setting method, it is divided into two categories: directly specify the registe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com