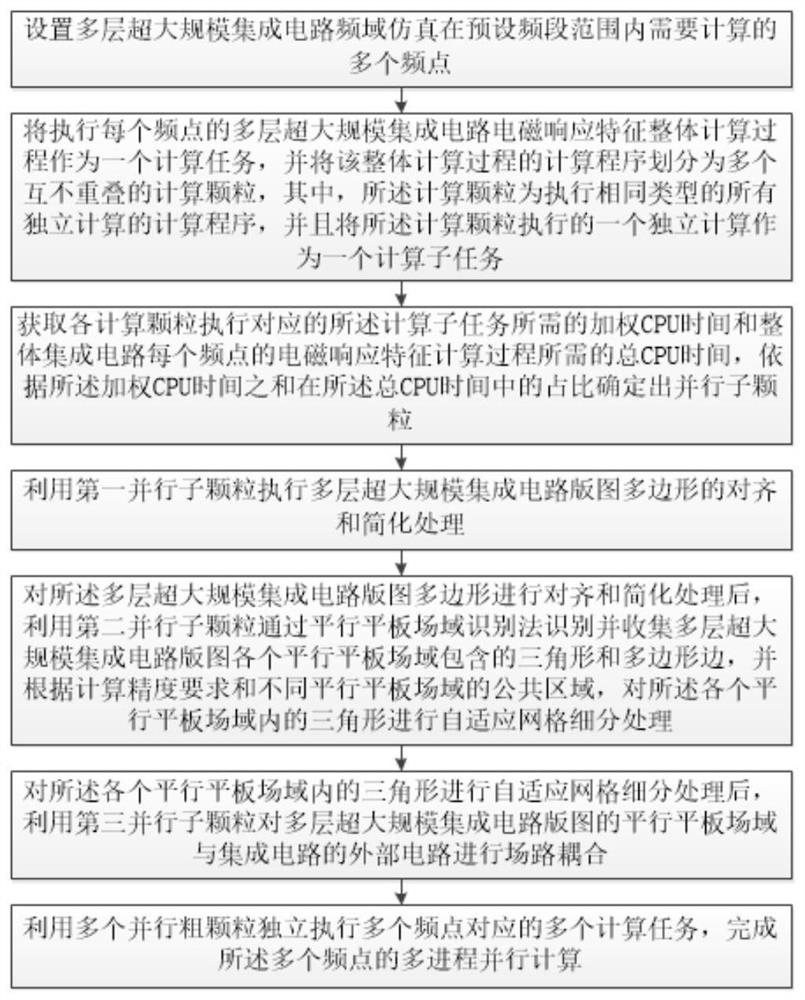

Integrated circuit electromagnetic response calculation method and device based on multi-level parallel strategy

A technology of integrated circuits and large-scale integrated circuits, which is applied in CAD circuit design, special data processing applications, etc., can solve the problem of difficult to meet the computational efficiency of multi-layer ultra-large-scale integrated circuits in frequency domain simulation, the reduction of parallel computing efficiency, and the low parallel computing efficiency. And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

[0167] The supernode voltage vector is a vector formed by each supernode reference node voltage;

[0168] The supernode current vector is a vector composed of the sum of all currents flowing into each supernode;

[0169] The length of the voltage vector of the non-reference node is the number of all non-reference nodes, and its i-th element P i is the potential of non-reference node i to its reference node, which is the sum of the voltages of all ideal voltage source branches on the path from non-reference node i to its reference node;

[0170] The row of the mutual conductance matrix of the super node and the non-reference node corresponds to the super node, the column of the mutual conductance matrix of the super node and the non-reference node corresponds to the non-reference point, and the ith row of the super node and the non-reference node Element P of column j ij is the mutual conductance of supernode i and non-reference point j or the self-conduction of non-reference...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More