Method of manufacturing mark

A manufacturing method and marking technology, which are applied in the fields of semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., can solve the problems of marking function obstruction and inability to obtain marking signals.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

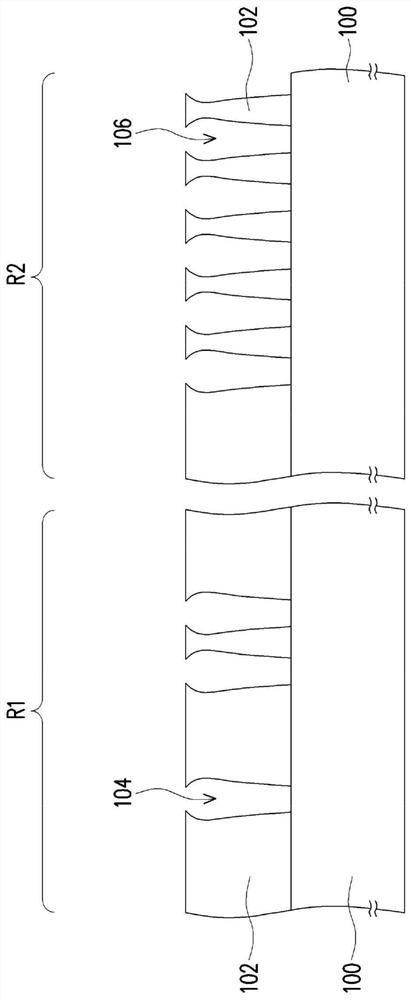

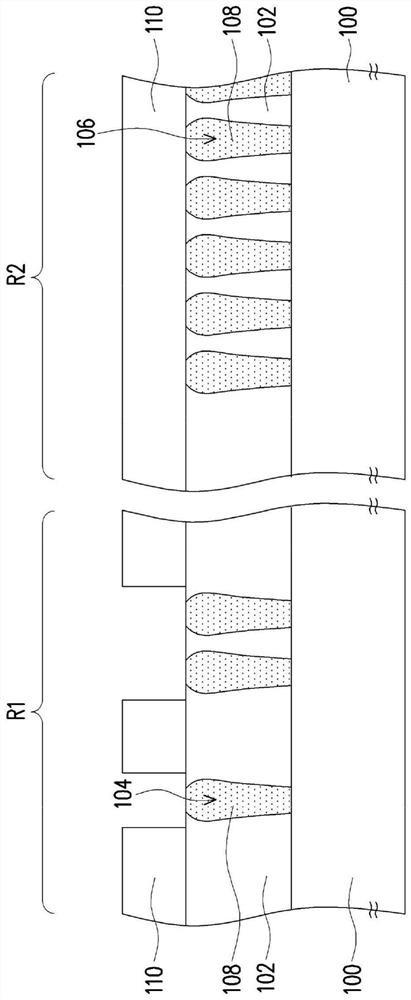

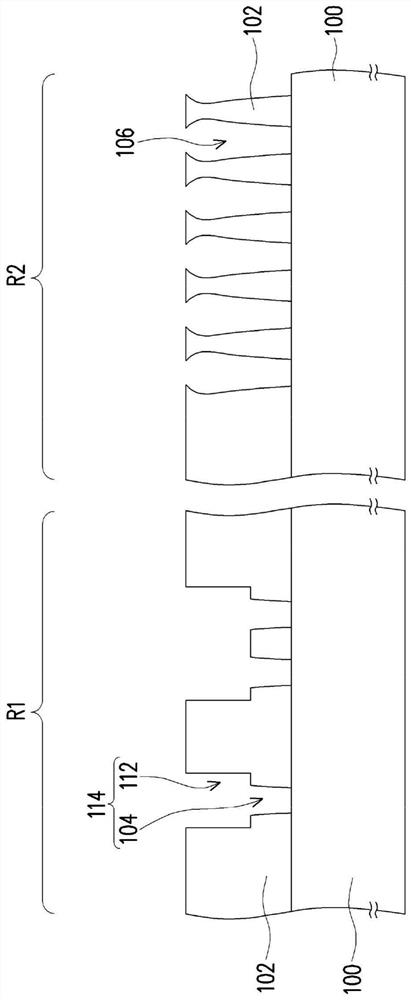

[0042]Please refer toFigure 1A , Provide substrate 100. The substrate 100 includes a device region R1 and a marking region R2. The element region R1 can be used to form various semiconductor elements. For example, the element region R1 may be a memory cell region, but the invention is not limited to this. In addition, the mark area R2 can be used to form marks such as alignment marks or overlapping marks.

[0043]The substrate 100 may include a semiconductor substrate (eg, a silicon substrate), but the invention is not limited thereto. In some embodiments, the substrate 100 may further include a semiconductor element (eg, a transistor) and a dielectric layer formed on the semiconductor substrate. In FIG. 1, the substrate 100 is shown as a single-layer structure to simplify the description.

[0044]Next, a dielectric layer 102 is formed on the substrate 100. The material of the dielectric layer 102 is silicon oxide, for example. The formation method of the dielectric layer 102 is, for exam...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More