Design method of on-chip photonic device based on appearance contour regulation and control

A technology of photonic devices and design methods, applied in design optimization/simulation, instruments, calculations, etc., can solve problems such as inability to meet wider bandwidth, limit device design dimensions, high error tolerance, etc., to expand design methods and design dimensions , small size design goals, and the effect of high error tolerance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The preferred embodiments of the present invention will be further described in detail below.

[0033] A silicon structure design of an on-chip optical power beam splitter is carried out on an insulator with a silicon thickness of 220 nm and a silicon dioxide thickness of 3 μm, which includes the following steps:

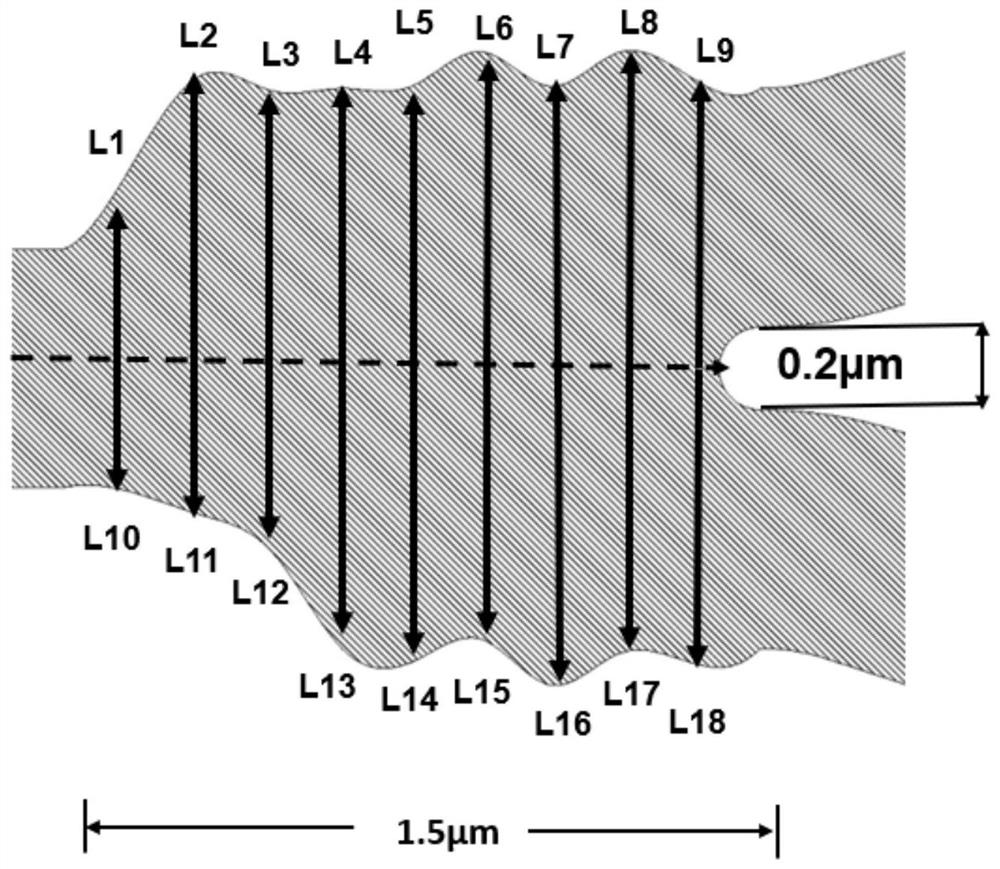

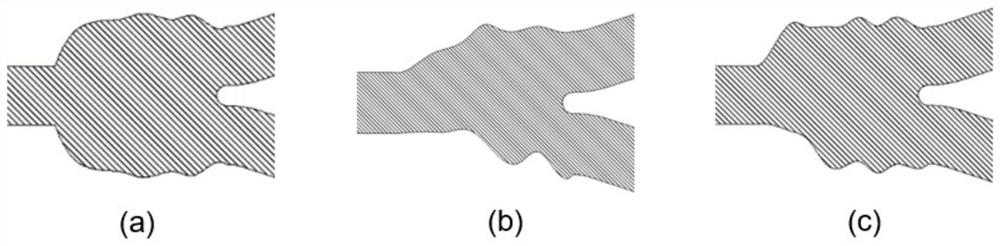

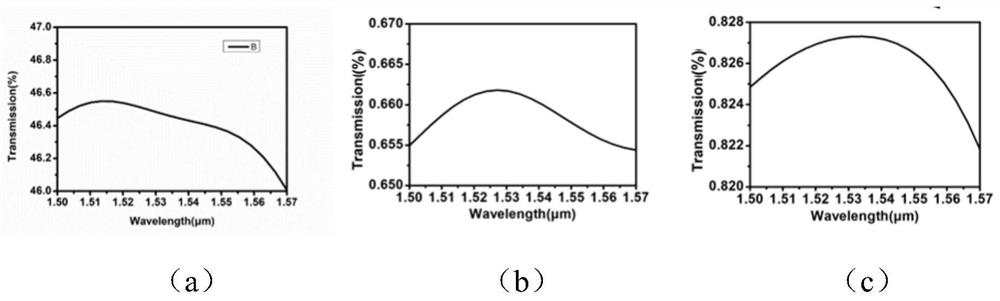

[0034] Step S1: Determine the function of the on-chip photonic device to be designed, the design target and the design area of the outline. The device is one-port input, two-port output, and the waveguide width is 0.5 μm; the function is to split the input light in different proportions at the two output ports; the design goal is that the output spectral lines of the two ports are between 1500nm- The 1570nm band is flat and the sum of the output optical power of the two ports reaches more than 90% of the input optical power; the area to be designed is an area with a length of 1.5 μm between the input and output ports.

[0035] Step S2: Establish a rectangu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More