FPGA-based speed filter algorithm

A filter and filter bank technology, applied in the direction of instruments, radio wave measurement systems, etc., can solve the problems of high cost, small space, high resource requirements, etc., to reduce resource consumption, save multiplier resources, and easy to implement Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

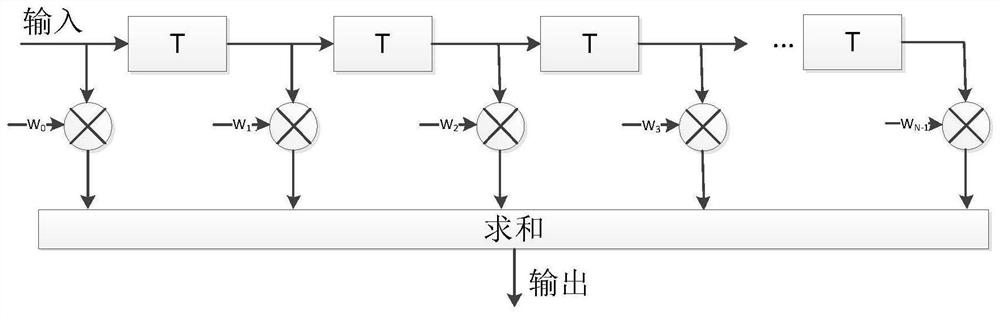

Method used

Image

Examples

Embodiment

[0034] The speed filter algorithm based on FPGA that the present embodiment provides, comprises the following steps:

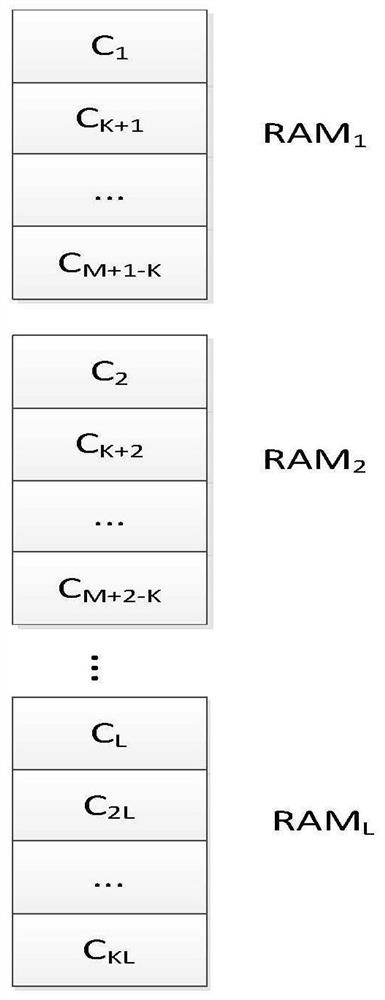

[0035] 1) When the system is initialized, the filter bank coefficients applicable to the current application scenario are bound to the on-chip RAM of the FPGA. Assuming that there are M speed units and the times of multiplexing in time is K, then M / K filter banks are required, and each filter bank is responsible for K sets of filter coefficients.

[0036] Such as figure 2 As shown in, RAM1 contains K sets of filter coefficients, and C1 contains A total of N coefficients correspond to an N-order filter.

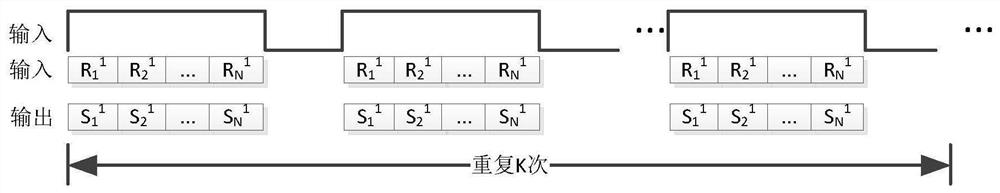

[0037] 2) After the radar echo data has undergone pulse compression, it is necessary to store the data of a pulse group first, trigger the read operation when the storage is completed, read the data according to a certain address rule, and put the same distance units of different pulses together, which is convenient for follow-up speed filter.

[0038] s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More