Chip testing method and device, processor chip and server

A chip testing and chip technology, applied in the field of chip automatic testing, can solve the problems of prolonging the chip testing cycle, multi-time cost, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0026] It should be clear that the described embodiments are only some of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

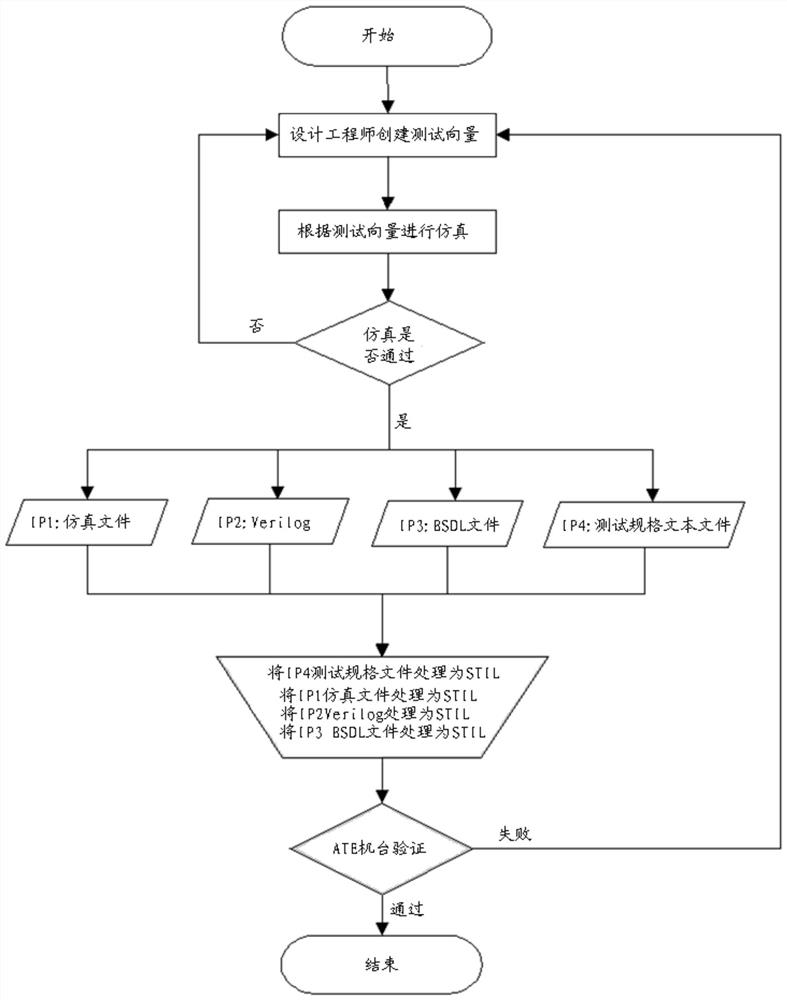

[0027] figure 1 shows a chip testing method, such as figure 1 As shown, when the ATE test on the chip based on the ATE vector fails, the ATE vector needs to be recreated, then simulated, and the test engineer obtains the STIL vector file that ATE can use based on the ATE vector. In this process, the design engineer responsible for generating ATE vectors and the test engineer responsible for ATE testing can only work serially, and the working conditions are highly dependent, which is not conducive to compressing the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More