Method and device for realizing sparse matrix multiplication on reconfigurable processor array

A processor array and sparse matrix technology, which is applied in the fields of electrical digital data processing, digital data processing components, instruments, etc., can solve problems such as increased power consumption, and achieve the effect of efficient implementation and reduction of configuration times and memory access times.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention more clear, the embodiments of the present invention will be further described in detail below in conjunction with the accompanying drawings. Here, the exemplary embodiments and descriptions of the present invention are used to explain the present invention, but not to limit the present invention.

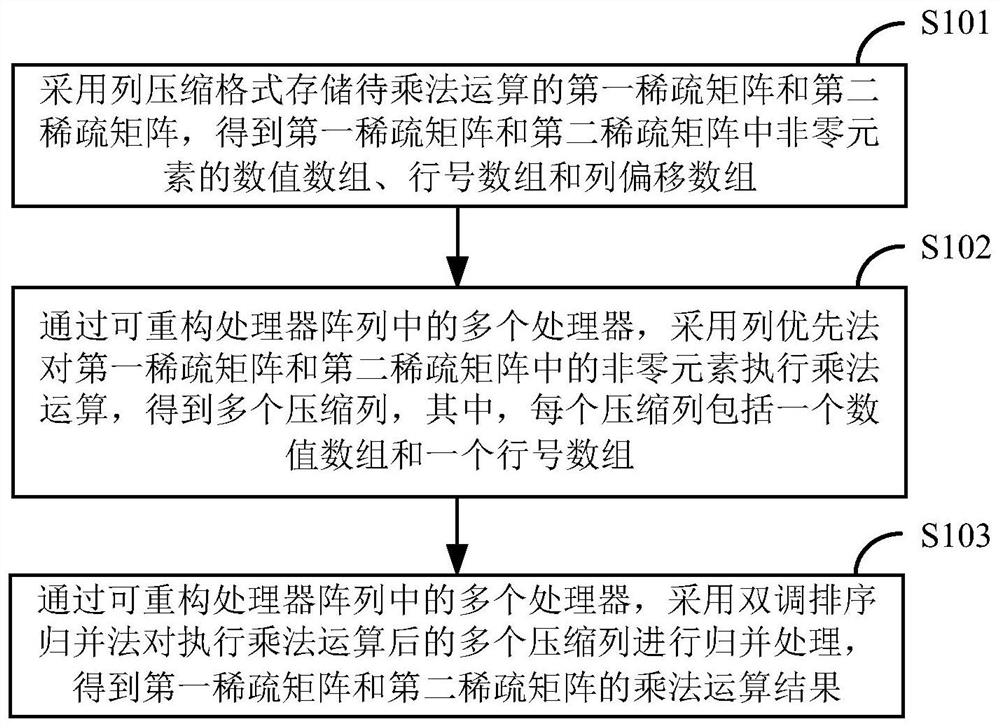

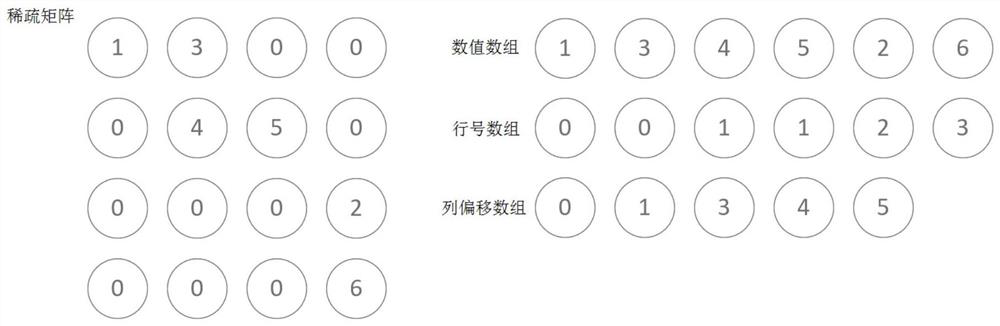

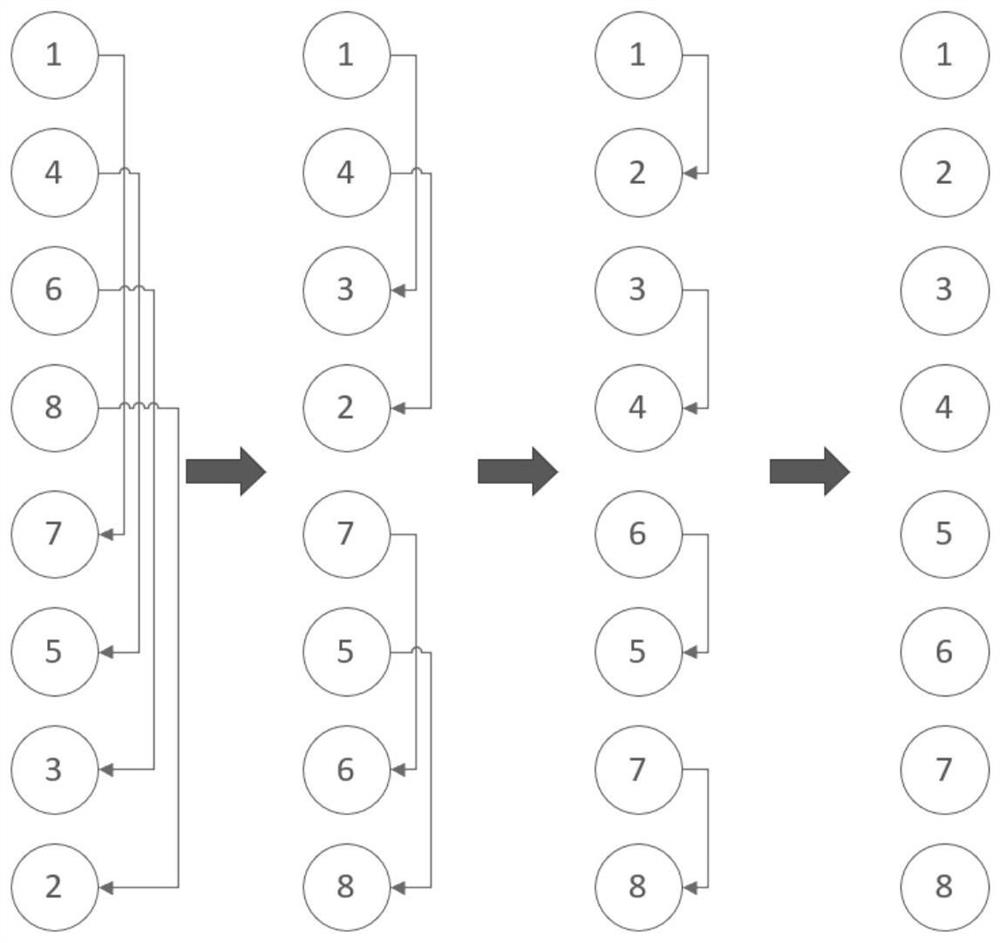

[0026] Since the operation unit of the reconfigurable processing array supports operations such as addition, multiplication, multiply-accumulate, and selection, the operation unit can perform parallel calculations. Therefore, in order to improve the operation efficiency of sparse matrix multiplication, an embodiment of the present invention provides a sparse matrix multiplication The implementation method on the reconfigurable processor array, compared with the traditional matrix multiplication operation, can make full use of the pipeline and parallel calculation of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More