Server boards for uniprocessor systems

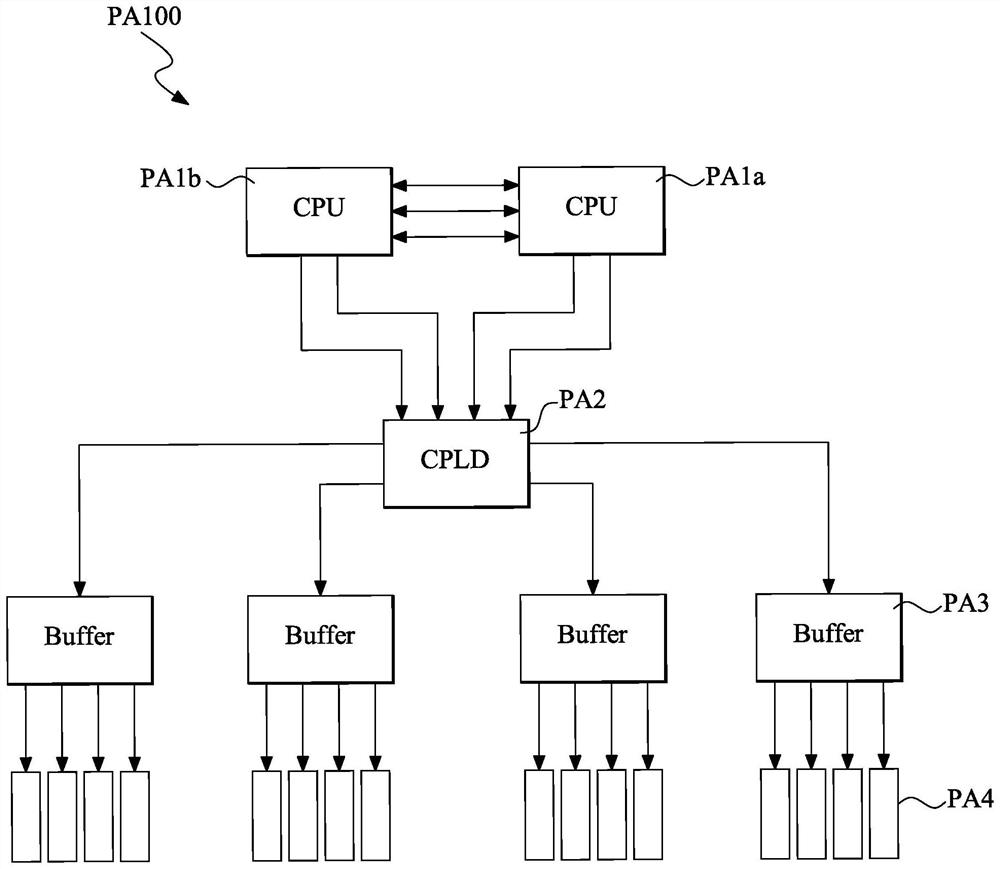

A processor system and server technology, applied in the architecture with a single central processing unit, electrical digital data processing, instruments, etc., can solve performance waste, falsely trigger board management controller reset operation, dual processor system Problems such as PA100 not working properly

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

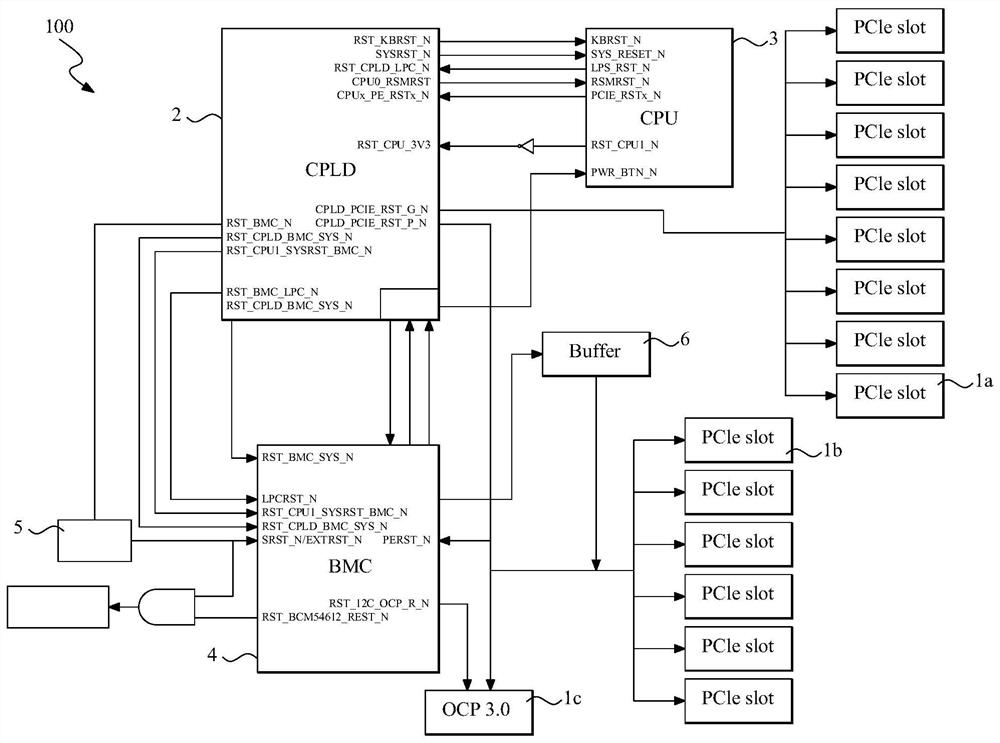

[0039] see figure 2 , figure 2 It is a signal transmission circuit diagram of the server main board of the single processor system provided by the preferred embodiment of the present invention. Such as figure 2 As shown, a server motherboard 100 of a single processor system includes eight PCIe (Peripheral Component Interconnect Express) ports 1a (only one is marked in the figure), six PCIe ports 1b (only one is marked in the figure), a PCIe port 1c, a complex programmable logic device (Complex ProgrammableLogic Device, CPLD) 2, a central processing unit (Central Processing Unit, CPU) 3, a baseboard management controller (Board Management Controller, BMC) 4, an isolation circuit 5 and - Buffer (Buffer)6.

[0040] The PCIe ports 1a, 1b, and 1c are used to install at least one PCIe device; wherein, the PCIe ports 1a, 1b in this embodiment are PCIe slots (PCIe slots), and the PCIe port 1c is a network card port (OCP 3.0).

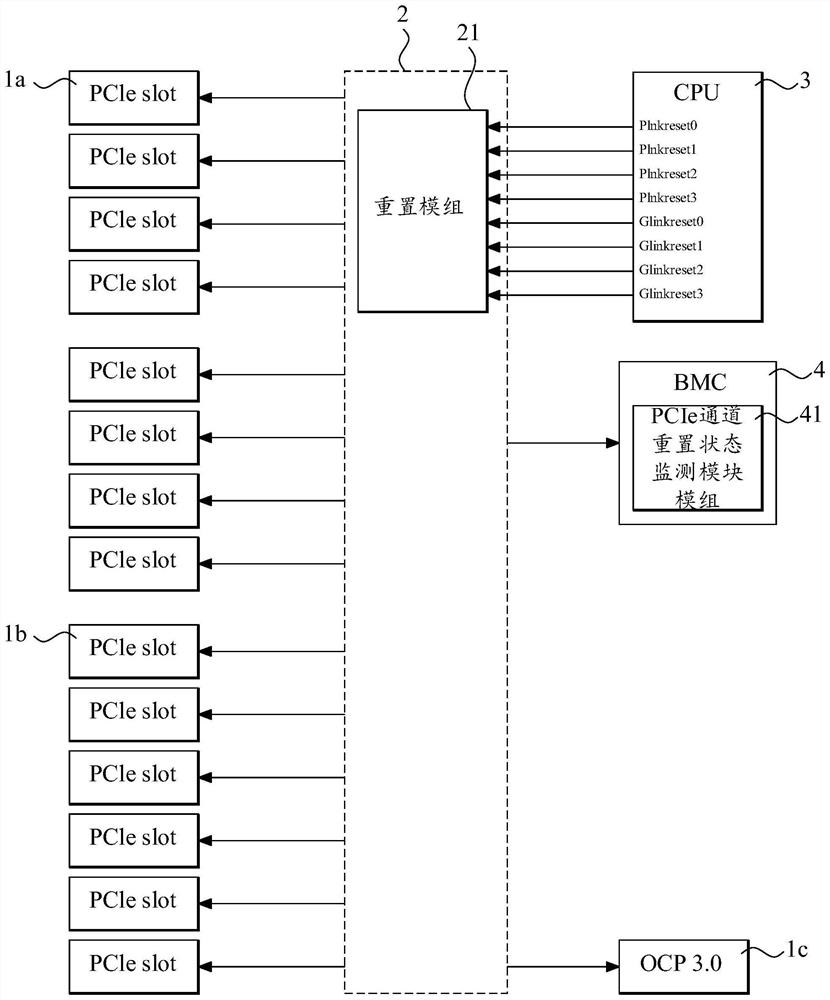

[0041] read on image 3 , image 3 It is a schem...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More