SoC dual-core system clock synchronization method and device

A system clock and clock synchronization technology, applied in the direction of generating/distributing signals, etc., can solve the problems of the impact of product punctuality accuracy and the inability of the management core to save the system clock, so as to avoid clock asynchrony and ensure punctuality accuracy.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

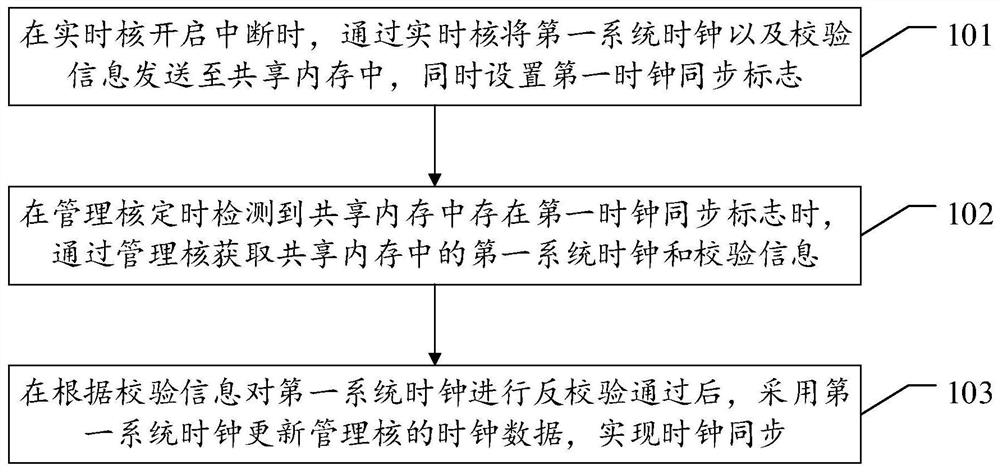

[0040] For ease of understanding, see figure 1 , Embodiment 1 of a SoC dual-core system clock synchronization method provided by the present application includes:

[0041] Step 101 , when the real-time core enables interrupts, send the first system clock and verification information to the shared memory through the real-time core, and set a first clock synchronization flag at the same time.

[0042] Shared memory is a memory that both the real-time core and the management core can access. It can be set in advance as needed, and is mainly used to store information such as clocks and related signs during the clock synchronization process. The verification information not only includes the information obtained by checking the first system clock in real time, but also includes verification mode information, which is convenient for management and verification of anti-verification. The clock synchronization flag provides different states according to whether the synchronization is ...

Embodiment 2

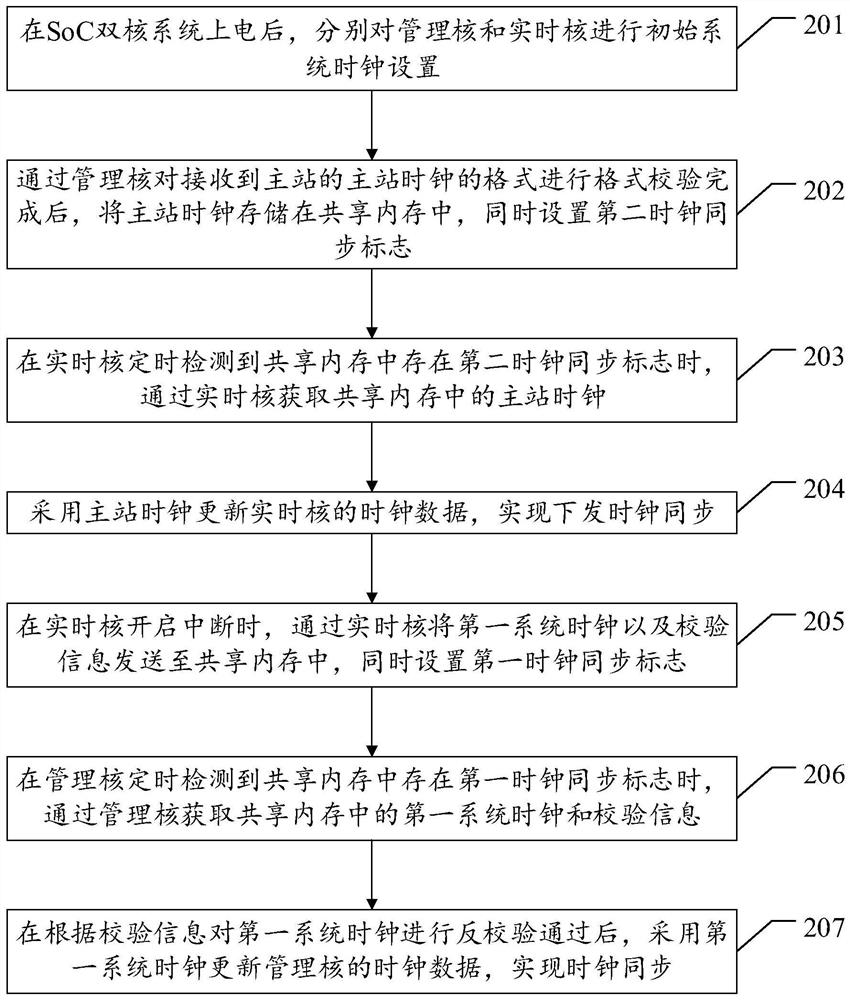

[0051] For ease of understanding, see figure 2 , the present application provides a second embodiment of a SoC dual-core system clock synchronization method, including:

[0052] Step 201 , after the SoC dual-core system is powered on, perform initial system clock settings for the management core and the real-time core respectively.

[0053] The clock of the management core is mainly provided by the real-time core, and the initial system clock setting process is no exception. The clock of the real-time core is provided by the RTC chip. The real-time core can obtain clock data from the RCT chip, but if the acquisition fails, the management core Linux is used. The system clock in the kernel updates the clocks of the real-time kernel and the RTC chip at the same time.

[0054] Further, step 201 includes:

[0055] The RTC clock obtained on the RTC chip is sent to the shared memory through the real-time core, so that the management core performs the initial system clock setting a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More