Integrated test board card, chip test system and chip test method

A technology of integrated testing and chip testing, which is applied in automated testing systems, electronic circuit testing, electrical measurement, etc., and can solve problems such as low testing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

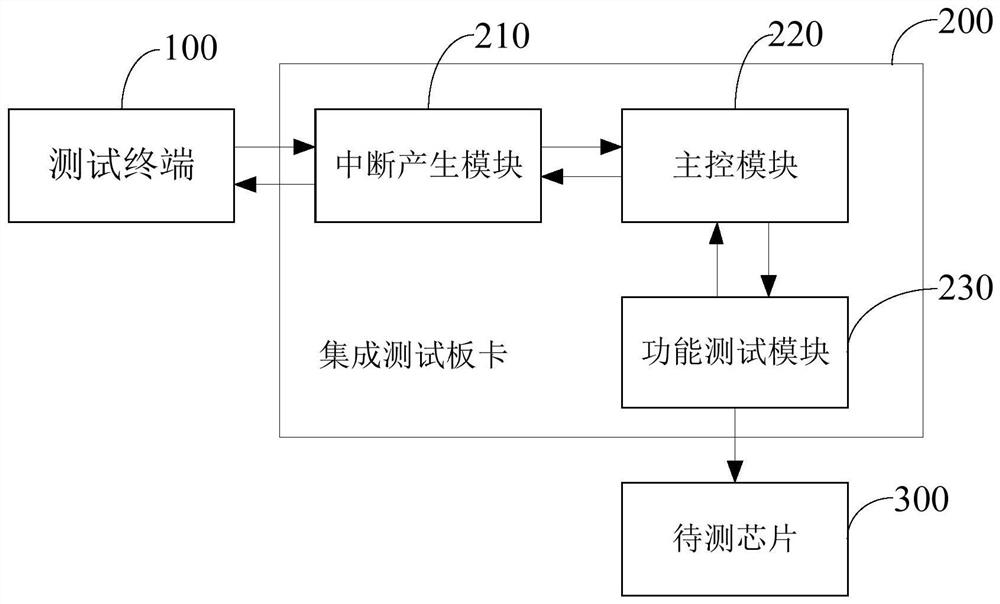

[0040] This embodiment provides an integrated test board 200 for testing the chip 300 to be tested. figure 1 The integrated test board 200 includes an interrupt generation module 210, a master module 220, and a functional test module 230.

[0041] Wherein, the interrupt generating module 210 is configured to generate a first interrupt trigger signal when the test command is received by the test terminal 100;

[0042] The master module 220 connects the interrupt generating module 210, in response to the first interrupt trigger signal, acquiring test parameter information corresponding to the test command, and configures the function test module 230 based on the test parameter information To test the function test module 230 for testing the standby chip 300, the test parameter information is stored in advance in the main control module;

[0043] The master module 220 is further configured to generate a response command after the function test module 230 is finished, and transmit the...

Embodiment 2

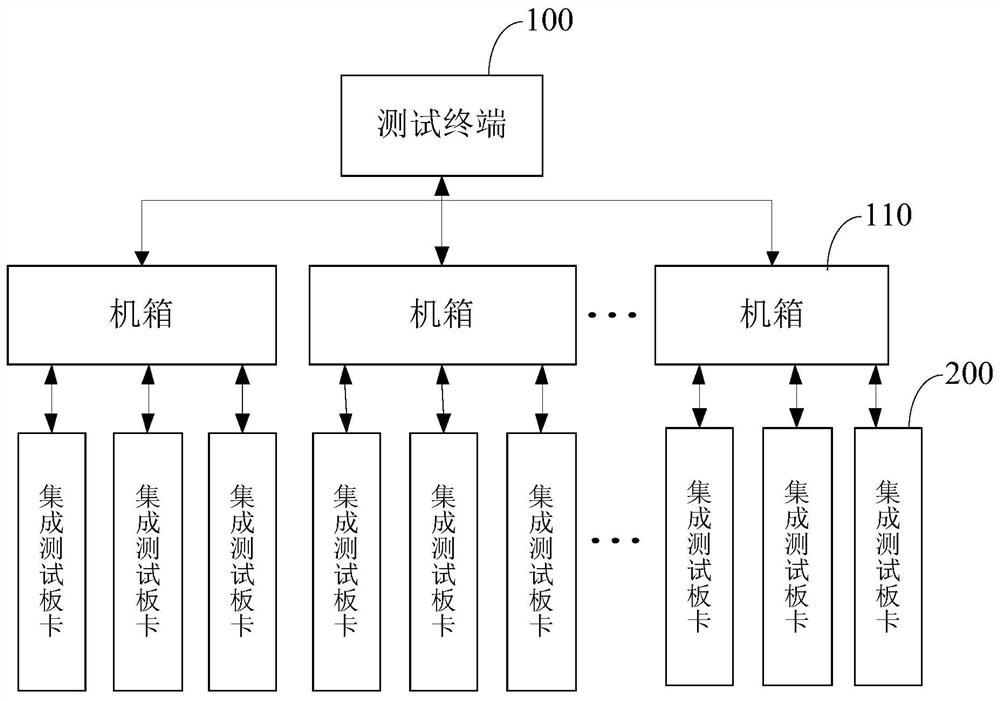

[0054] This embodiment provides a chip test system for testing the chip 300 to test, referring to figure 1 The chip test system includes a test terminal 100 and an integrated test board 200 provided by one embodiment, the test terminal 100 for generating a test instruction and transmitting the test instruction to the integrated test board 200, and When the second interrupt trigger signal is received, the test result is obtained.

[0055] Through the above chip test system, during the entire process of the test, the test terminal 100 only needs to issue a test instruction and after the test is triggered by the second interrupt trigger signal, replacing the traditional timing acquisition test data. In the way, avoid repeated unwanted acquisition operations, and the configuration test parameter information is directly from the integrated test board 200 to obtain the corresponding test parameter information according to the test instruction according to the test instruction, and does ...

Embodiment 3

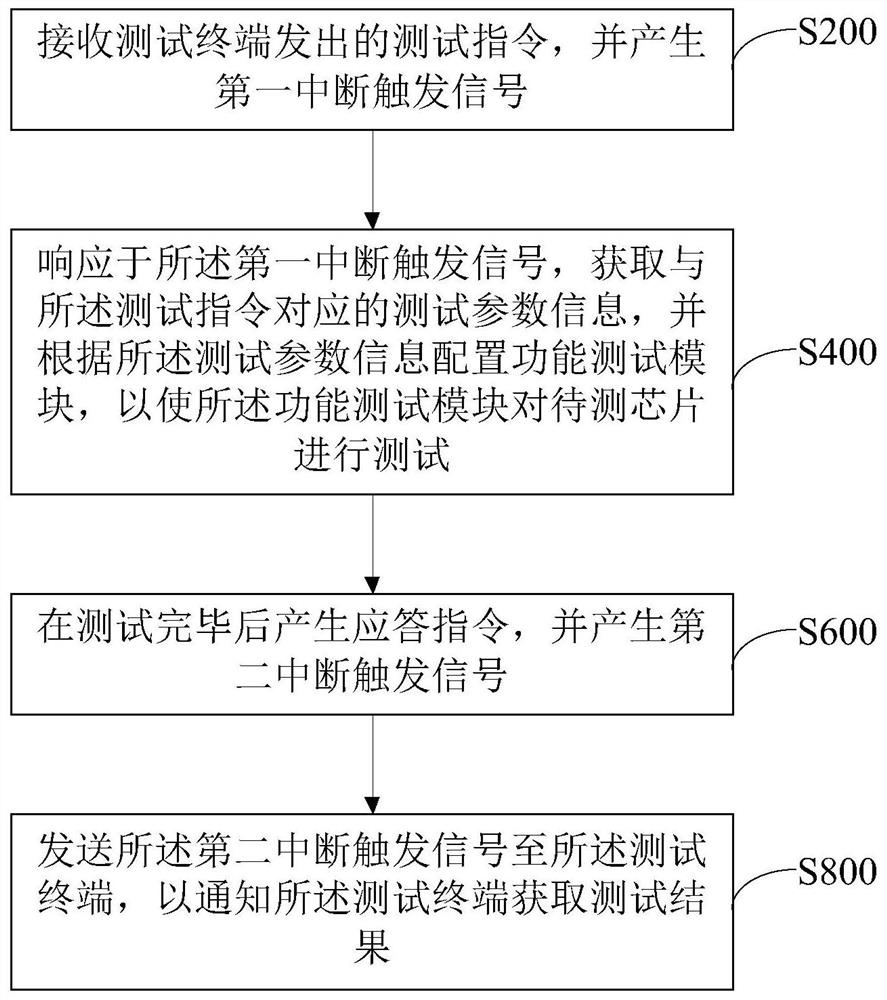

[0060] This embodiment provides a chip test method, applied to integrated test board 200, reference image 3 The chip test method includes the following steps:

[0061] Step S200, receive the test instruction emitted by the test terminal 100 and generate a first interrupt trigger signal;

[0062] In response to the first interrupt trigger signal, the test parameter information corresponding to the test command is acquired, and the function test module 230 is configured according to the test parameter information to enable the function test module 230 to be tested. 300 carry out testing;

[0063] Step S600, generate a response command after the test is completed, and generate a second interrupt trigger signal;

[0064] In step S800, the second interrupt trigger signal is transmitted to the test terminal 100 to inform the test terminal 100 to acquire test results.

[0065] Through the above chip test method, during the entire process of test, the test terminal 100 only needs to issue...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com