Aging circuit board, aging test structure and aging test method

A technology of aging test and aging circuit, which is applied in the direction of electronic circuit testing, printed circuit components, printed circuits connected with non-printed electrical components, etc., and can solve the problems of aging characteristics testing of small chip interconnection functions, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] In order to make the purpose, technical solution and advantages of the present application clearer, the present application will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present application, and are not intended to limit the present application.

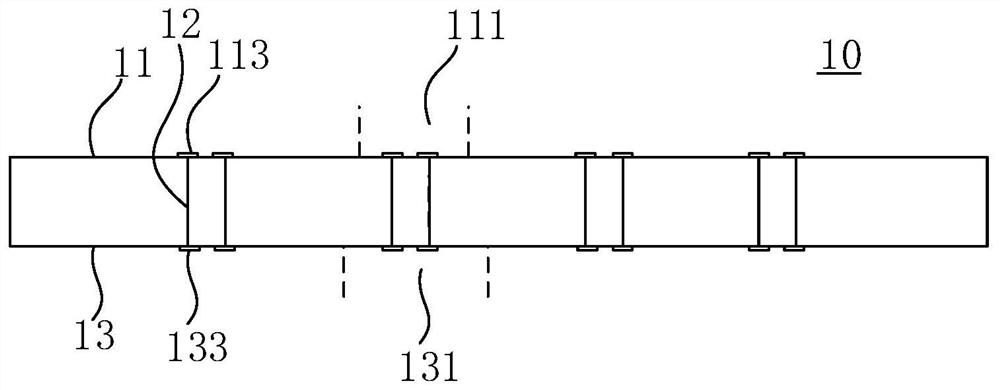

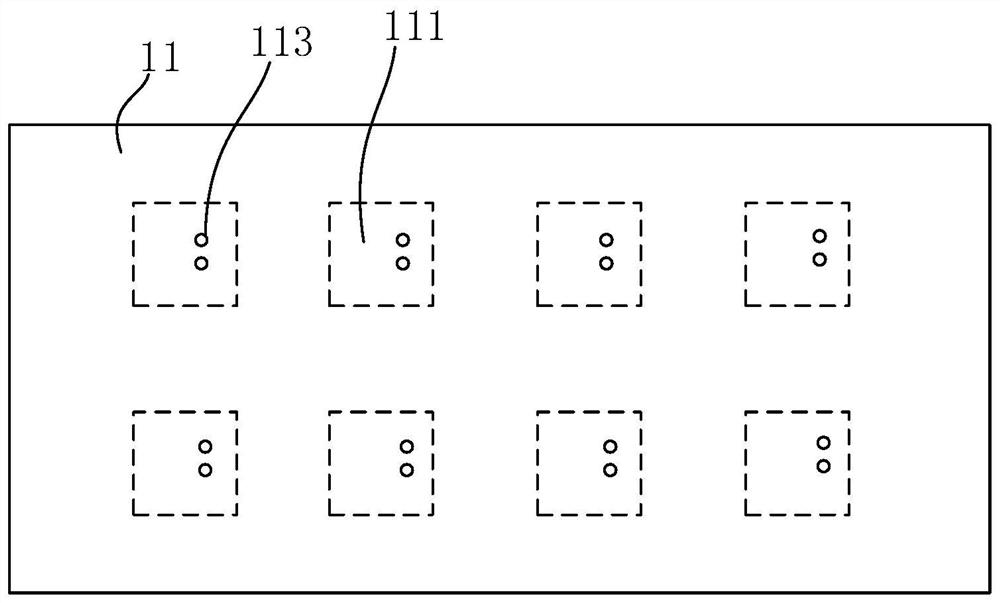

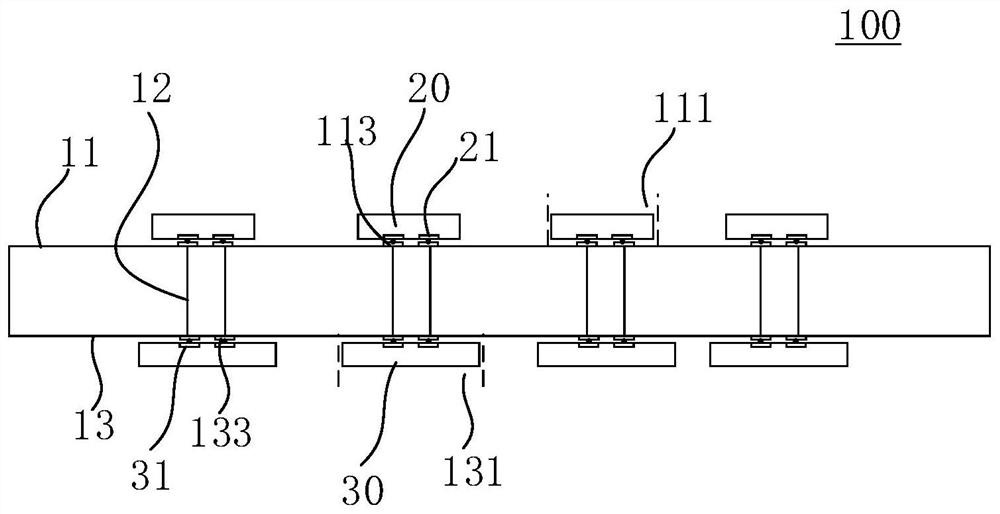

[0030] Please also refer to figure 1 and figure 2 , an embodiment of the present application provides an aging circuit board 10, which is used to perform aging tests on the aging characteristics of chips related to interconnection and the aging characteristics of interconnection functions between chips, for example, for integrated chips with a chiplet architecture. The "chiplets" involved and the interconnection function between the "chiplets" are subjected to burn-in tests.

[0031] It can be understood that since the material environment of the interconnection between...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More