Storage array circuit, storage array layout and verification method

A storage array and verification method technology, applied in the field of storage array circuits, can solve problems such as consistency verification

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

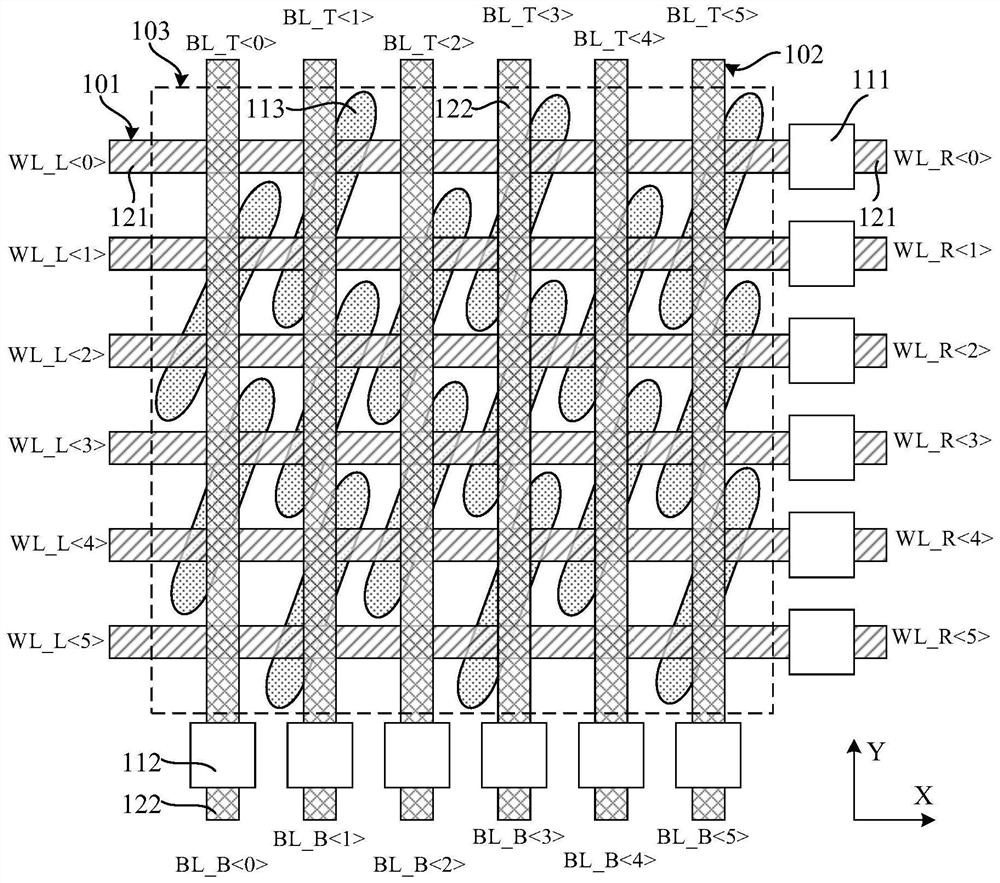

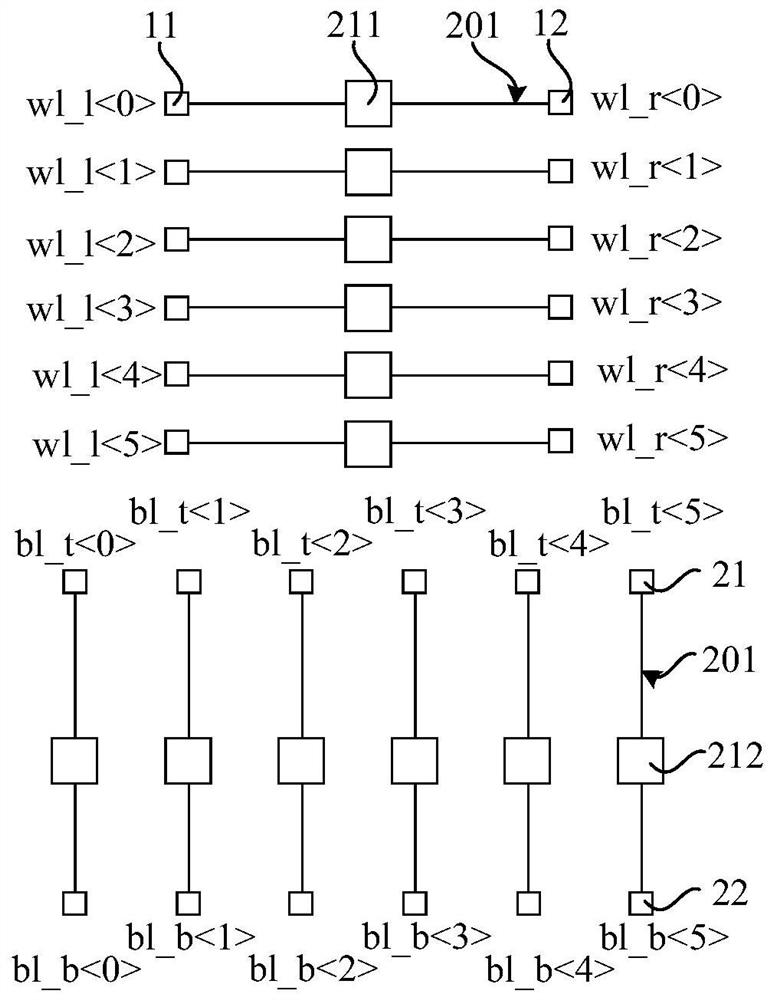

[0014] The storage array includes a plurality of intervalted word lines and a plurality of intervalted bit lines, and each word line is electrically connected to the corresponding word line drive circuit, each bit will be connected with the corresponding sense amplified circuit electricity connect. If the layout of the word line or bit line is an error, it will affect the electrical connection relationship in the storage array. Therefore, the word line layer and the bit line layer in the storage array layout are verified, which is conducive to improving the yield of the storage array.

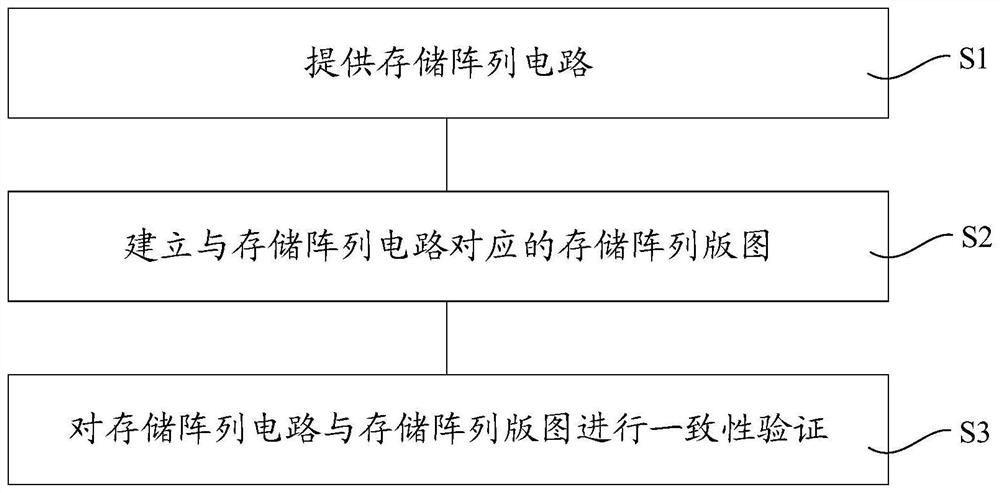

[0015] This application implementation provides a storage array layout that verifies the layout layout of the bit line layer and the word line layer using the storage array layout.

[0016] In order to make the objects, technical solutions, and advantages of the present application, various embodiments of the present application will be described in detail below with reference to the accompanying d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More