Visual target tracking system based on DSP + FPGA

A target tracking and vision technology, applied in the field of visual target tracking system

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The preferred examples of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the preferred examples described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

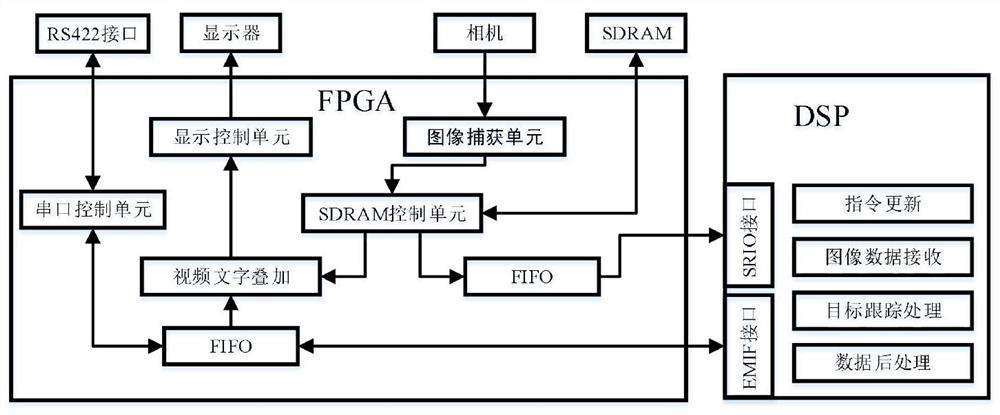

[0034] A kind of visual target tracking system based on DSP+FPGA described in the present invention, as figure 1 As shown, it mainly includes the following steps:

[0035] S1: Use the FPGA processor to control the timing of the serial port and video decoding chip to collect image data and receive serial port instructions;

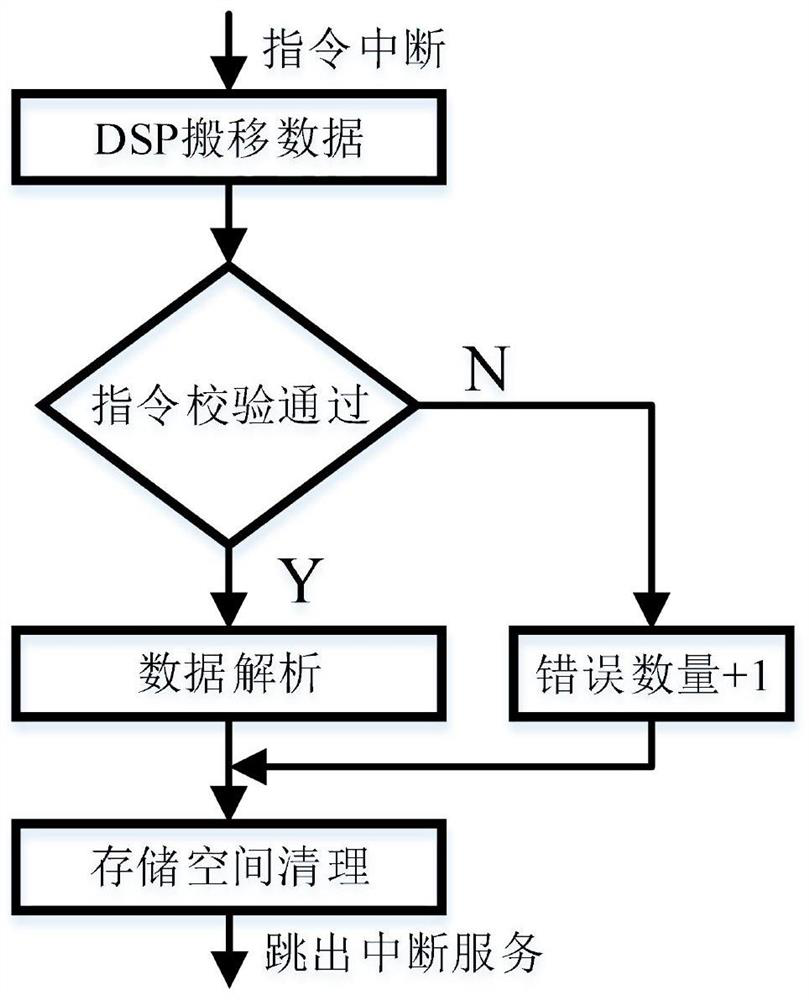

[0036] S1.1: FPGA realizes the reception of tracking command data by controlling the timing of the external serial port chip, writes the command data into the EMIF space of DSP in a transparent transmission mode, and triggers the corresponding GPIO pin interrupt of the DSP processor;

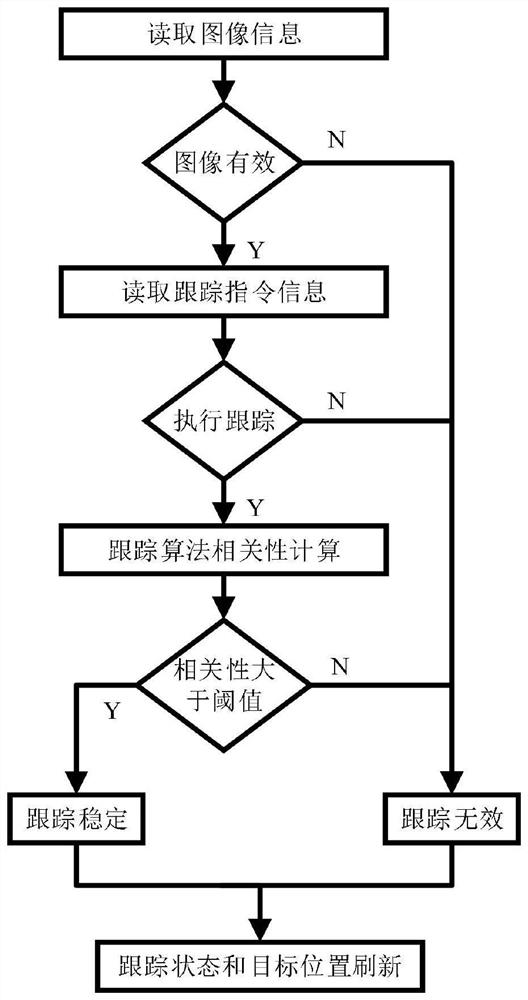

[0037] S1.2: FPGA controls the timing of the video decoding chip c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More