ZYNQ-based multi-channel DAC reference clock rapid synchronization system

A technology for synchronizing systems and reference clocks, applied in analog-to-digital converters, electrical components, code conversion, etc., can solve the problems of high logic resource occupancy, long debugging time, and large amount of logic resource calculations, and achieve real-time feedback, The effect of fast speed and reduced logic resource usage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

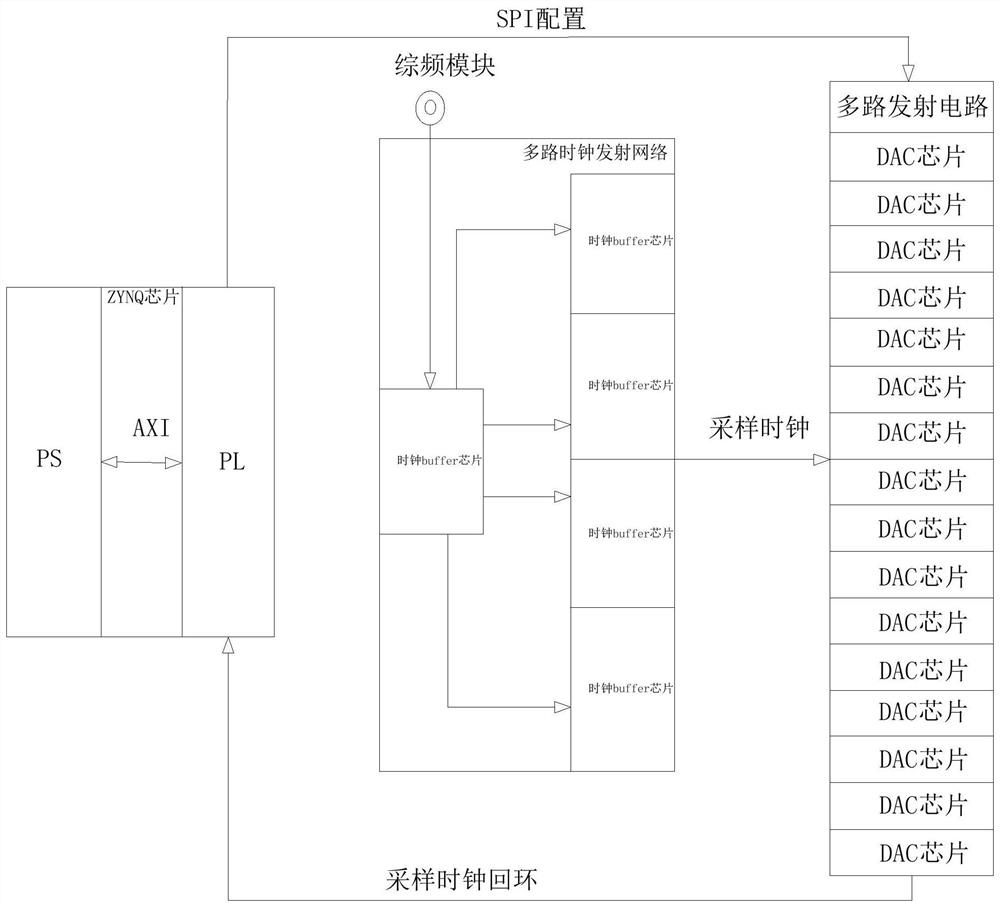

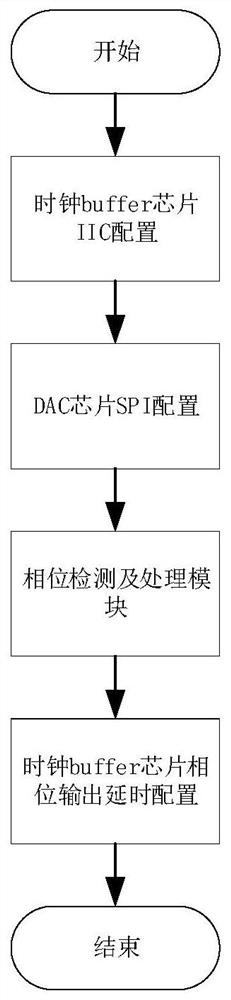

[0024] Such as figure 1 As shown, the present embodiment provides a reference clock fast synchronization system based on a ZYNQ multi-channel DAC, including a ZYNQ chip, at least one clock buffer chip, and a plurality of DAC chips, and the PL end and the PS end of the ZYNQ chip pass AXI bus interconnection, configure the clock buffer chip to generate the clock, configure the DAC chip to work in the sampling clock loopback to the PL end of the ZYNQ chip, and the PL end of the ZYNQ chip performs phase detection and phase processing on multiple reference clock signals to obtain the clock buffer chip The delay output configuration parameters are transmitted to the PS terminal through the AXI bus.

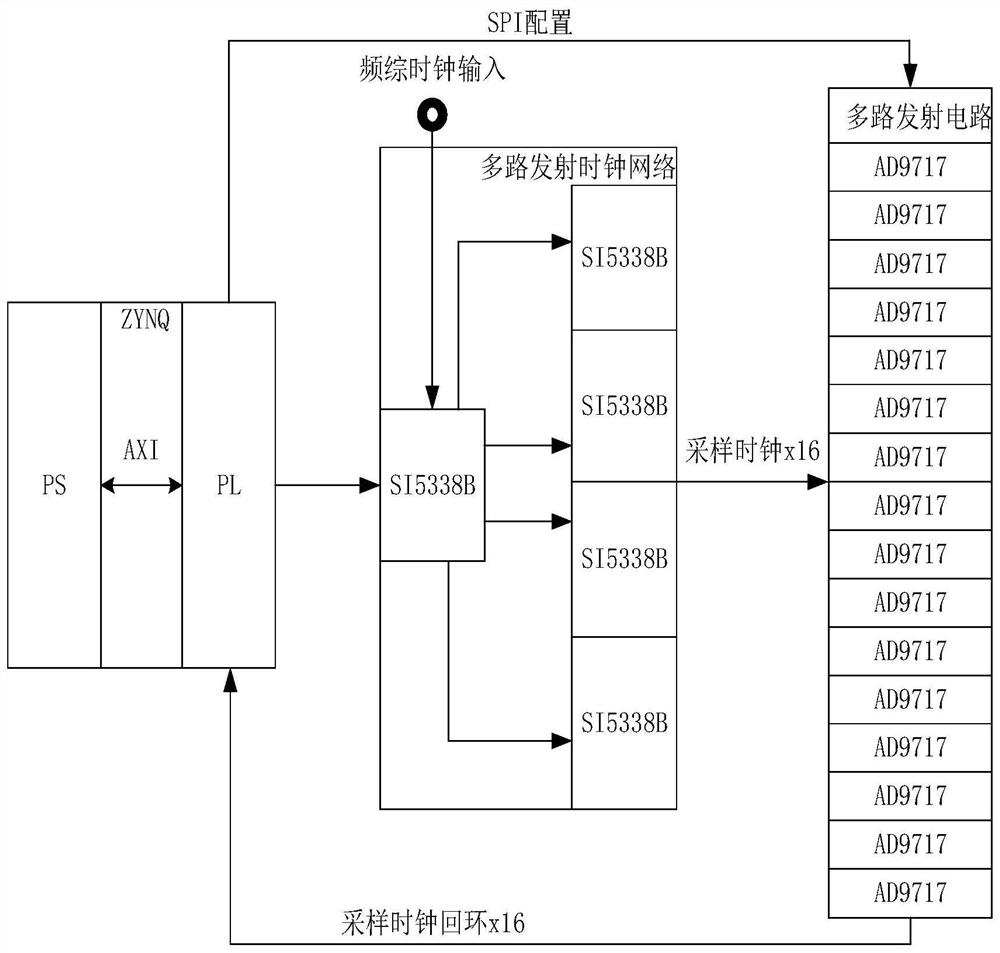

[0025] The present invention: reference figure 2 , the hardware design is mainly to solve the problem of the same source design of the clock, the ZYNQ chip model is XC7Z100-2FFG900I, the clock buffer chip selected in the multi-channel transmission clock network is SI5338B with output ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More