Chip packaging structure

A chip packaging structure, chip technology, applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve the problems of reliability risk, vertical size increase, etc., to save bonding gold wire, reduce the vertical size, avoid chip displacement bit effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

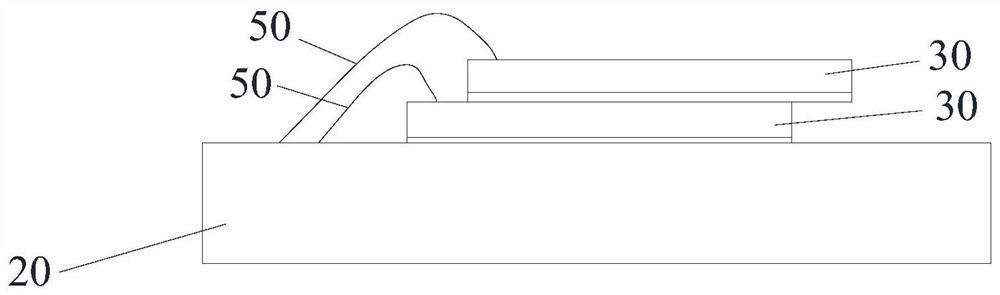

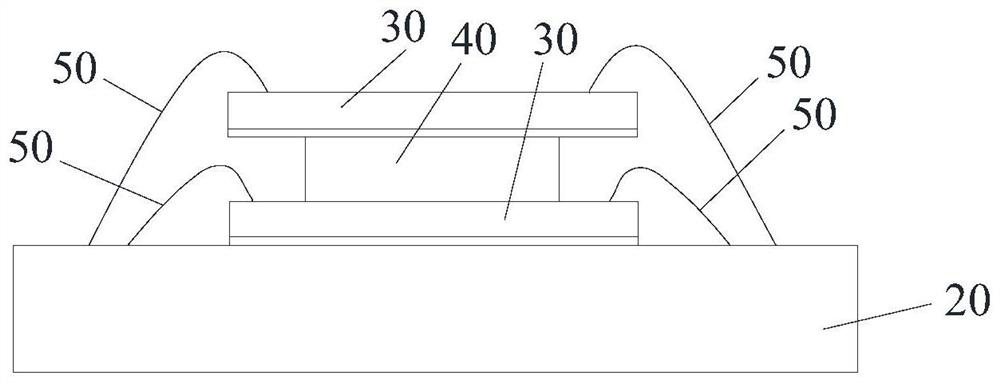

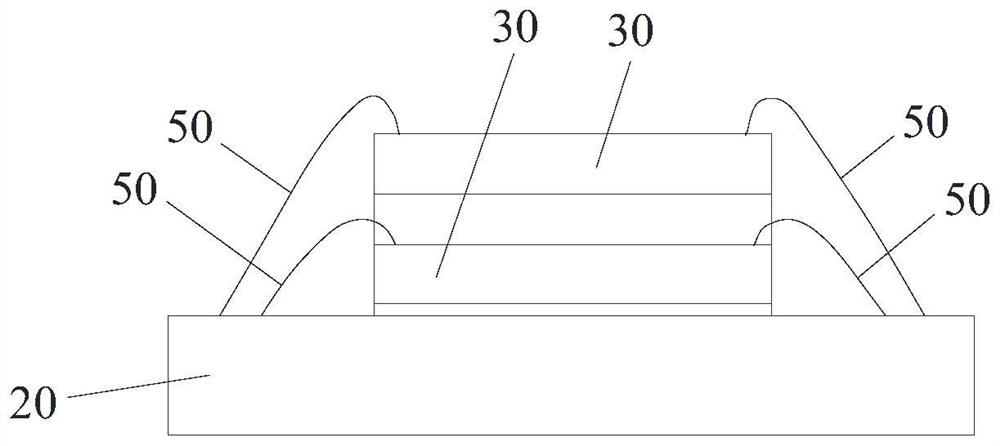

[0052] The following will clearly and completely describe the technical solutions in the embodiments of the present application with reference to the accompanying drawings in the embodiments of the present application. Obviously, the described embodiments are only part of the embodiments of the present application, not all of them. Based on the embodiments in this application, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the scope of protection of this application.

[0053] It should be noted that when an element is referred to as being “disposed on” another element, it may be directly on the other element or there may be another element in between. When an element is referred to as being "connected to" another element, it can be directly connected to the other element or it may be present intervening with the other element. The terms "vertical," "horizontal," "left," "right," and similar expressions are used ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More