Upper computer and FPGA high-speed data transmission architecture based on UDP protocol and implementation method

A technology of high-speed data transmission and transmission architecture, applied in the field of high-speed transmission, can solve the problems of redundancy, occupying a lot of resources, not supporting transmission protocols, etc., to achieve the effect of satisfying high-speed data transmission and improving data transmission speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to make the objectives, technical solutions and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and embodiments. It should be understood that the specific embodiments described herein are only used to explain the present invention, but not to limit the present invention.

[0034] On the contrary, the present invention covers any alternatives, modifications, equivalents and arrangements within the spirit and scope of the present invention as defined by the appended claims. Further, in order to give the public a better understanding of the present invention, some specific details are described in detail in the following detailed description of the present invention. The present invention can be fully understood by those skilled in the art without the description of these detailed parts.

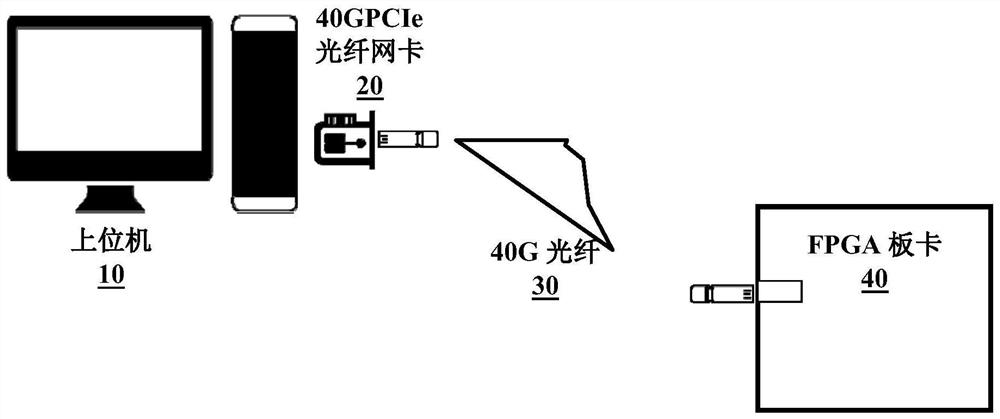

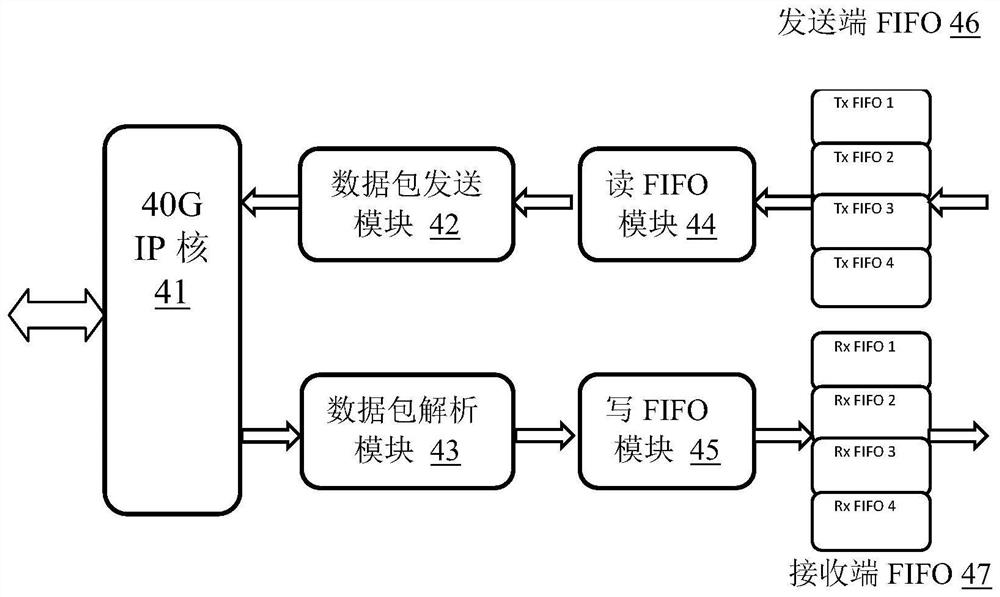

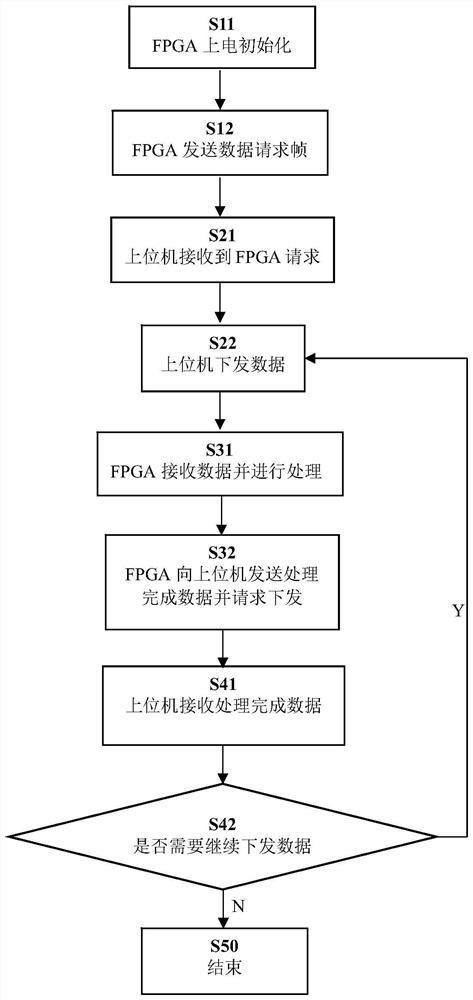

[0035] see figure 1 , 2 , the technical solution of the present inven...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More