Translation lookaside buffer (TLB) (mTLB) in process-specific memory for enhancing memory management unit (MMU) TLB for translating virtual addresses (VA) to physical addresses (PA) in processor-based systems

A memory management and central processing unit technology, applied in the field of memory management units, can solve problems such as large conversion overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

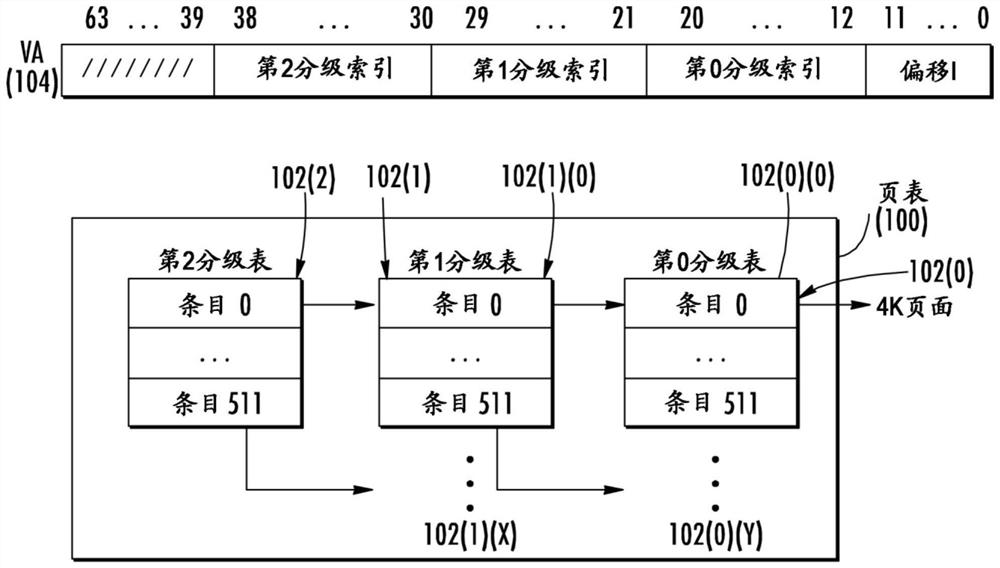

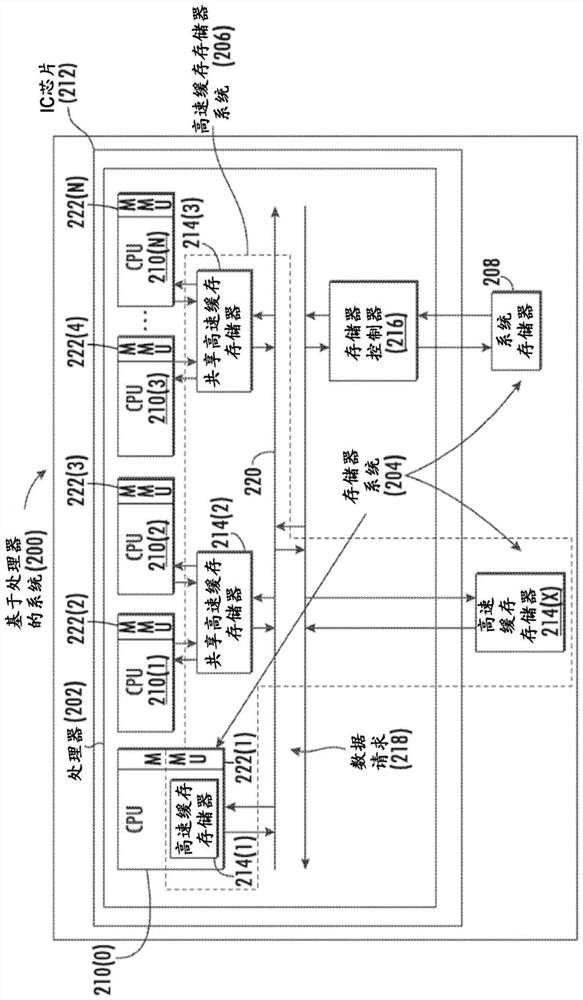

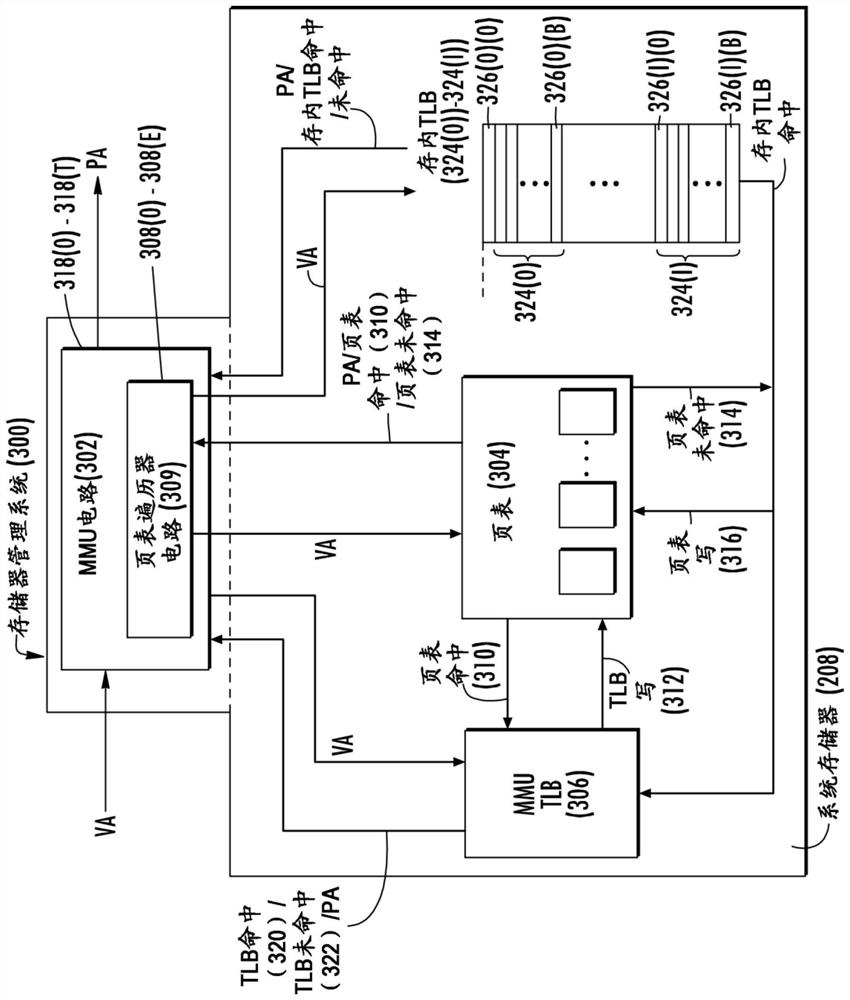

[0026] Aspects disclosed herein include a process-specific in-memory translation lookaside buffer ( TLB) (mTLB). A processor-based system includes a processor having one or more central processing units (CPUs), each central processing unit (CPU) configured to execute computer software instructions for a process. The processor-based system also includes a memory system including main physical memory addressable by the PA. A processor is a virtual memory system that employs virtual addressing to make the memory space available memory greater than the amount of physical memory space in the main system memory of the processor-based system. In some examples, each CPU is provided with a shared or dedicated MMU for converting VA to PA. The MMU is associated with a system in-memory TLB ("MMU TLB") and page tables (which are memory circuits). System memory is memory that is fully addressable by the PA space of a processor-based system. The MMU TLB is the cache memory associated wit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com