Stacked semiconductor device and method of manufacturing the same

A technology of semiconductors and oxide semiconductors, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., and can solve problems such as area reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

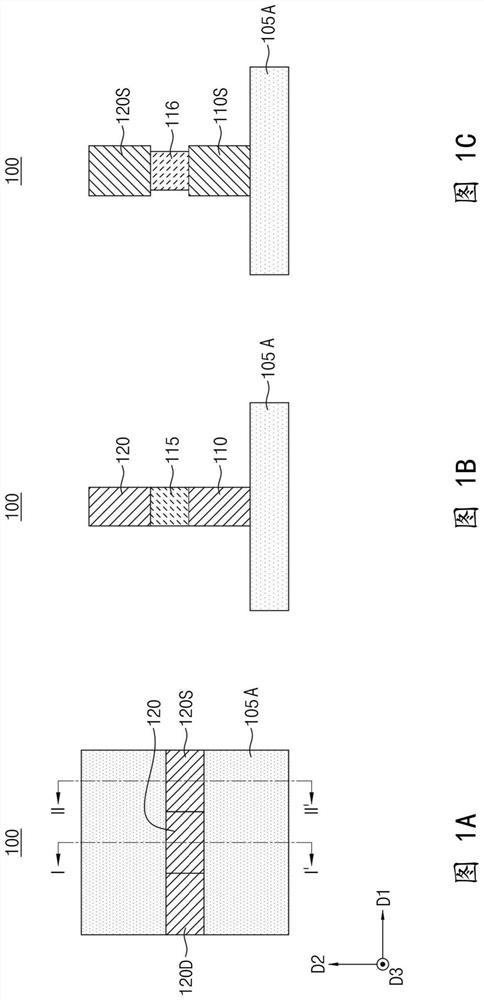

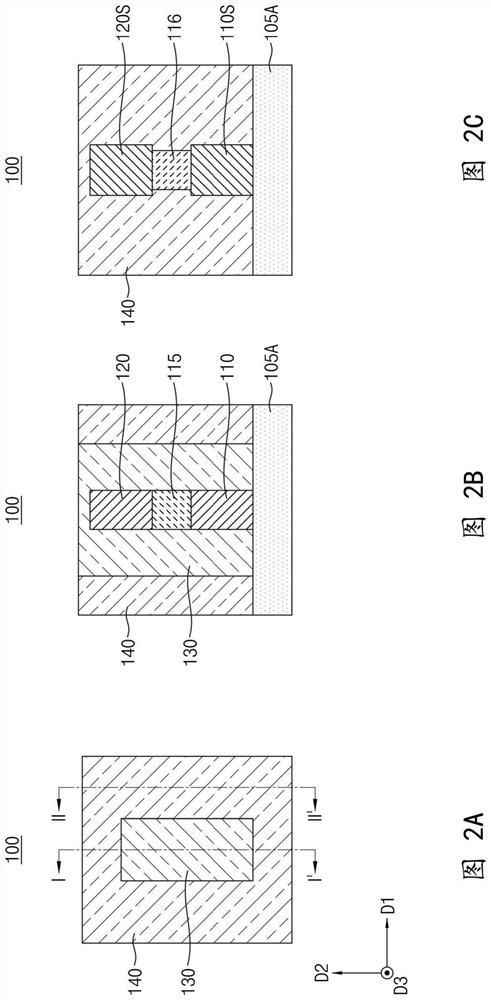

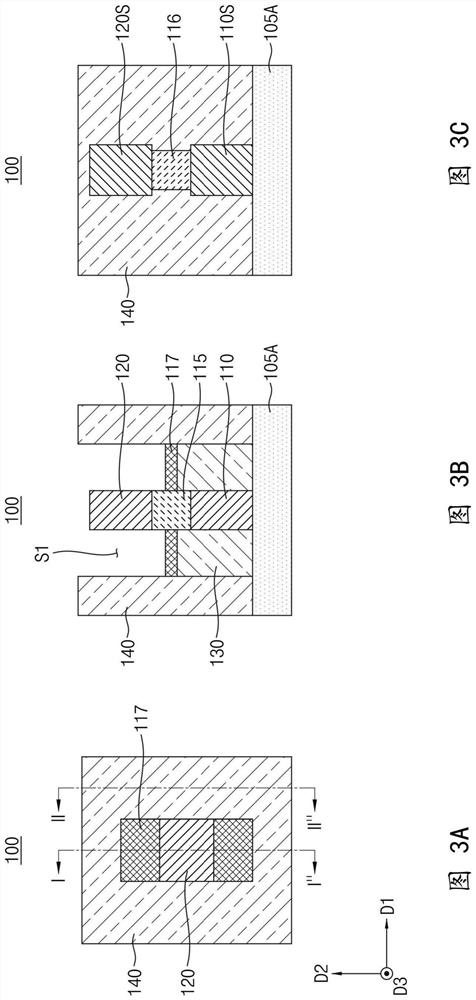

[0015] The embodiments described herein are all example embodiments, and thus, the inventive concept is not limited thereto and may be implemented in various other forms. It does not preclude that each embodiment provided in the following description is associated with one or more features of another example or another embodiment, also provided or not provided herein, but consistent with the inventive concept. For example, even if an item described in a particular example or implementation is not described in a different example or implementation, the matter may be construed as related to or in conjunction with that different example or implementation unless in the description mentioned additionally. Furthermore, it should be understood that all descriptions of the principles, aspects, examples, and embodiments of the inventive concept are intended to encompass both structural and functional equivalents thereof. Furthermore, these equivalents should be understood to include n...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com