Connection structure of CMOS double-row DUP and internal ESD device

A technology of ESD devices and connection structures, applied in semiconductor devices, electric solid devices, electrical components, etc., can solve problems such as waste and achieve the effect of improving utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

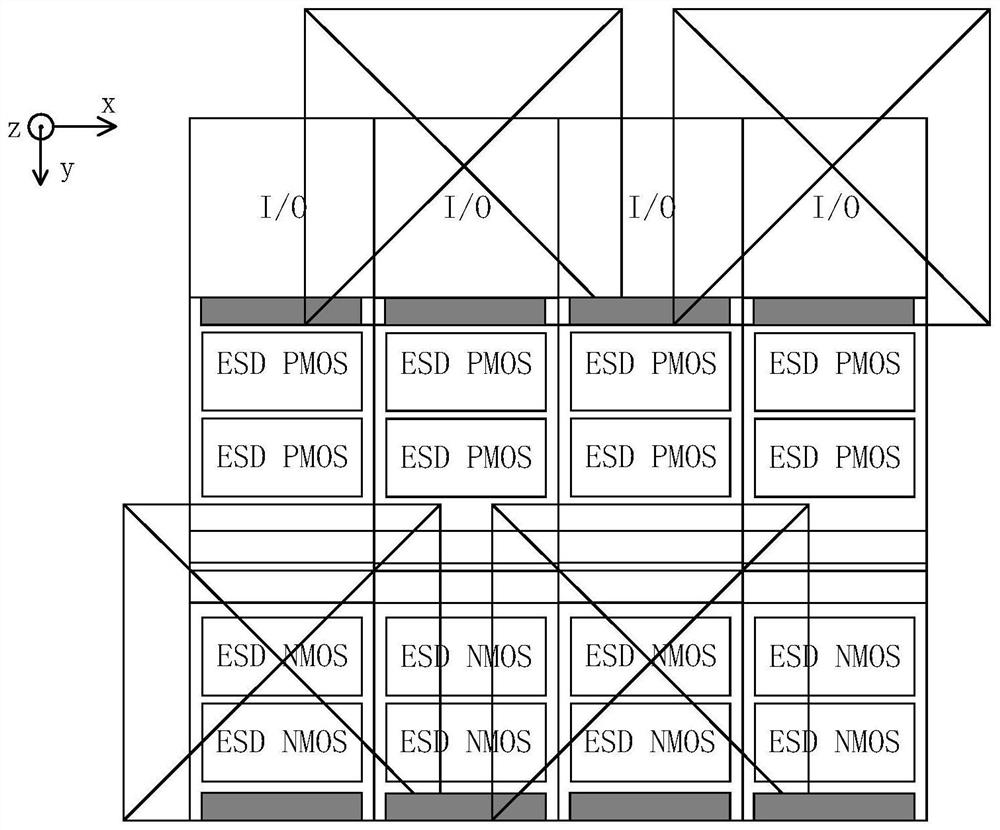

[0019] In the present invention, in the connection between the double-row DUP and the internal ESD device, a second metal interface is arranged between two ESD PMOS transistors arranged side by side up and down.

[0020] In the present invention, "first", "second" and "third" are all used to distinguish similar things, and have no meaning of order. The height mentioned in the present invention refers to the direction along the z-axis, and the width refers to the direction of the x-axis.

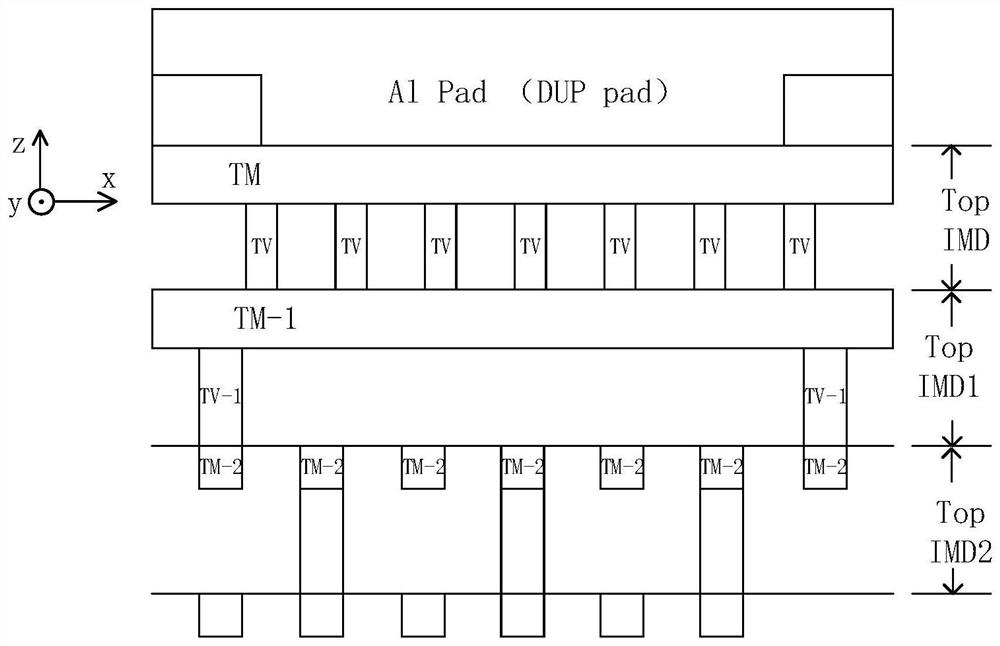

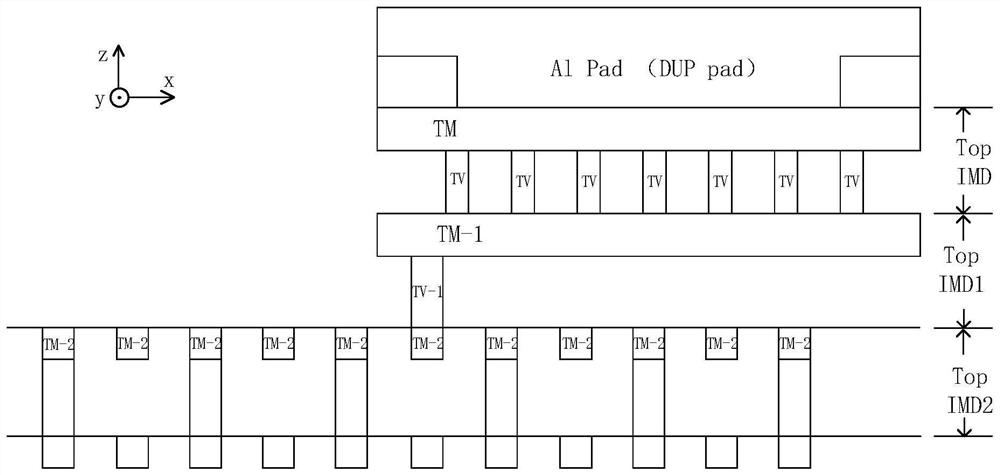

[0021] see image 3 , the metal layer of the PAD includes a TM layer and a TM-1 layer, the TM layer and the TM-1 layer are connected through a first through silicon via TV, and the TM-1 layer and another metal layer TM-2 layer are connected through a second Through silicon via TV-1 connection. The lowest metal layer of the PAD is the TM-1 layer, and the TM-2 layer is the device area, where the GPIO (not shown in the figure) is placed. IMD (inter metaldielectric) is a metal internal dielect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More