Address generating circuit

An address generation, circuit technology, used in electrical components, electronic switches, static memory, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

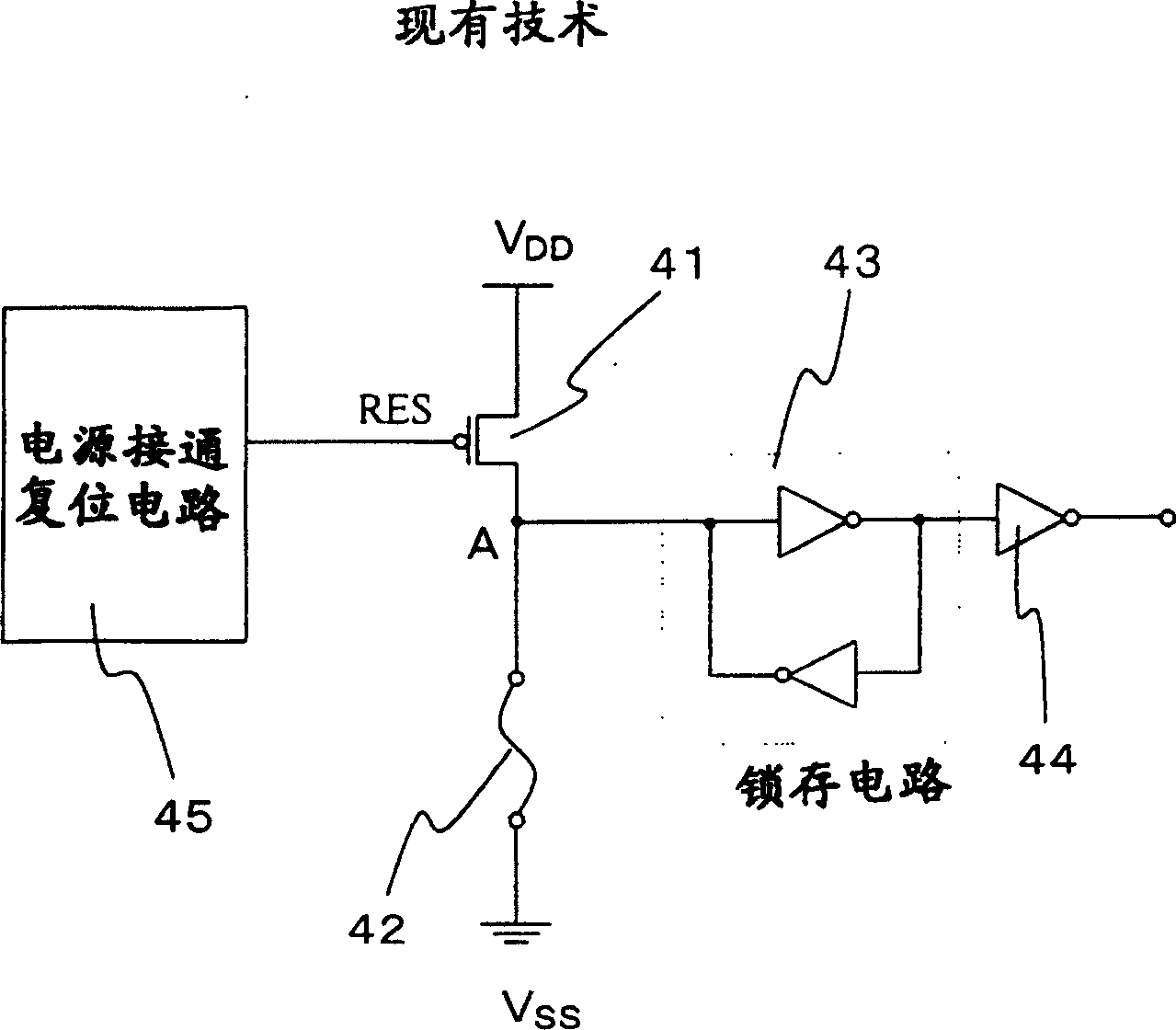

Problems solved by technology

Method used

Image

Examples

no. 1 example

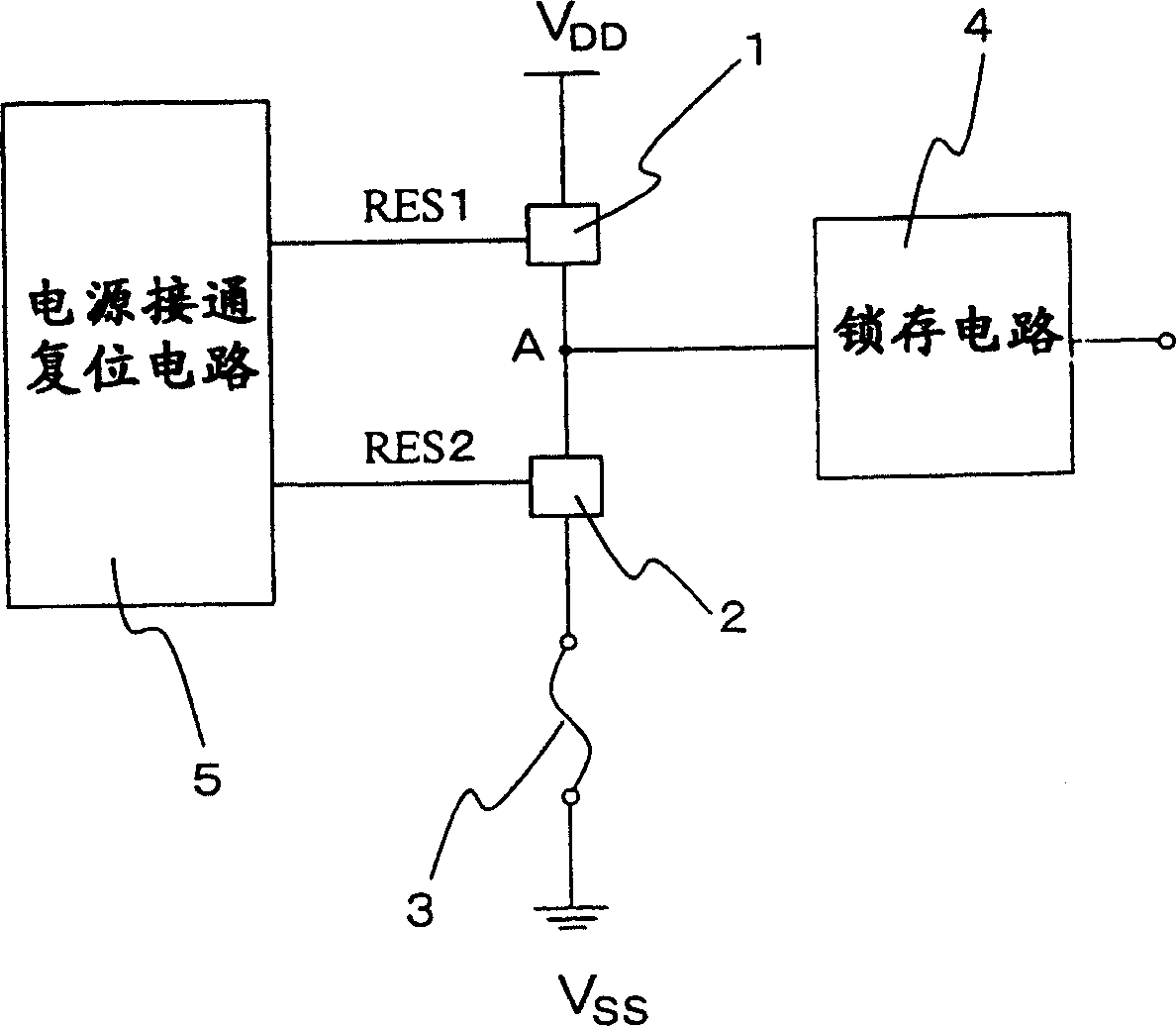

[0048] FIG. 3 is a schematic diagram of an address generation circuit according to the first embodiment of the present invention.

[0049] FIG. 3(a) is a circuit diagram of an address generating circuit according to a first embodiment of the present invention. In this figure, reference numeral 11 is a PMOS transistor; reference numeral 12 is an NMOS transistor; reference numeral 13 is a fuse element; reference numeral 14 is a latch circuit; An inverter; reference numeral 16 is a second inverter forming a latch circuit; reference numeral 17 is a third inverter; and reference numeral 18 is a power-on reset circuit.

[0050] In Fig. 3(a), the PMOS transistor 11, the NMOS transistor 12 and the fuse element 13 are under power supply V DD and ground V SS sequentially connected in series. The latch circuit 14 includes a first inverter 15 and a second inverter 16, the input terminal of one inverter is connected to the output terminal of the other inverter. A connection node A of t...

no. 2 example

[0074] Figure 4 is a schematic diagram of the address generating circuit of the second embodiment of the present invention. The second embodiment of the present invention provides a circuit example of the power-on reset circuit in the first embodiment.

[0075] In this figure, elements disclosed in FIG. 3 are denoted by the same reference numerals. Further, reference numeral 19 is an inverter; reference numeral 20 is a transistor whose source and drain are connected; reference numeral 21 is a PMOS transistor; and reference numeral 32 is an inverter delay circuit.

[0076] like Figure 4 As shown, the power-on reset circuit 18 of the second embodiment has a structure including two PMOS transistors 21 whose sources and drains are connected to each other and are connected in parallel between the power supply VDD and the ground VSS. . A PMOS transistor with its gate connected to its drain forms a diode transistor.

[0077] Furthermore, the power-on reset circuit 18 has a con...

no. 3 example

[0092] Figure 5 is a schematic diagram of the address generating circuit of the third embodiment of the present invention. In this figure, something like figure 2 Disclosed elements are denoted by the same reference numerals. In addition, reference numeral 22 is a first power-on reset circuit; reference numeral 23 is a second power-on reset circuit; reference numeral 24 is an NMOS transistor with a low threshold; and reference numeral 25 is an NMOS transistor with a high threshold. The transistor and reference numeral 26 is a PMOS transistor.

[0093] The address generating circuit of the third embodiment of the present invention has a structure substantially similar to that of the first and second embodiments. However, the address generation circuit of the third embodiment is different in the structure of the power-on reset circuit.

[0094] like Figure 5 As shown, the power-on reset circuit of the third embodiment includes a first power-on reset circuit 22 for outputt...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More