Compound integrated circuit design verification method

A technology for integrated circuit and electronic design, applied in the field of design verification of composite integrated circuits, which can solve problems such as co-simulation and simulation that cannot run applications, long turnaround time, and difficulty in finding defects.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] In prior patent applications owned by the same assignee of the present invention, event-based test systems are described in U.S. Patent Application Nos. 09 / 406,300 and 09 / 340,371 "Event based semiconductor testsystem," while Event-based design validation stations are described in / 428,746 "Method and apparatus for SoC design validation". Additionally, time scaling techniques are described in US Patent Application No. 09 / 286,226 "Scaling logic for Event Based Test System". All of these patent applications are hereby incorporated by reference herein.

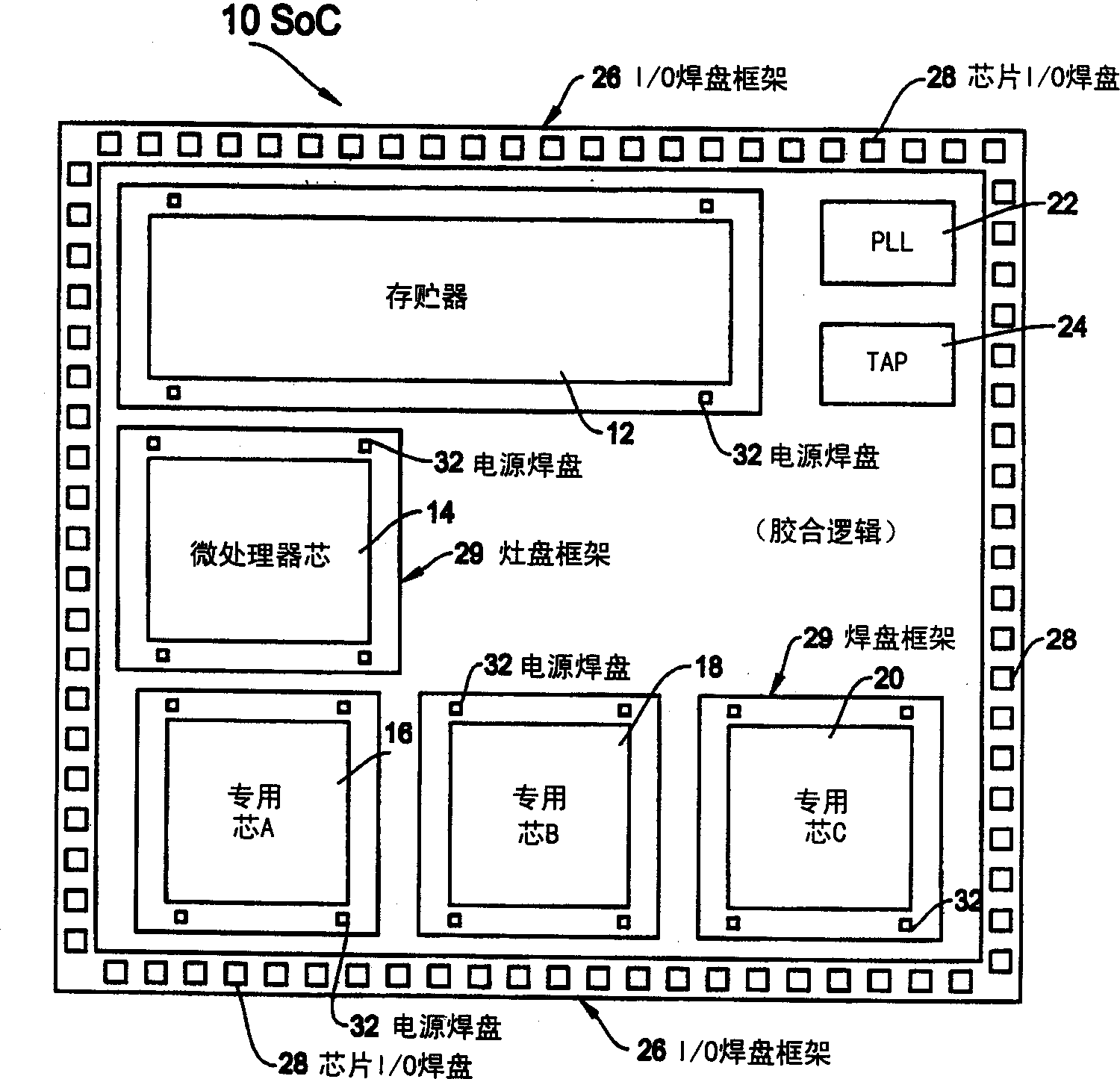

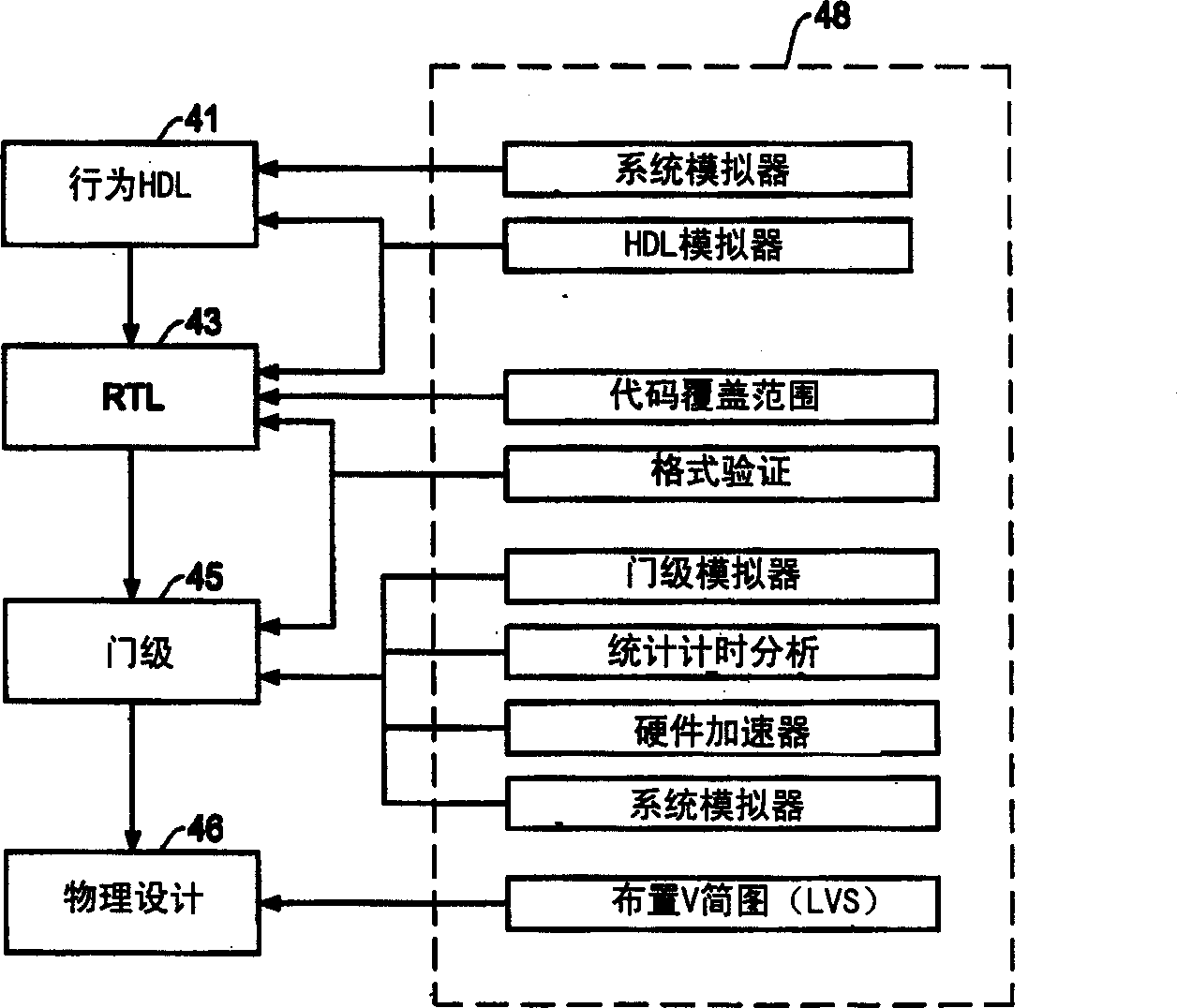

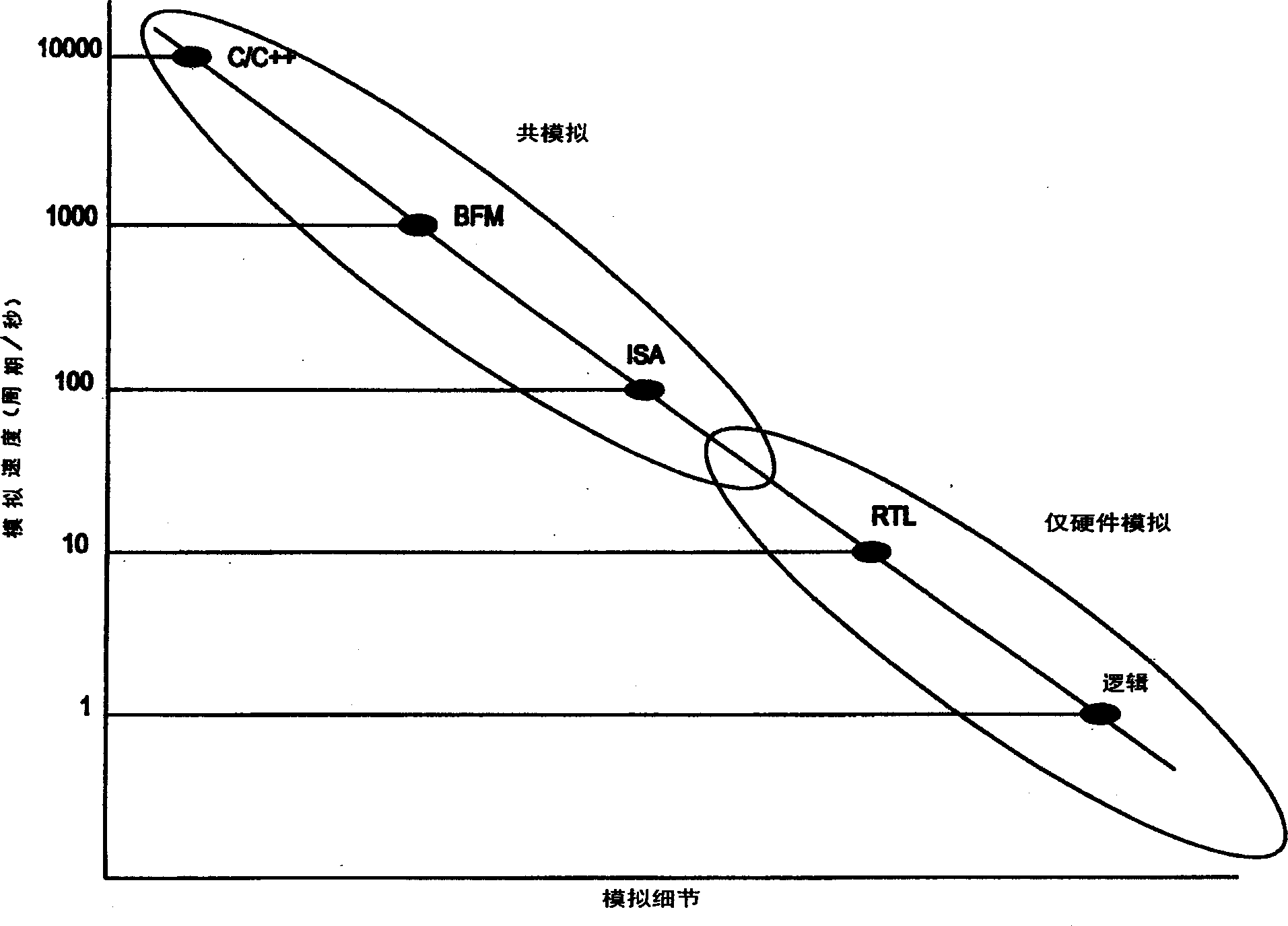

[0041] In the present invention, the inventors provide a concept of an integrated circuit design verification method using an event-based test system. More specifically, in the first embodiment, a design verification method using a silicon prototype is described, and in the second embodiment, a method without a silicon prototype is described. Both methods of the present invention are faster and less expensive than any cur...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap