Pseudo quarternary flow-process stracture used by 16-bit micro-processor

A microprocessor and pipelining technology, applied in the computer field, can solve the problems of not being able to fully utilize resource efficiency, occupy large design resources, and not suitable for small microprocessors, etc., so as to reduce the complexity of design for testability and reduce the size of chips Resource requirements, effects of avoiding data-related problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] In order to understand the present invention more clearly, the present invention will be further described in detail below in conjunction with the accompanying drawings.

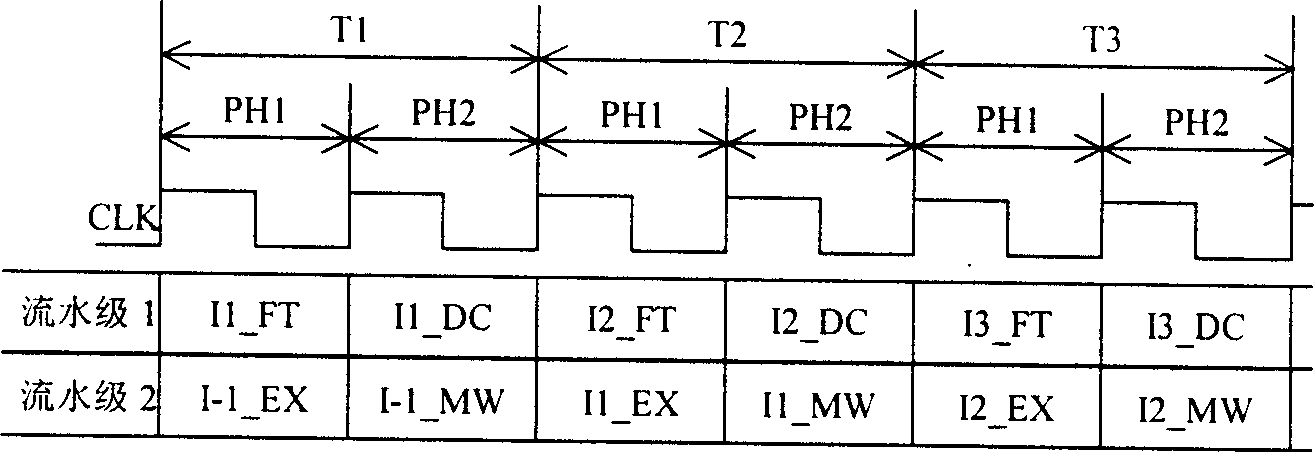

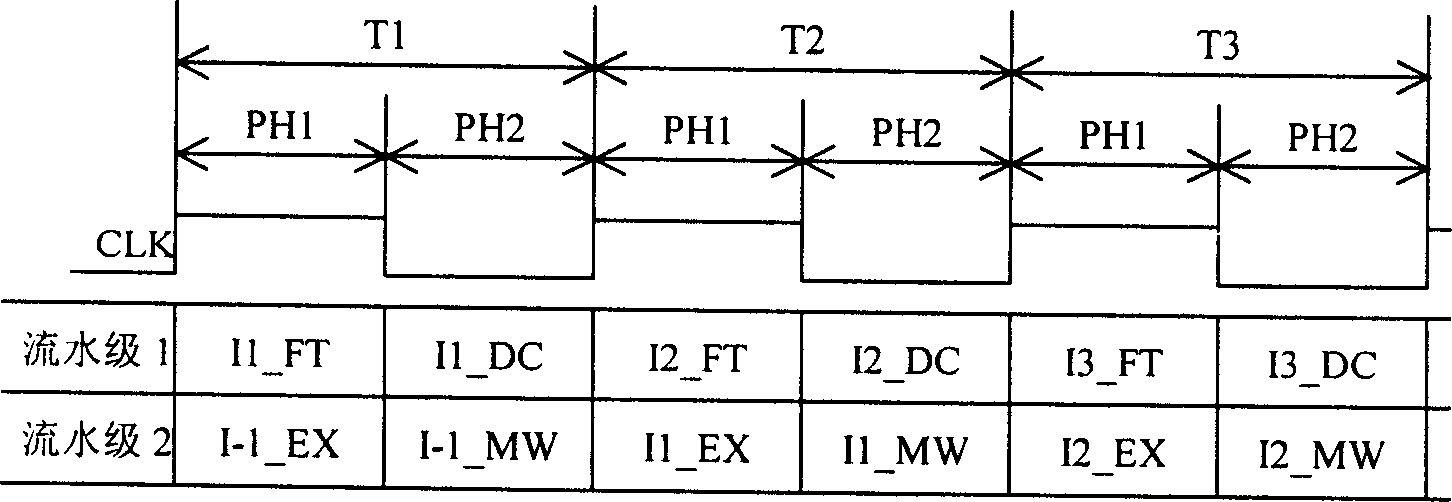

[0027] see figure 1 , figure 1 It is a flow chart of the pseudo four-stage pipeline structure instruction used by the 16-bit microprocessor (code-named LS-IPU16) of the present invention.

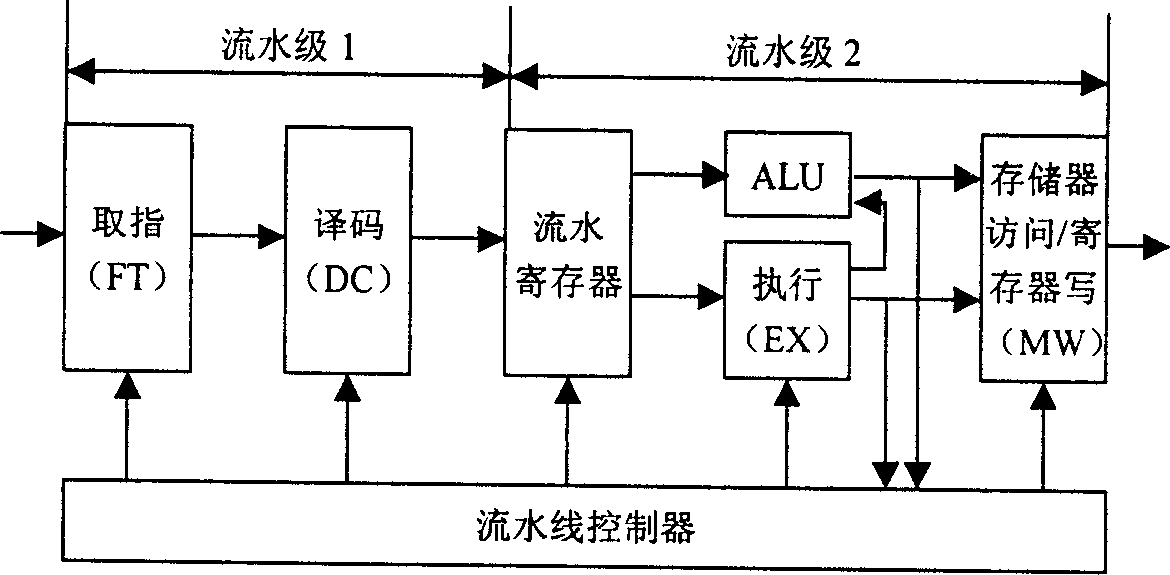

[0028] In the design of the 16-bit microcontroller for I / O channel data processing, the applicant adopts a pseudo-four-stage pipeline structure, which greatly simplifies the design complexity of the processor core.

[0029] The design idea of the pseudo four-stage pipeline structure used by the 16-bit microprocessor is as follows: figure 1 As shown, the LS-IPU16 microprocessor has a total of 37 instructions in 5 categories, and the execution of each instruction is divided into fetching instruction (FT), decoding (DC), executing (EX) and memory access and writing (MW). stage, set a two-stage pipeline in the pro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More