Data processing system capable of using virtual memory processing mode

A technology of data processing system and processing mode, applied in memory systems, electrical digital data processing, instruments, etc., can solve the problems of complex VMM code, not very effective replacement strategy, and VMM not understanding hardware structure, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] For purposes of illustration, the present invention is described using a multiprocessor data processing system with a single level of cache memory. It will be appreciated that the features of the present invention are applicable to data processing systems having multiple levels of cache memory.

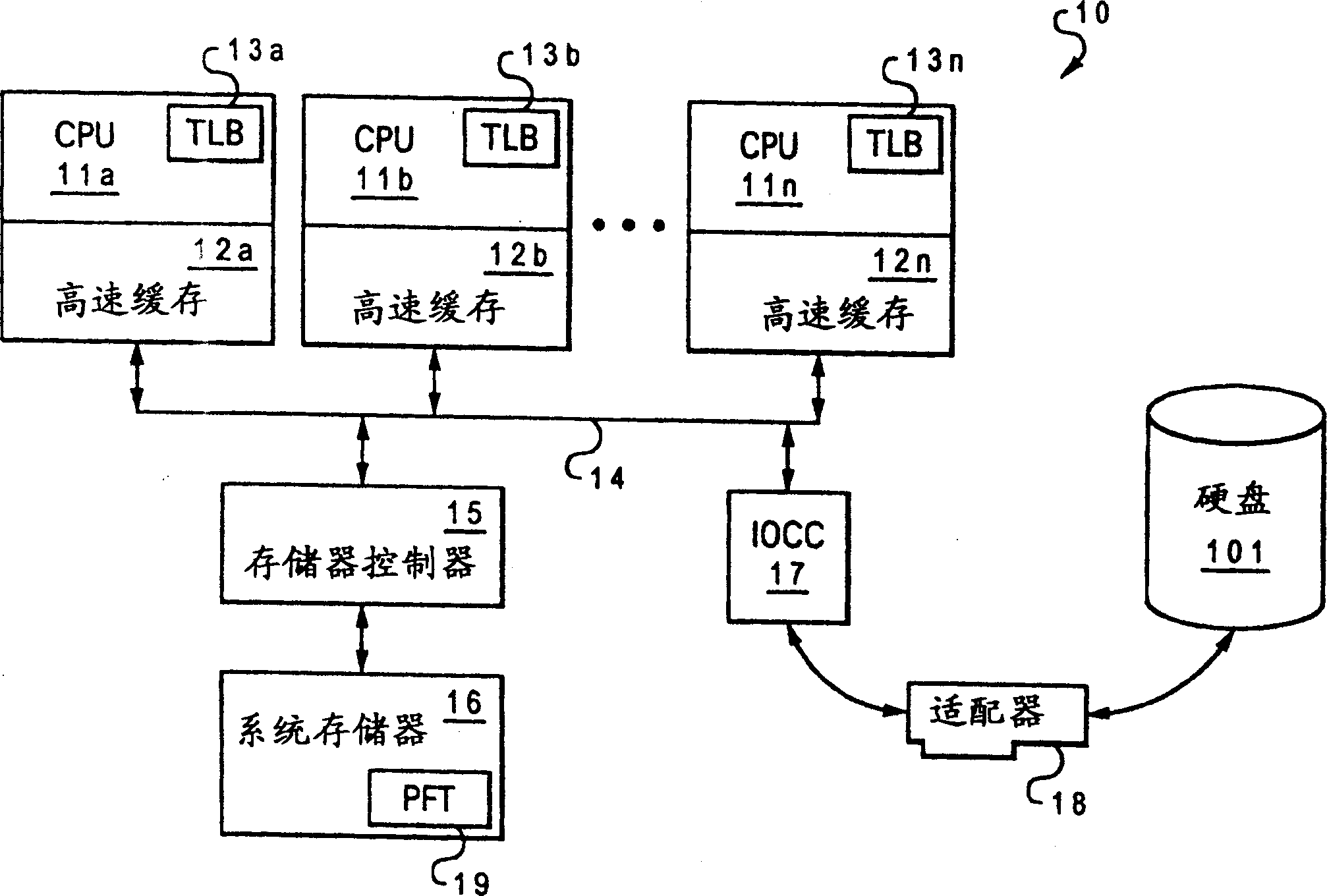

[0022] I. Existing technology

[0023] Referring now to the drawings, and in particular to FIG. 1, there is shown a block diagram of a multiprocessor data processing system according to the prior art. As shown, multiprocessor data processing system 10 includes a plurality of central processing units (CPUs) 11a-11n, each CPU 11a-11n including a cache memory. For example, the CPU 11a includes a cache memory 12a, the CPU 11b includes a cache memory 12b, and the CPU 11n includes a cache memory 12n. Through interconnect 14 , CPUs 11 a - 11 n and cache memories 12 a - 12 n are connected to memory controller 15 and system memory 16 . Interconnect 14 acts as a communication processi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More