Data transfer apparatus

A data transmission device and data transmission technology, which are applied in the fields of electrical digital data processing, television, color television, etc., can solve the problems of low buffer usage efficiency, low access frequency, and inability to perform high-speed access, and reduce buffering. The effect of the device capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0062] Next, Embodiment 1 of the present invention will be described using the drawings.

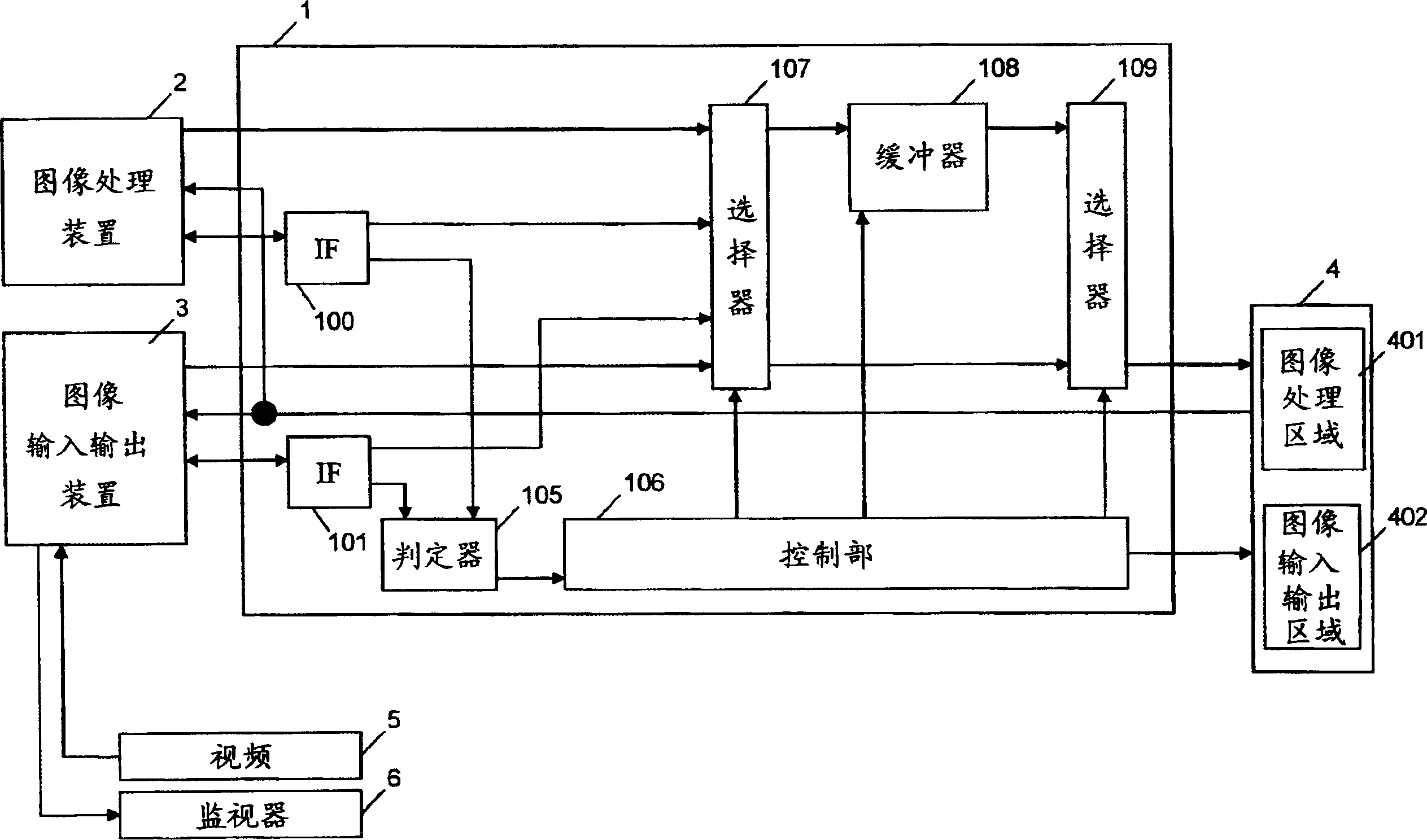

[0063] figure 1 is a block diagram showing the structure of the data transmission device according to Embodiment 1 of the present invention.

[0064] exist figure 1 Among them, symbols 2 to 6 are the same functional blocks as those in the prior art. In the data transmission device 1 , the interface 100 performs data transmission control with the image processing device 2 . The interface 101 performs data transfer control with the image input / output device 3 . The selector 107 makes the transmission data from the image processing device 2 and the transmission control signal from the interface 100 a first input, makes the transmission data from the image input and output device 3 and a transmission control signal from the interface 101 a second input, and controls The control signal of the unit 106 selects and outputs the above-mentioned transmission data to the buffer 108 and the se...

Embodiment 2

[0079] use Figure 10 and Figure 11 The data transmission sequence in the data transmission device according to Embodiment 2 of the present invention will be described. Figure 10 and Figure 11 A case where read transfer is performed by the image processing device 2 while burst transfer is performed by the image input / output device 3 is shown. Figure 10 Represents the data transmission timing in the data transmission device of the prior art, Figure 11 The sequence of data transmission in the data transmission device according to the second embodiment of the present invention is shown. The structure of the data transmission device is the same as that of Embodiment 1.

[0080] In the prior art data transmission device, in Figure 10 , the image input / output device 3 starts the transfer to the shared memory 4 with a burst transfer. During the burst transfer, the image processing device 2 outputs a read request to the shared memory 4 . The data D10 to D14 from the image...

Embodiment 3

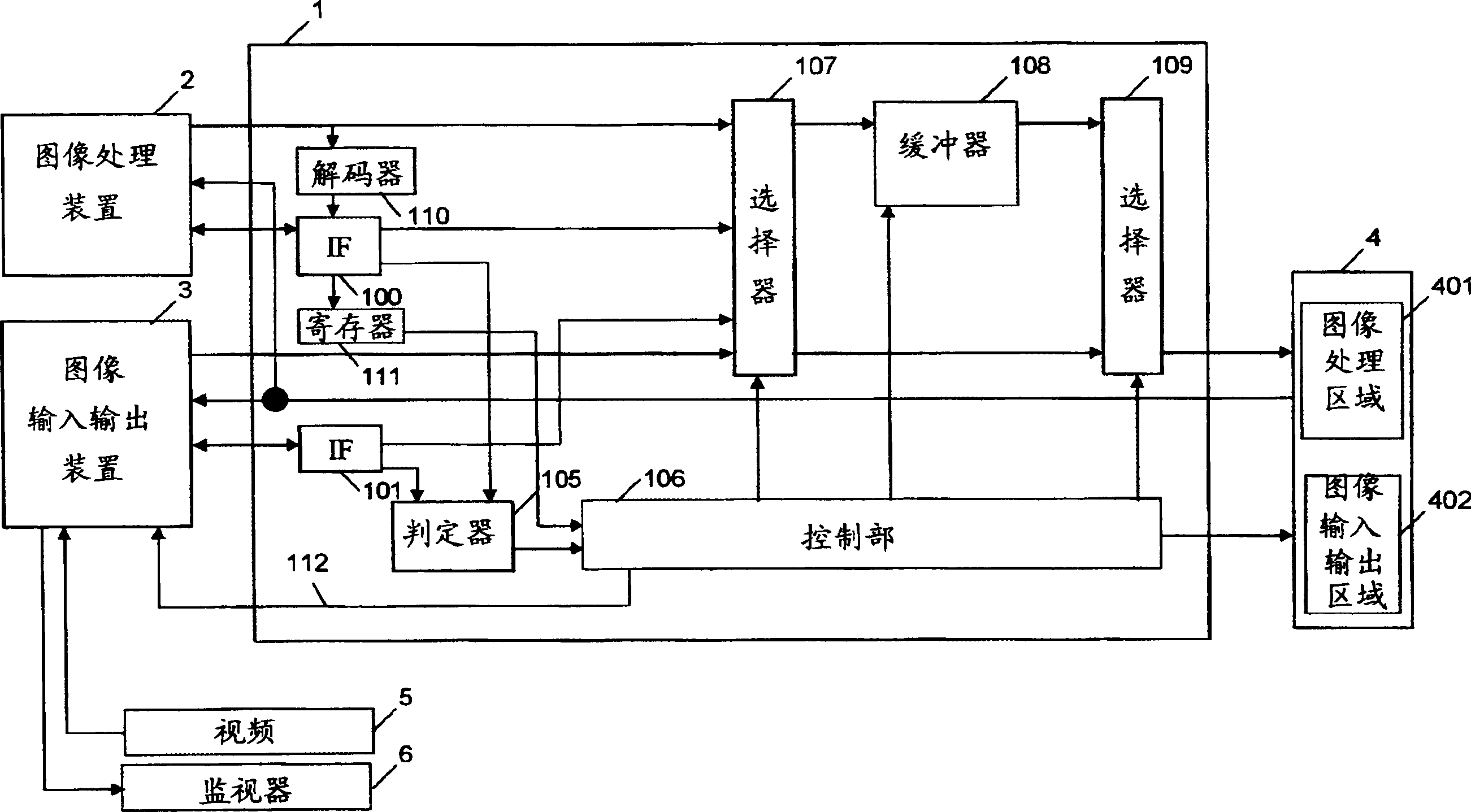

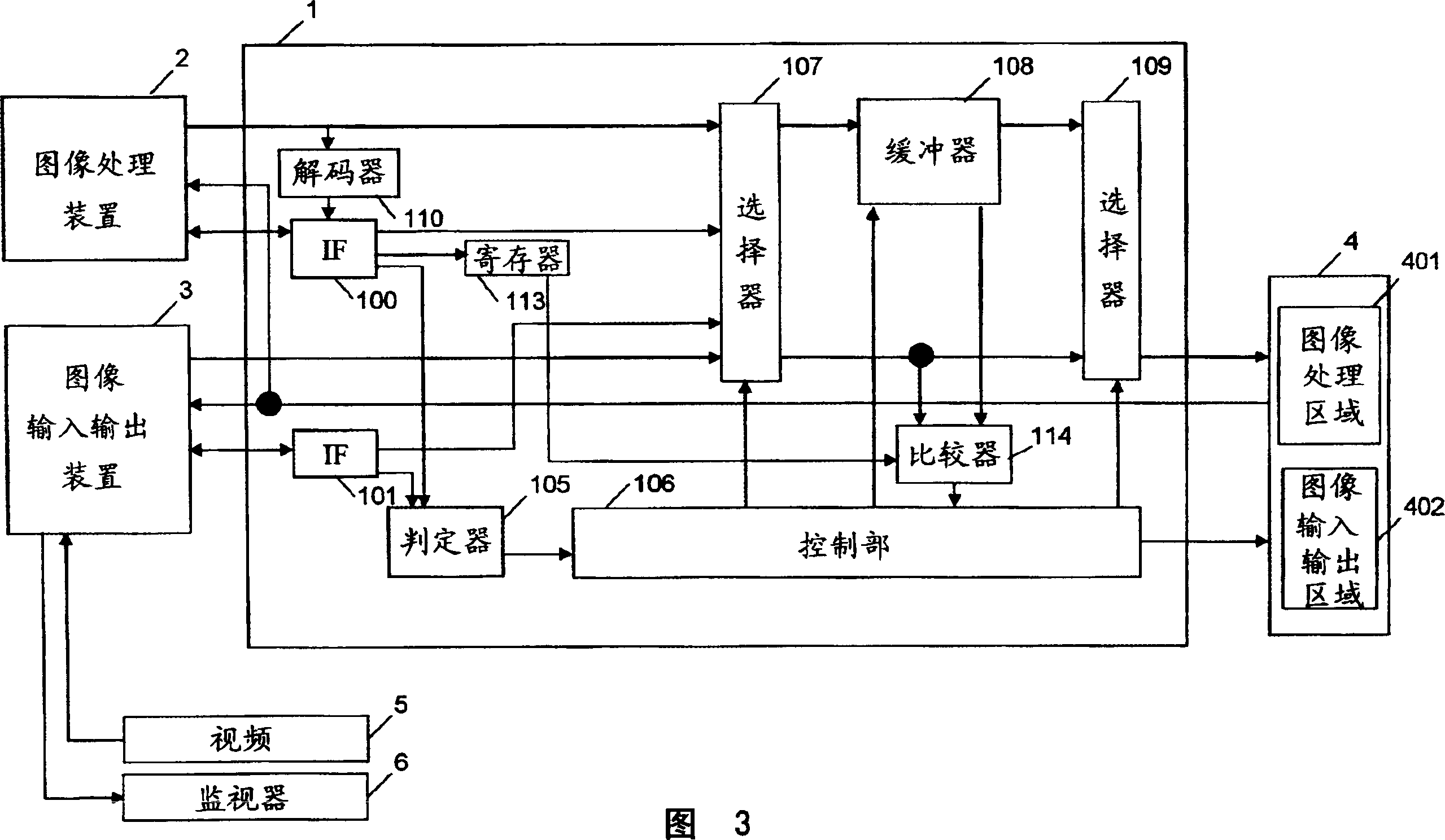

[0085] figure 2 is a block diagram showing the configuration of a data transmission device according to Embodiment 3 of the present invention.

[0086] exist figure 2 Among them, symbol 110 denotes an address decoder, symbol 111 denotes a buffer transfer request register, and symbol 112 denotes a buffer transfer end notification interrupt signal. For other structural elements with figure 1 same function.

[0087] Seen from the image processing device 2 , the data transfer device 1 is mapped to an address to the shared memory 4 and an address to the buffer transfer request register 111 . Then, an access address from the image processing device 2 is decoded by the address decoder 110 to access the buffer transfer request register 111 . When the access to the buffer transfer request register 111 is started, the control unit 106 starts transferring the data held in the buffer 108 to the shared memory 4, and the control interface keeps the buffer transfer request register ac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More