Patents

Literature

85results about How to "Reduce the amount of hardware" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

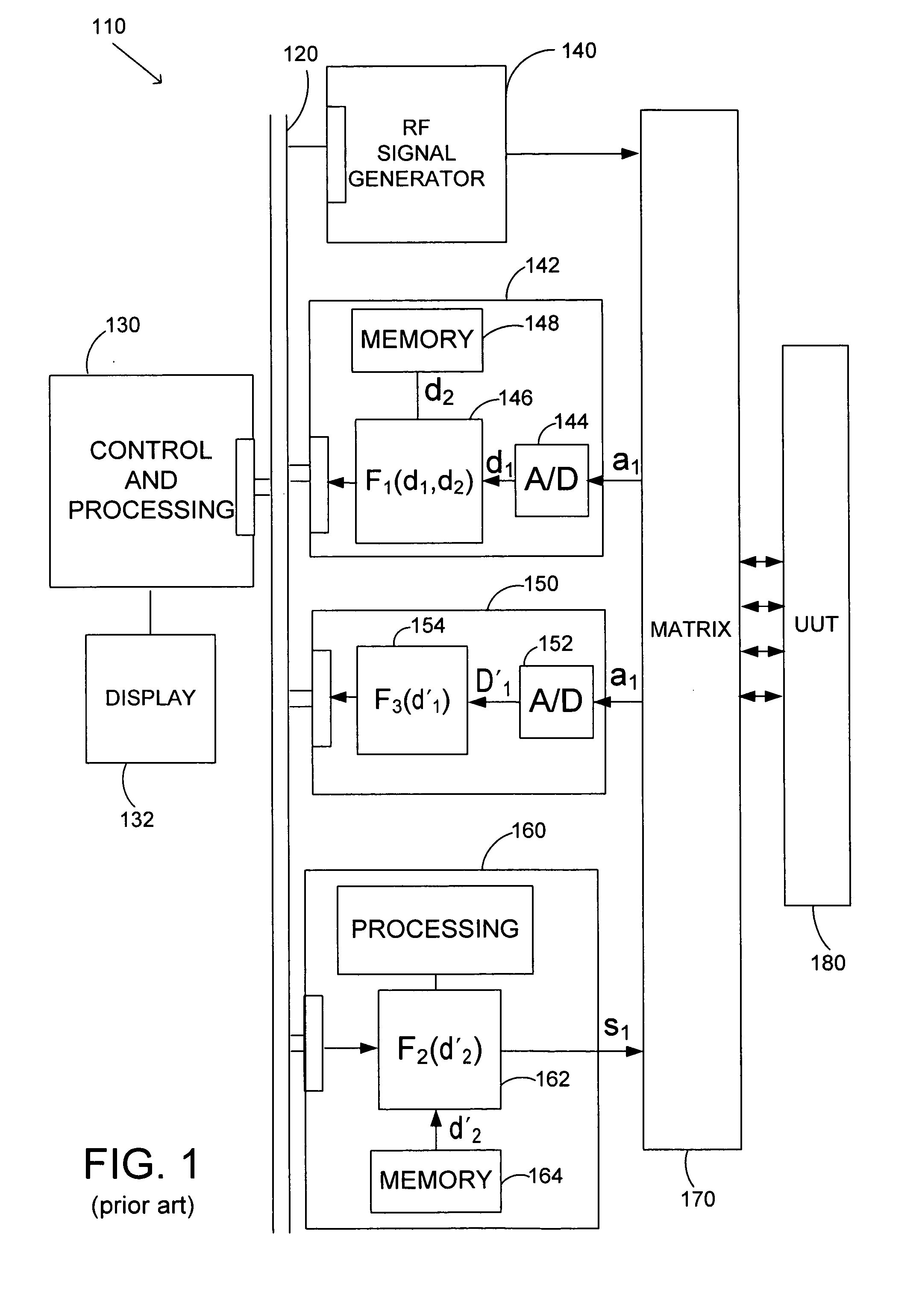

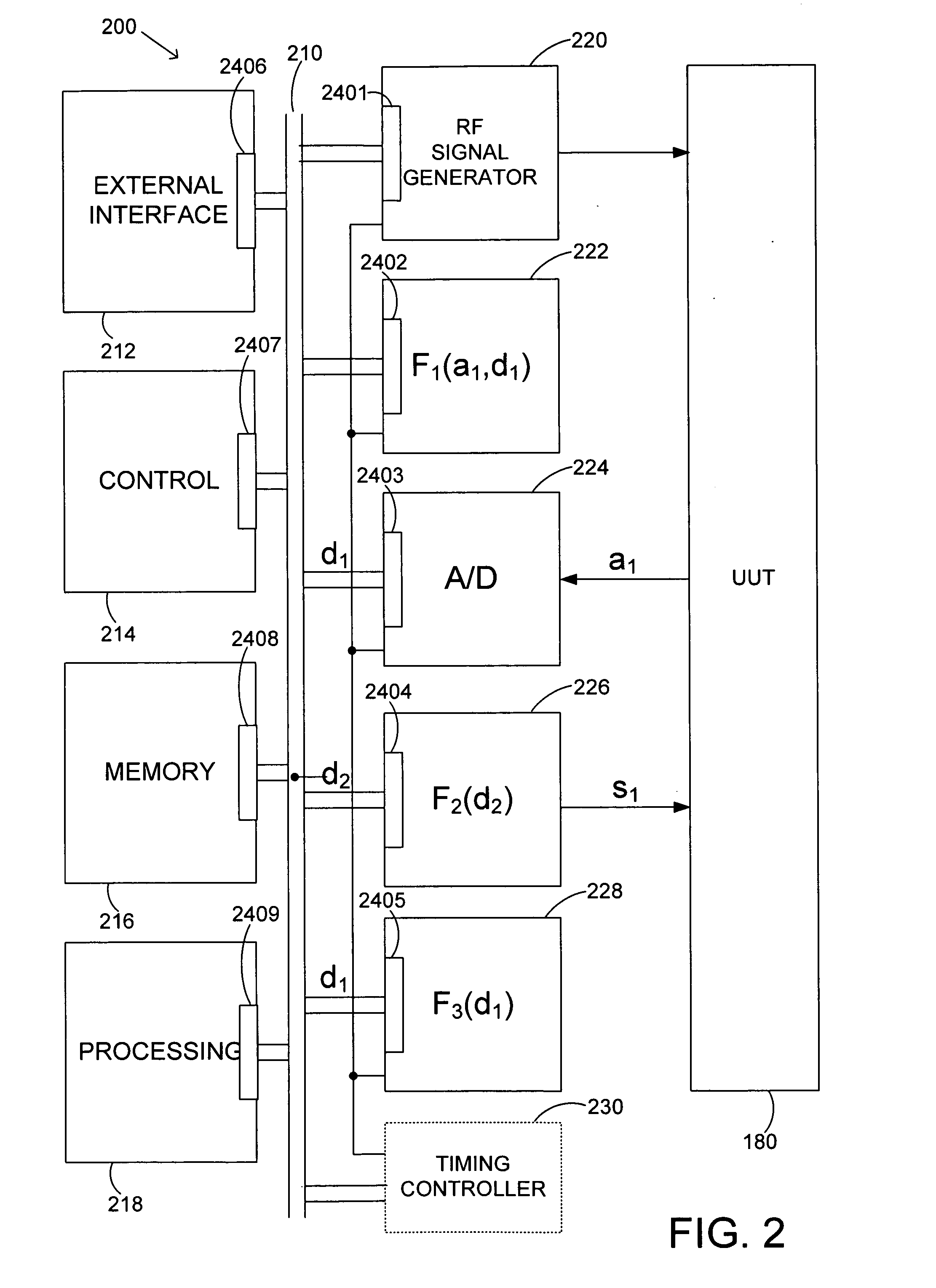

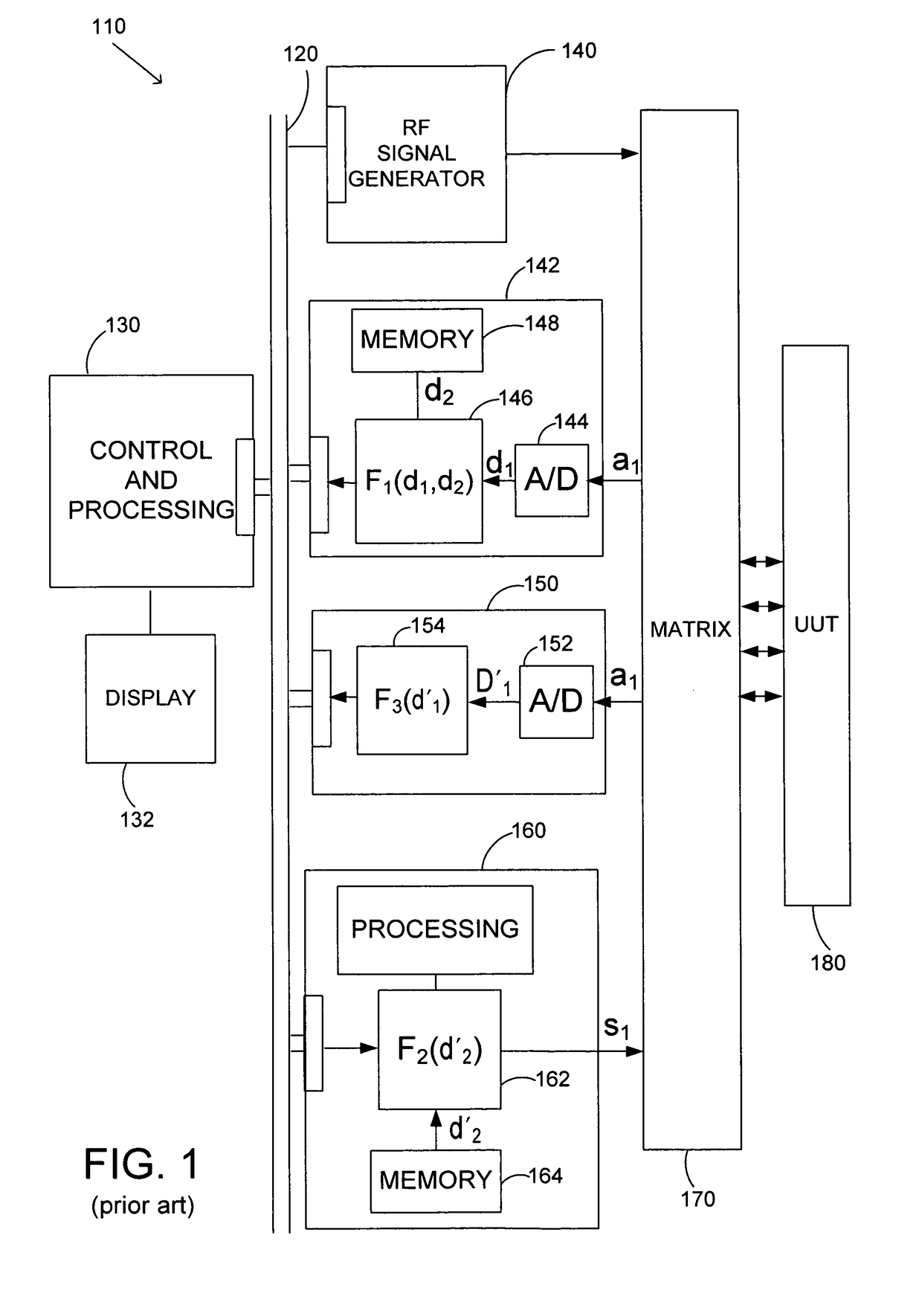

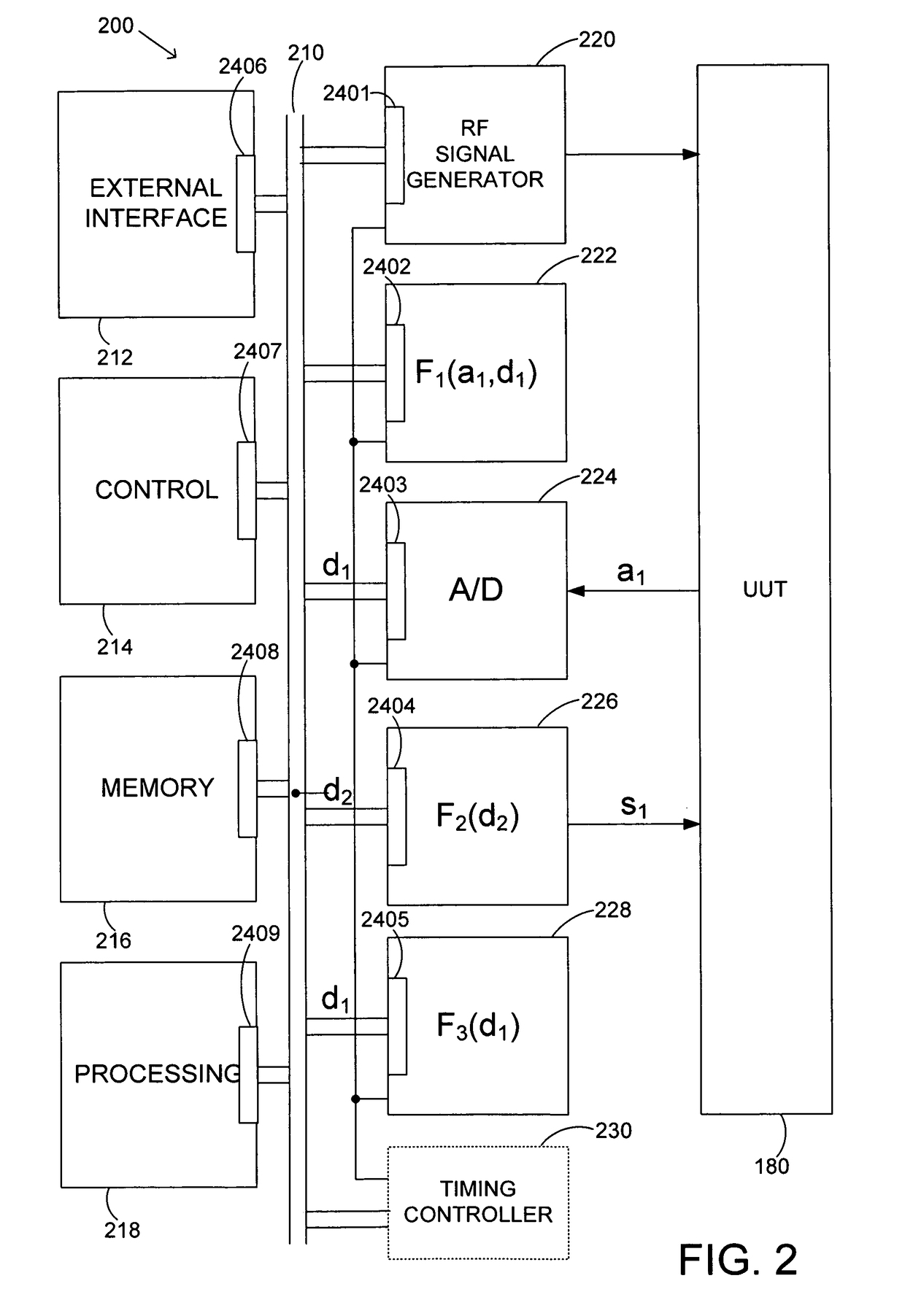

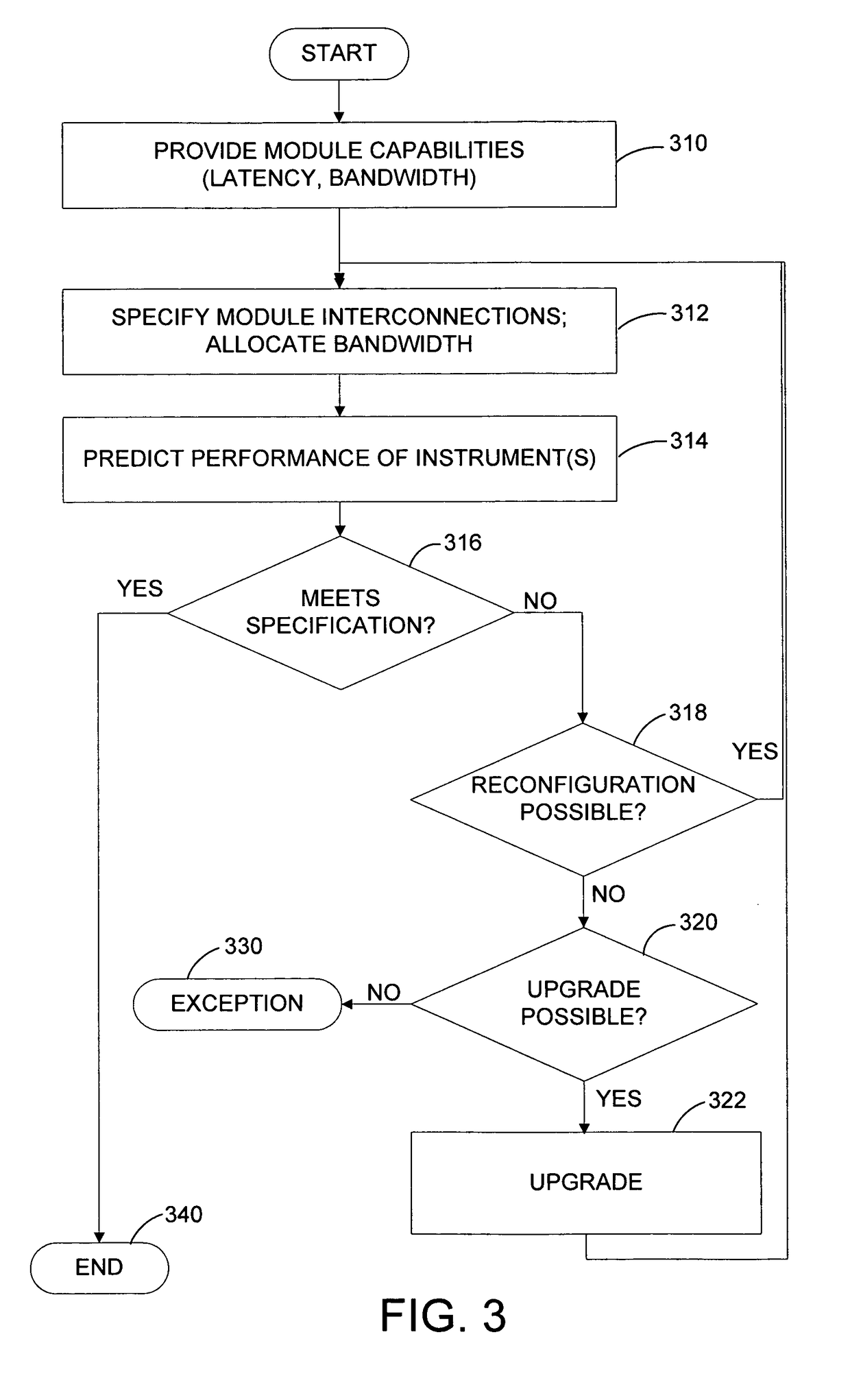

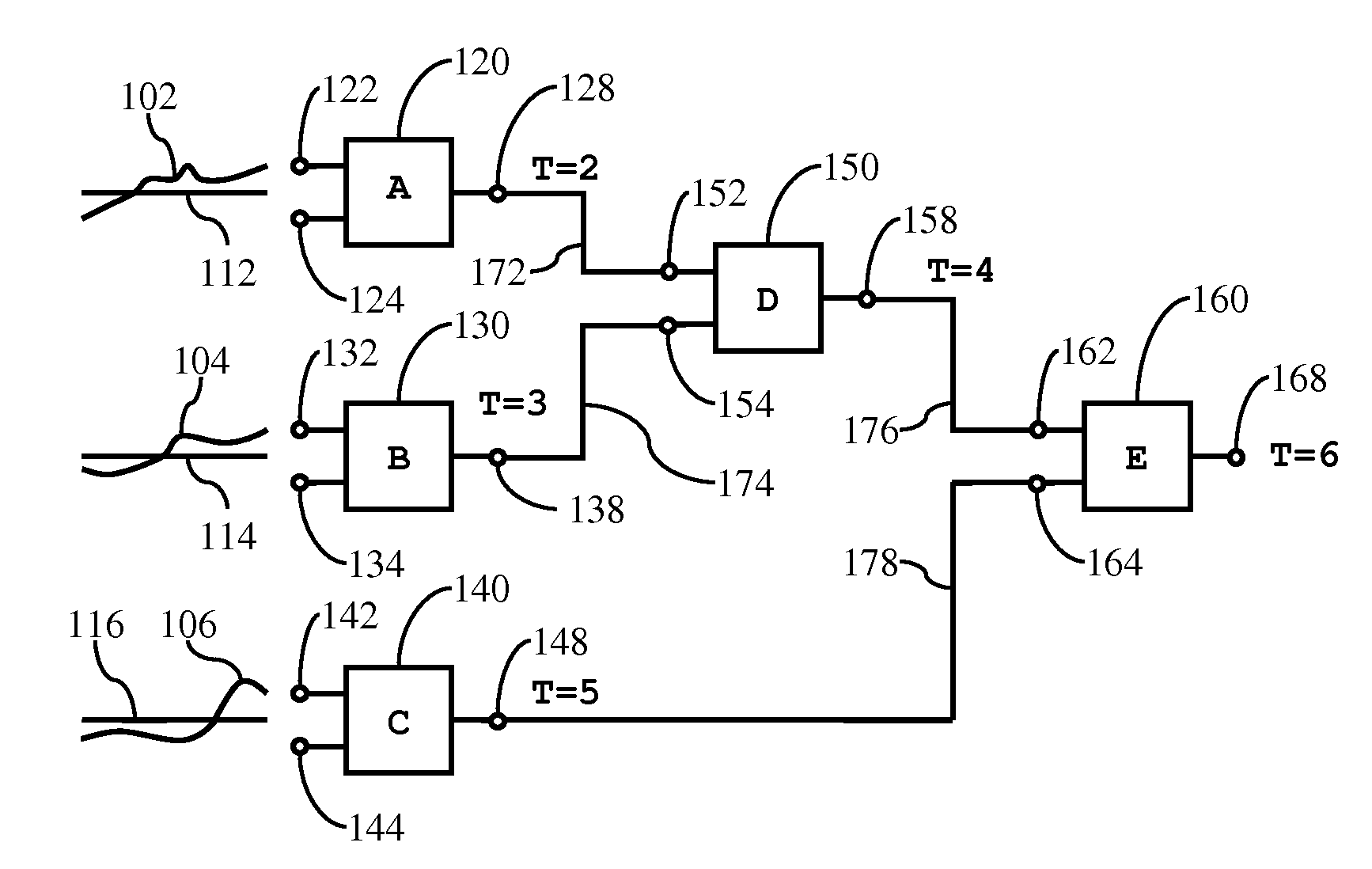

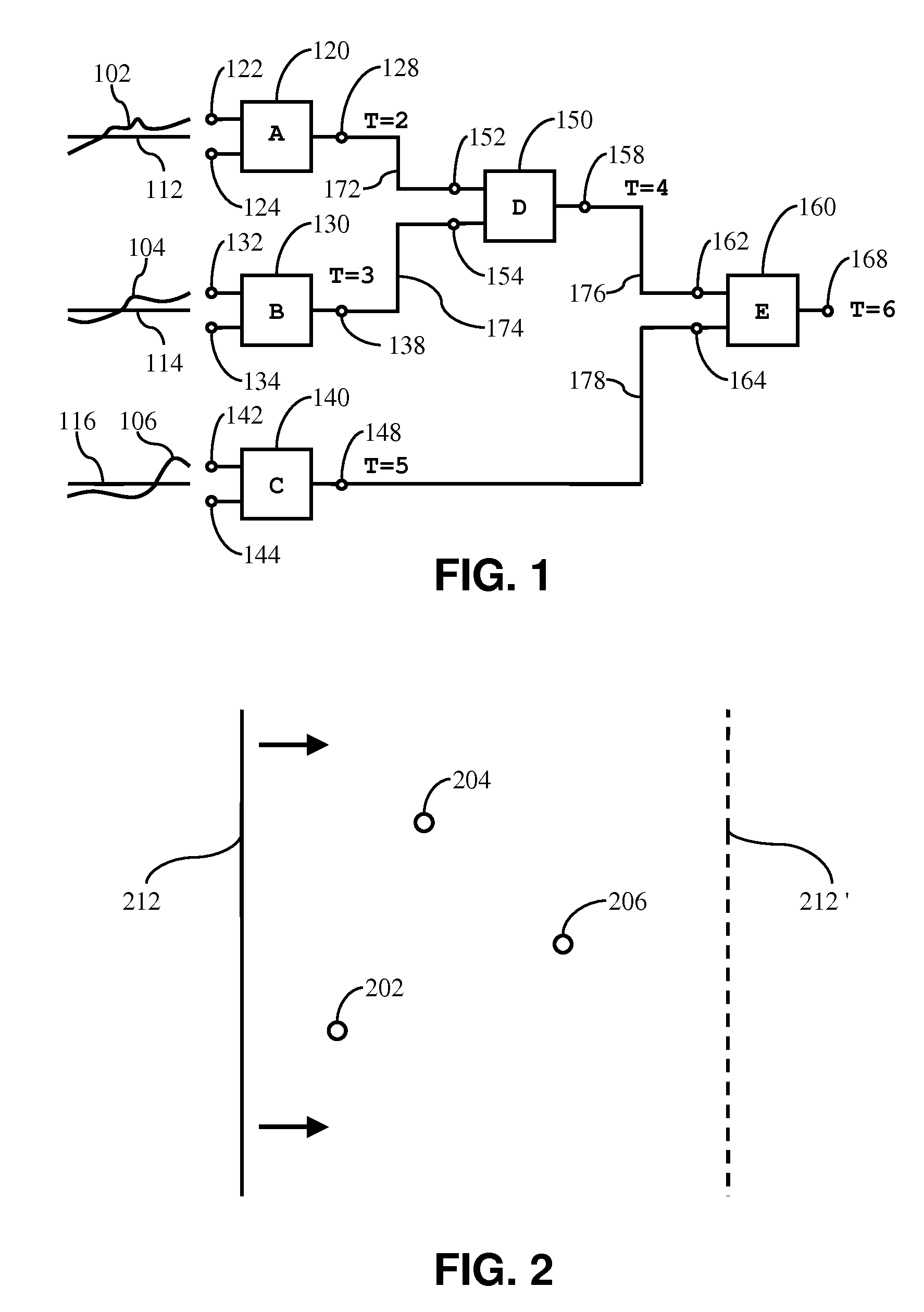

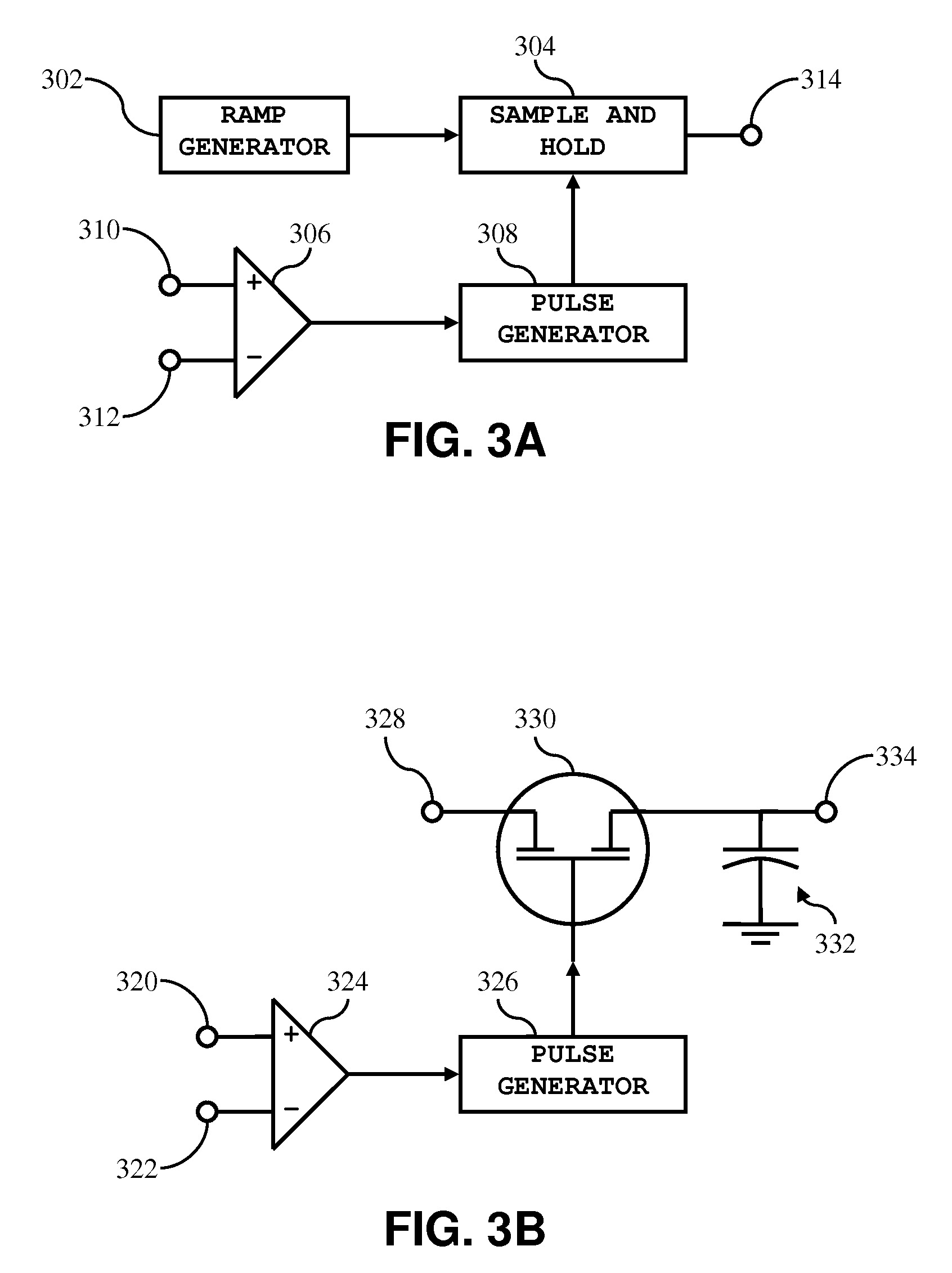

Networked test system

ActiveUS20080098272A1Reduce amount of hardwareReduce the amount of hardwareDigital circuit testingDetecting faulty hardware by remote testVirtual instrumentationInstrumentation

An automatic test system that can be configured to perform any of a number of test processes. The test system contains multiple functional modules that are interconnected by a network. By using software to configure data flow between functional modules, combinations of modules can be made, thereby creating virtual instruments. As test requirements change, the test system can be reconfigured to contain other virtual instruments, eliminating or reducing the need to add instruments to meet changing test requirements. To ensure adequate performance of the test system, a proposed configuration may be simulated, and if a virtual instrument does not provide a required level of performance, the test system may be reconfigured.

Owner:TERADYNE

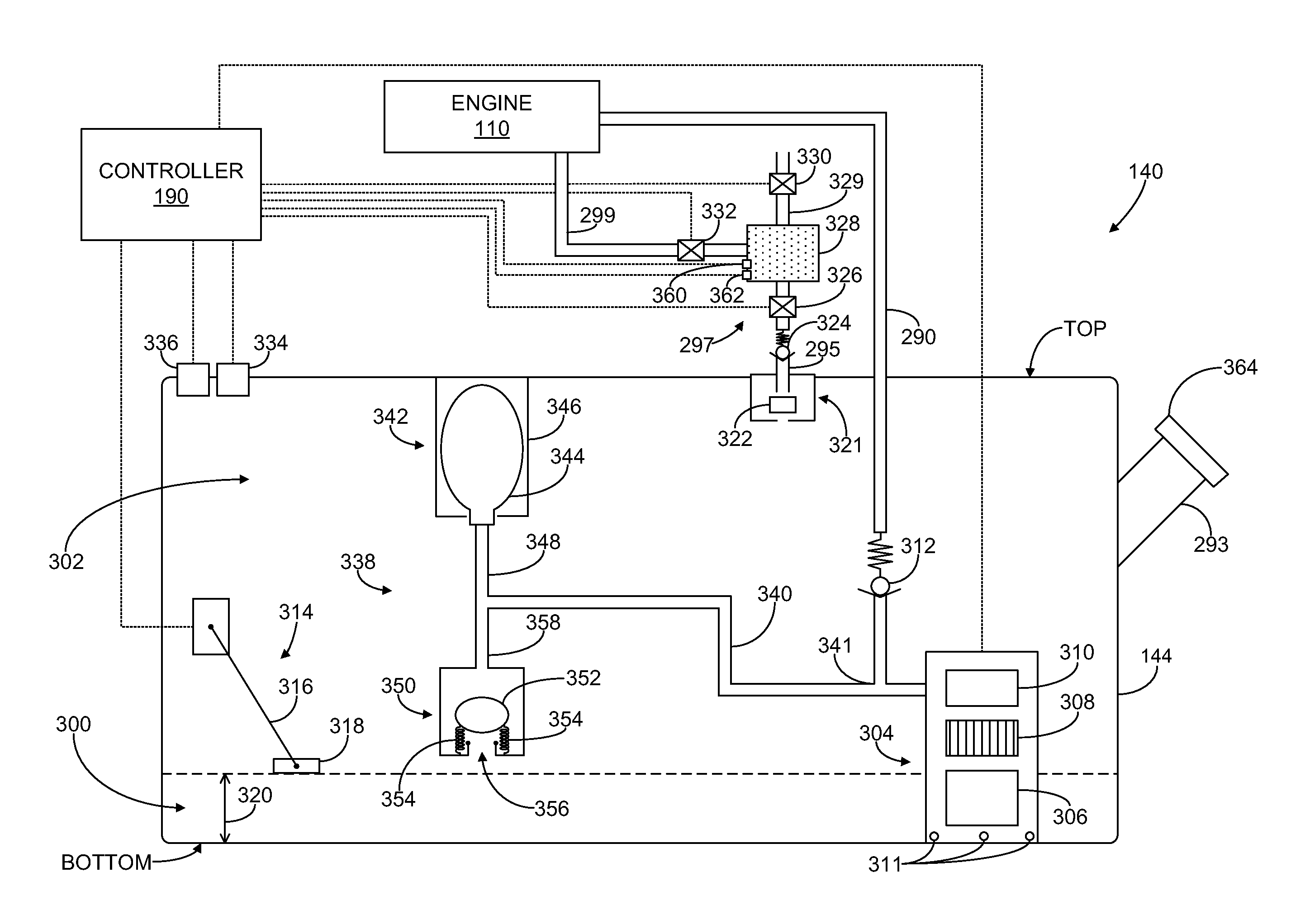

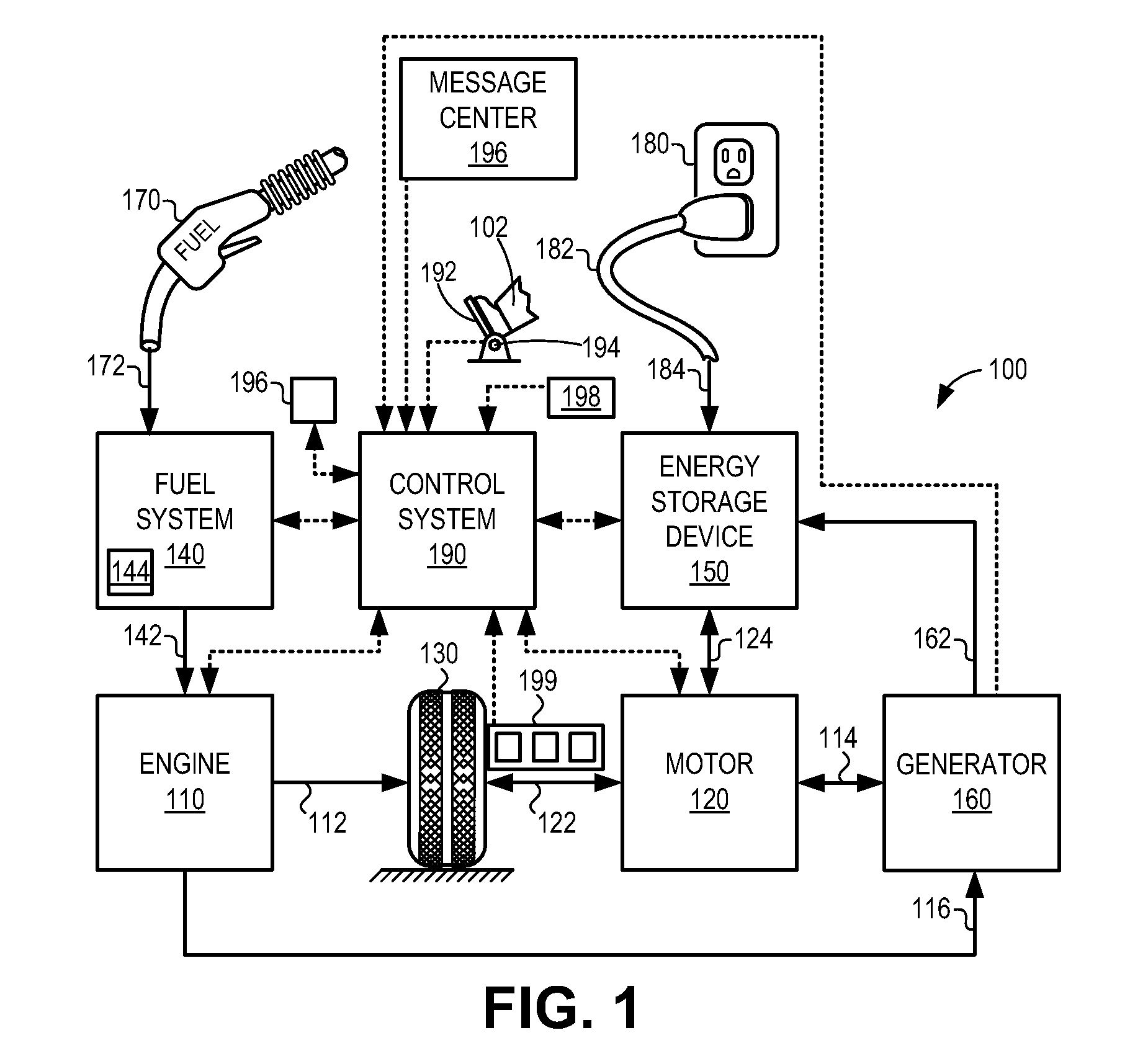

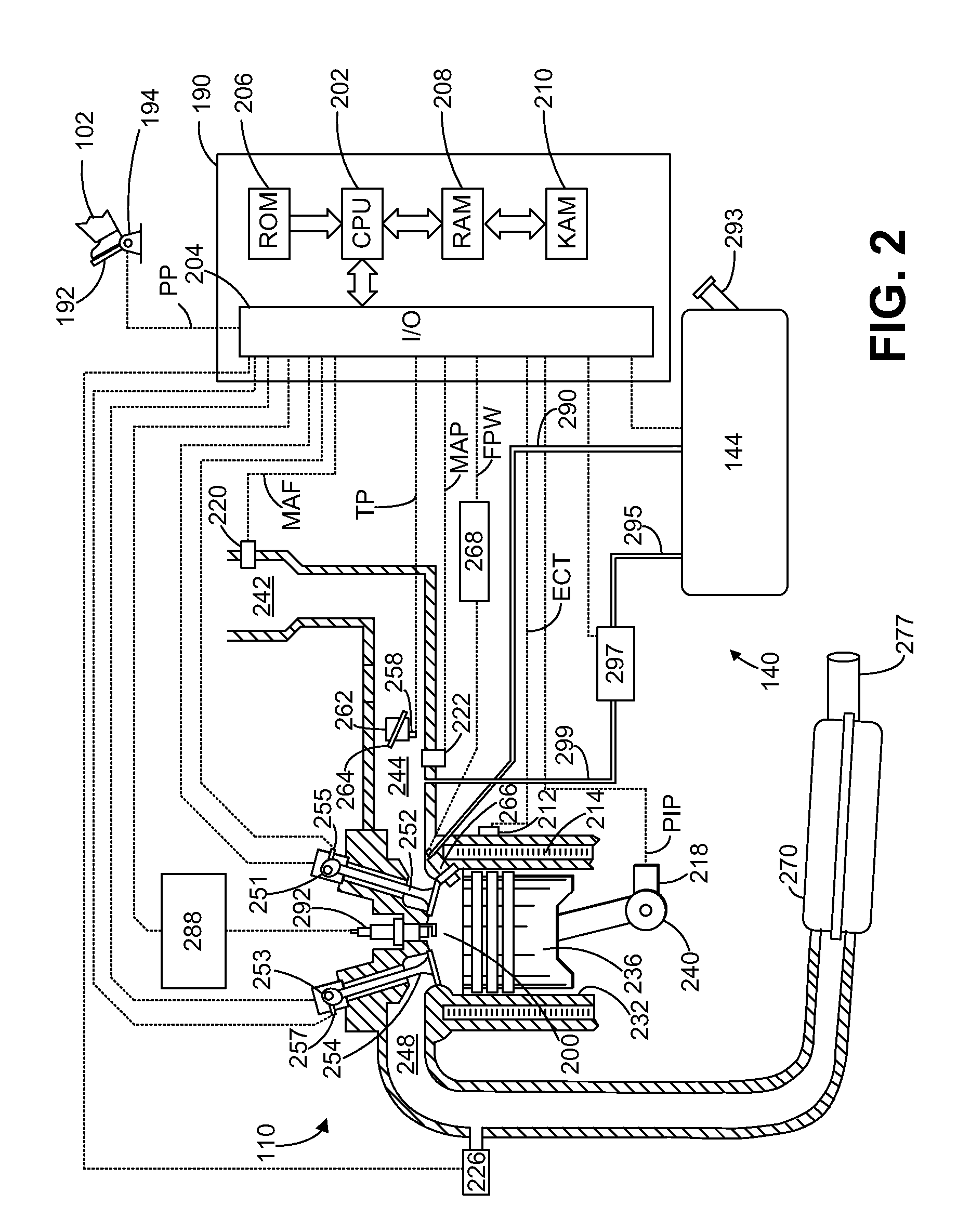

Automotive fuel system leak testing

ActiveUS8074627B2Improve installationSimple materialDetection of fluid at leakage pointAnalogue computers for vehiclesFuel tankAutomotive fuel

Systems and methods for performing leak testing on fuel system components in hybrid vehicles during engine-off operating conditions are disclosed. For example, a fuel tank may include a pressure accumulator which may be filled with fuel via a fuel pump in order to generate a vacuum which may be used to diagnose leaks in the fuel system.

Owner:FORD GLOBAL TECH LLC

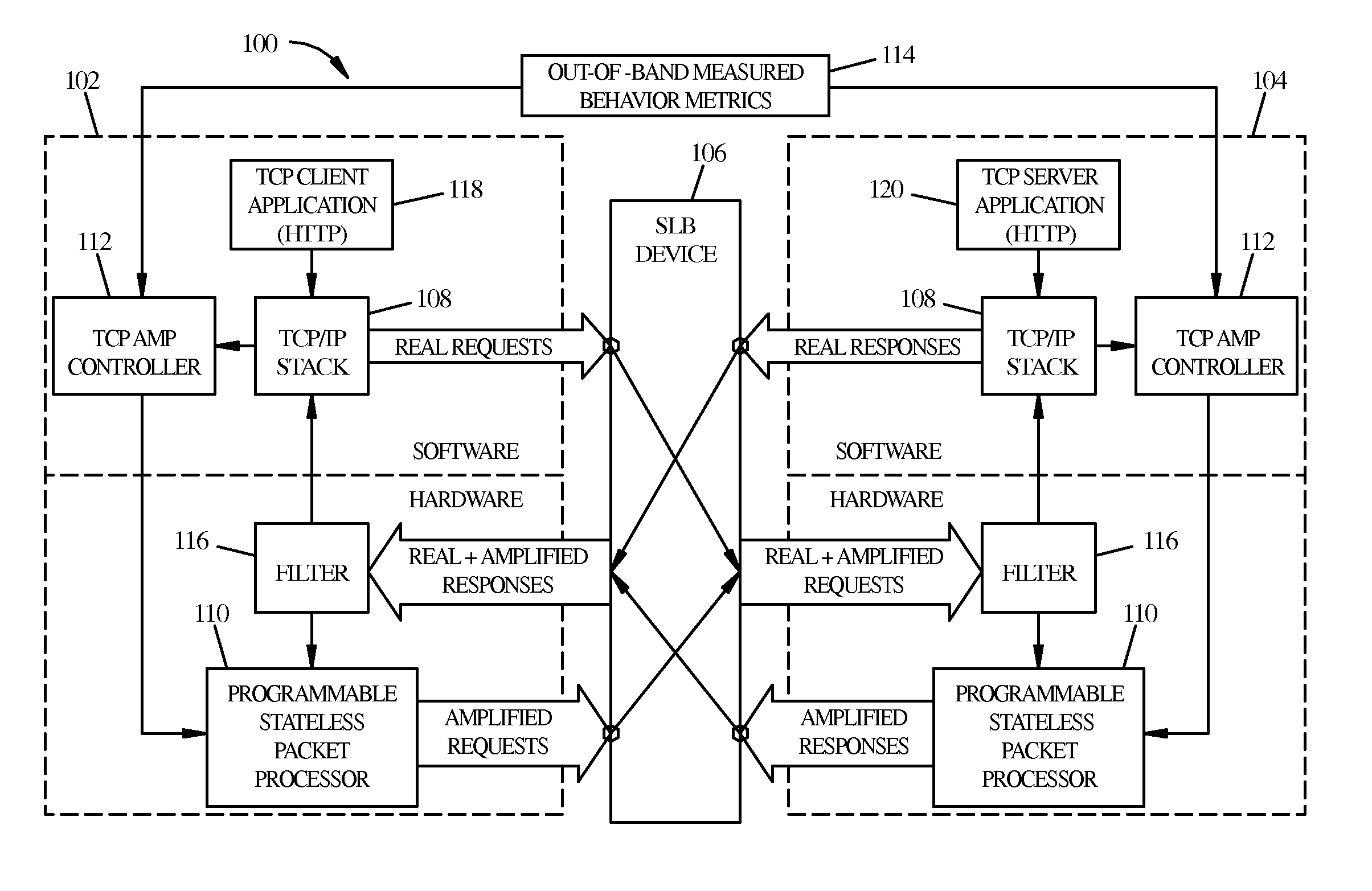

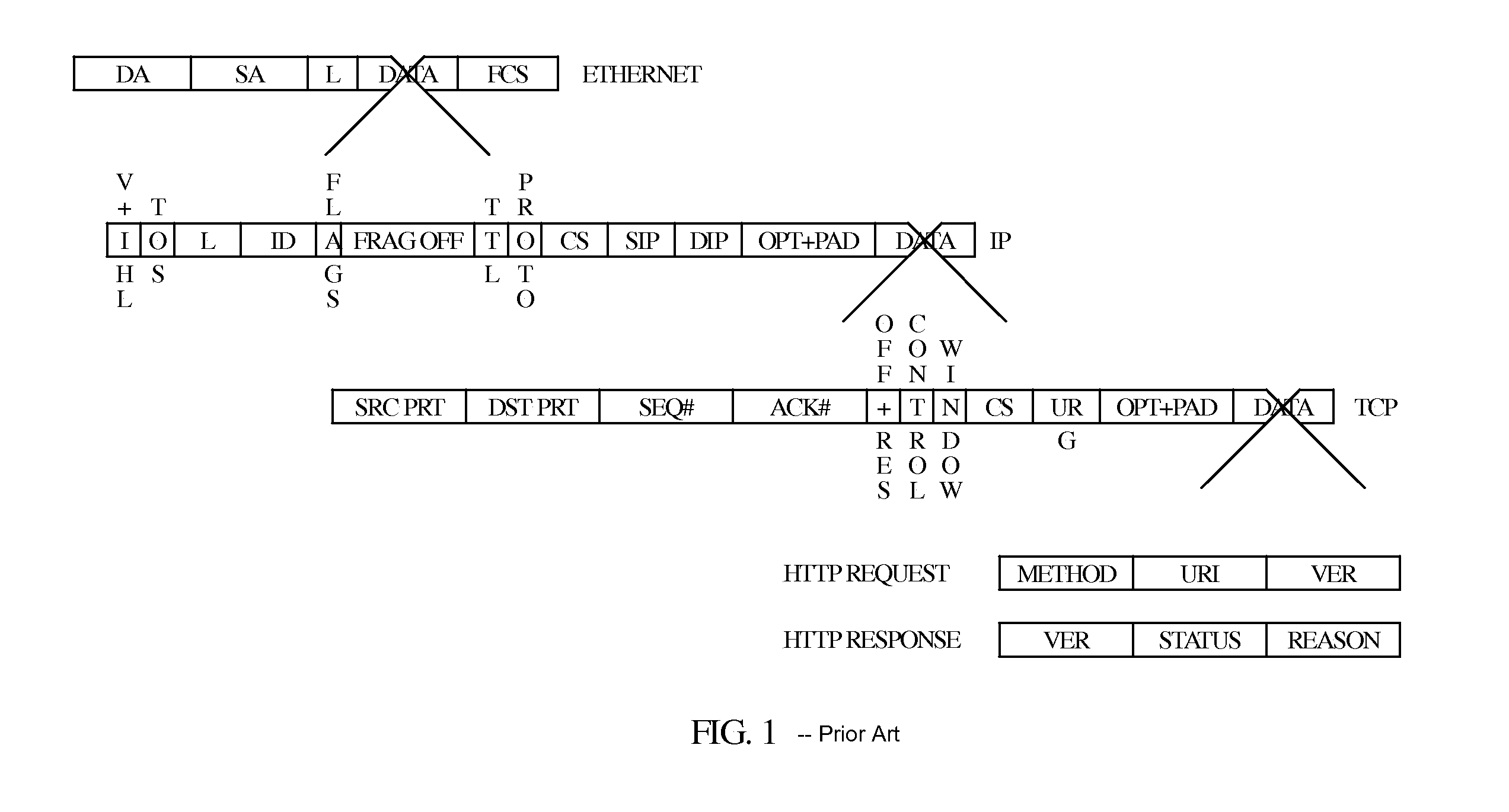

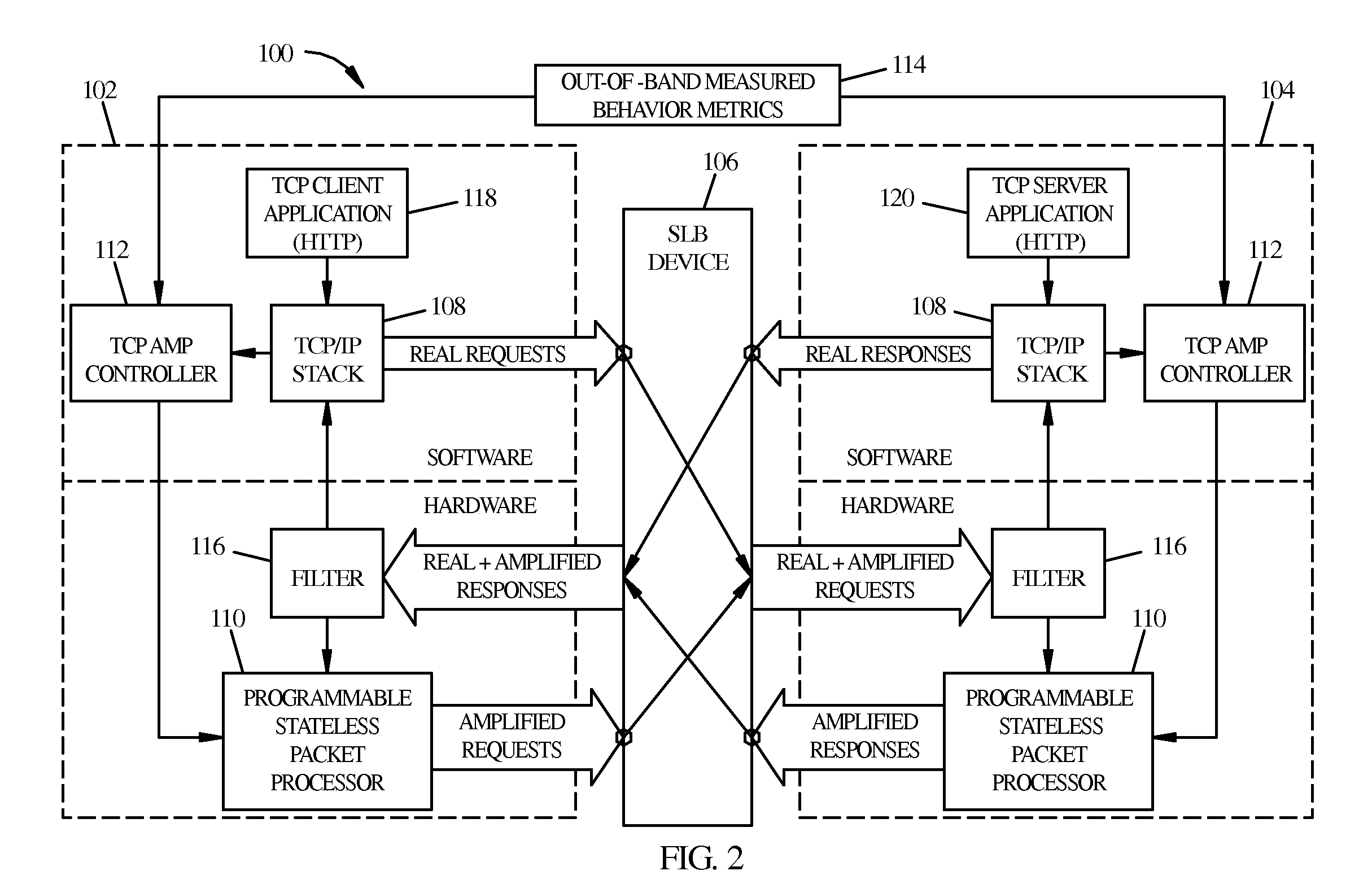

Method For Testing Stateful Network Communications Devices

InactiveUS20070121516A1Reduce the amount of hardwareReduce the amount requiredError preventionTransmission systemsData packNetwork communication

There is disclosed a method for testing a stateful network communications device. A plurality of stateful and simulated stateless connections are established with the device under test. Packets are sent to the device under test, and responses are received from the device enter test, over the stateless and stateful connections. Measurements are obtained for at least one of the stateless and stateful connections.

Owner:KEYSIGHT TECH SINGAPORE (SALES) PTE LTD

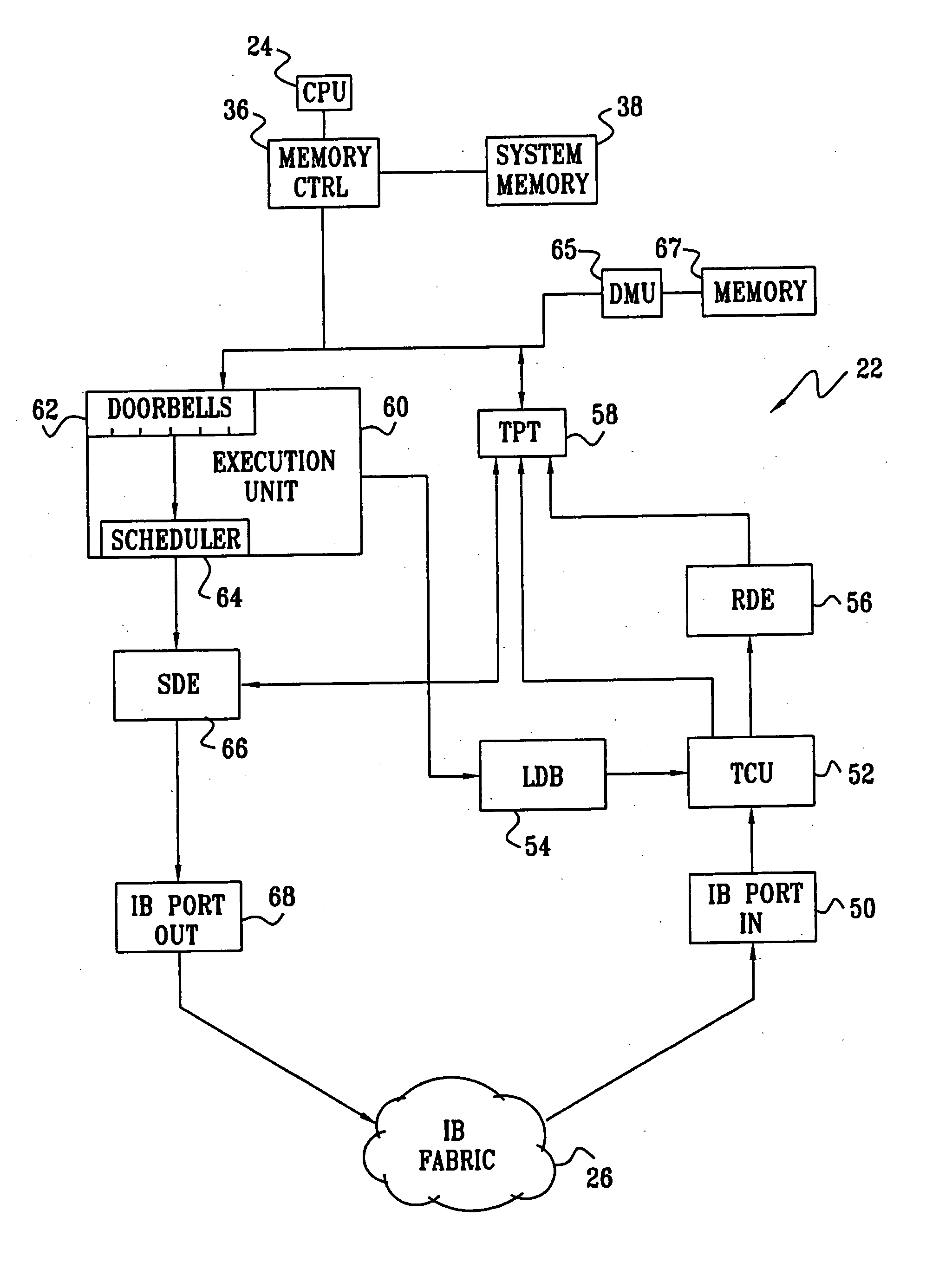

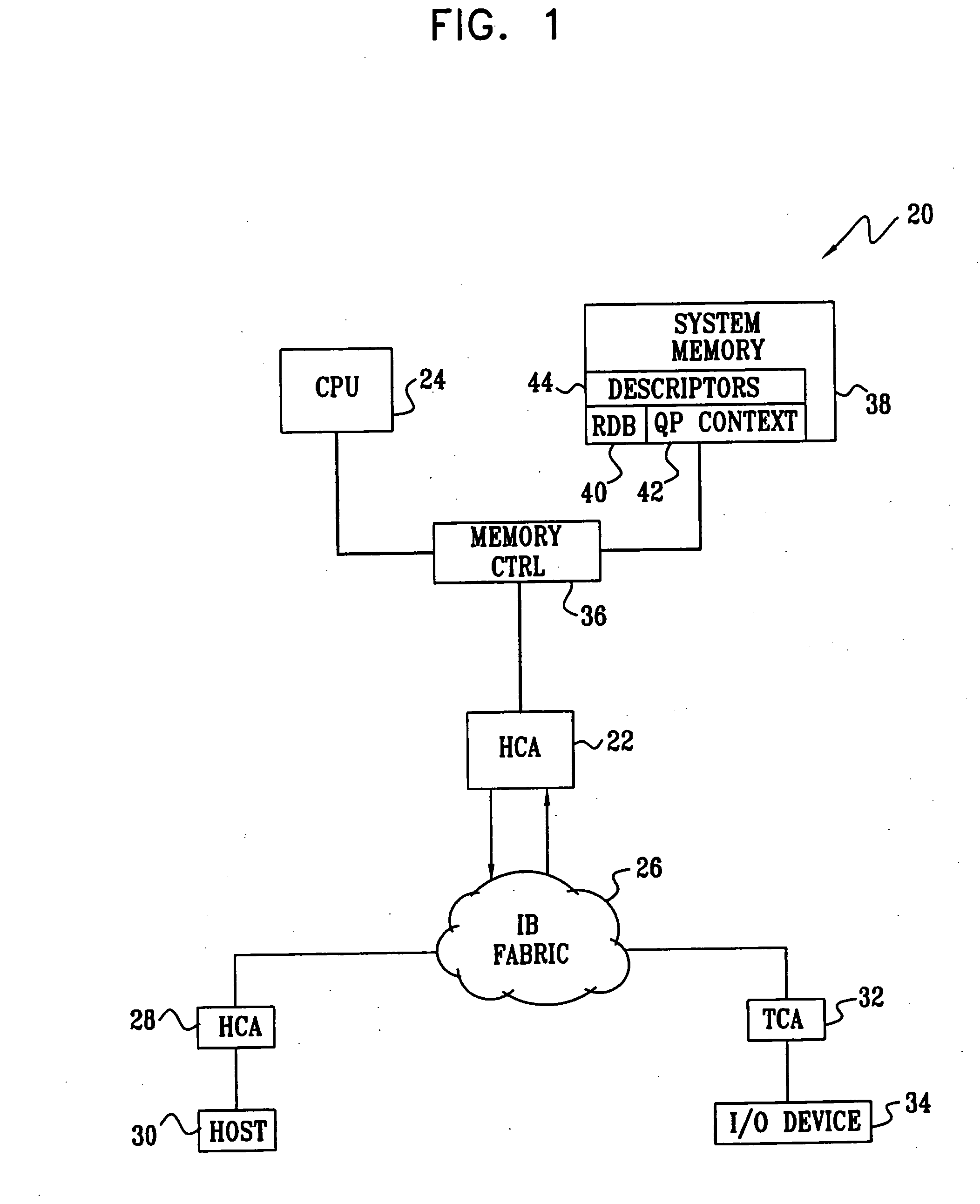

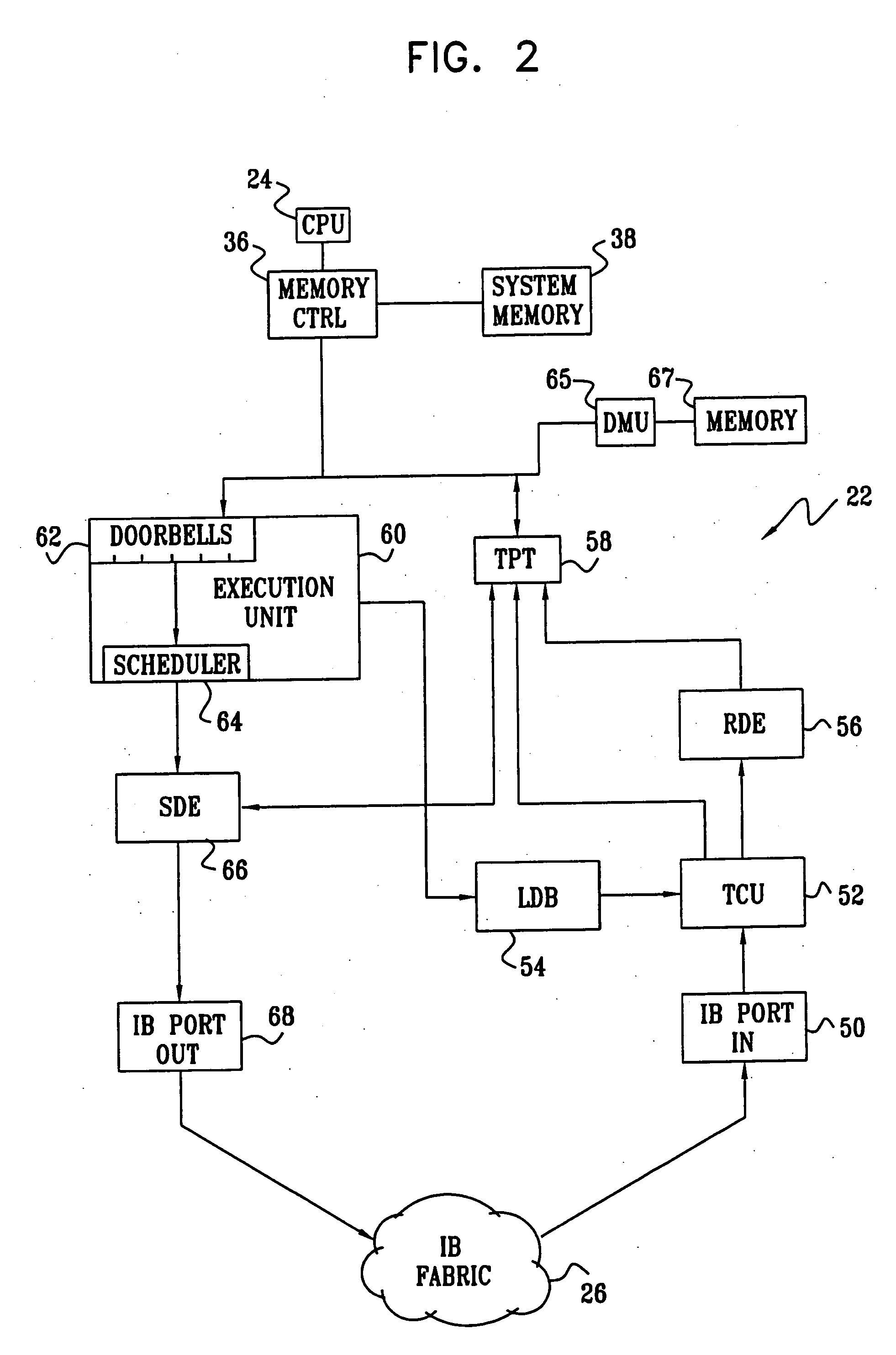

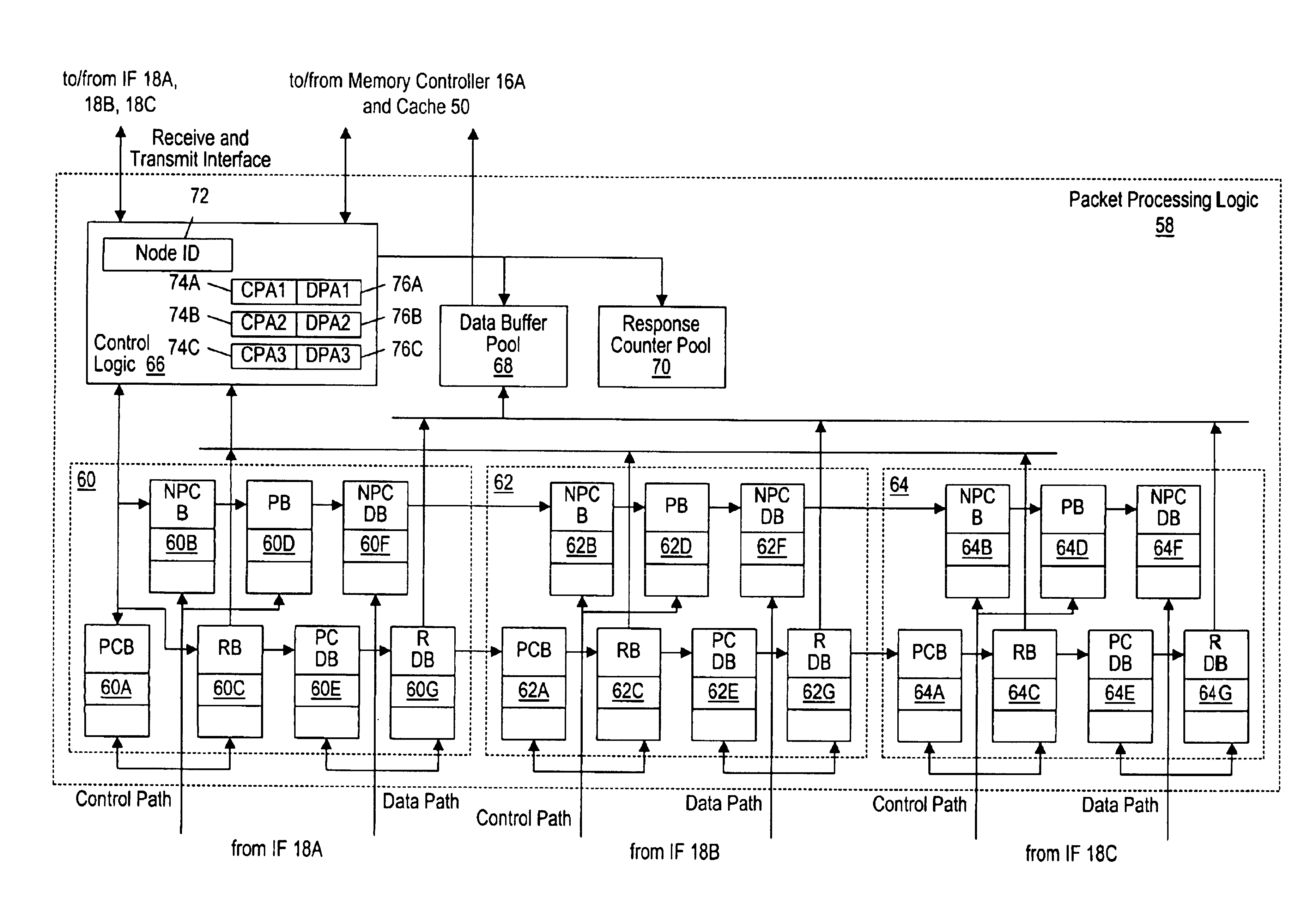

Network interface adapter with shared data send resources

InactiveUS20060129699A1Low hardware requirementsEfficient executionData switching by path configurationMultiple digital computer combinationsPacket generatorNetwork output

A network interface adapter includes an outgoing packet generator, adapted to generate an outgoing request packet for delivery to a remote responder responsive to a request submitted by a host processor and a network output port, coupled to transmit the outgoing request packet over a network to the remote responder. A network input port receives an incoming response packet from the remote responder, in response to the outgoing request packet sent thereto, as well as an incoming request packet sent by a remote requester. An incoming packet processor receives and processes both the incoming response packet and the incoming request packet, and causes the outgoing packet generator, responsive to the incoming request packet, to generate, in addition to the outgoing request packet, an outgoing response packet for transmission to the remote requester.

Owner:MELLANOX TECHNOLOGIES LTD

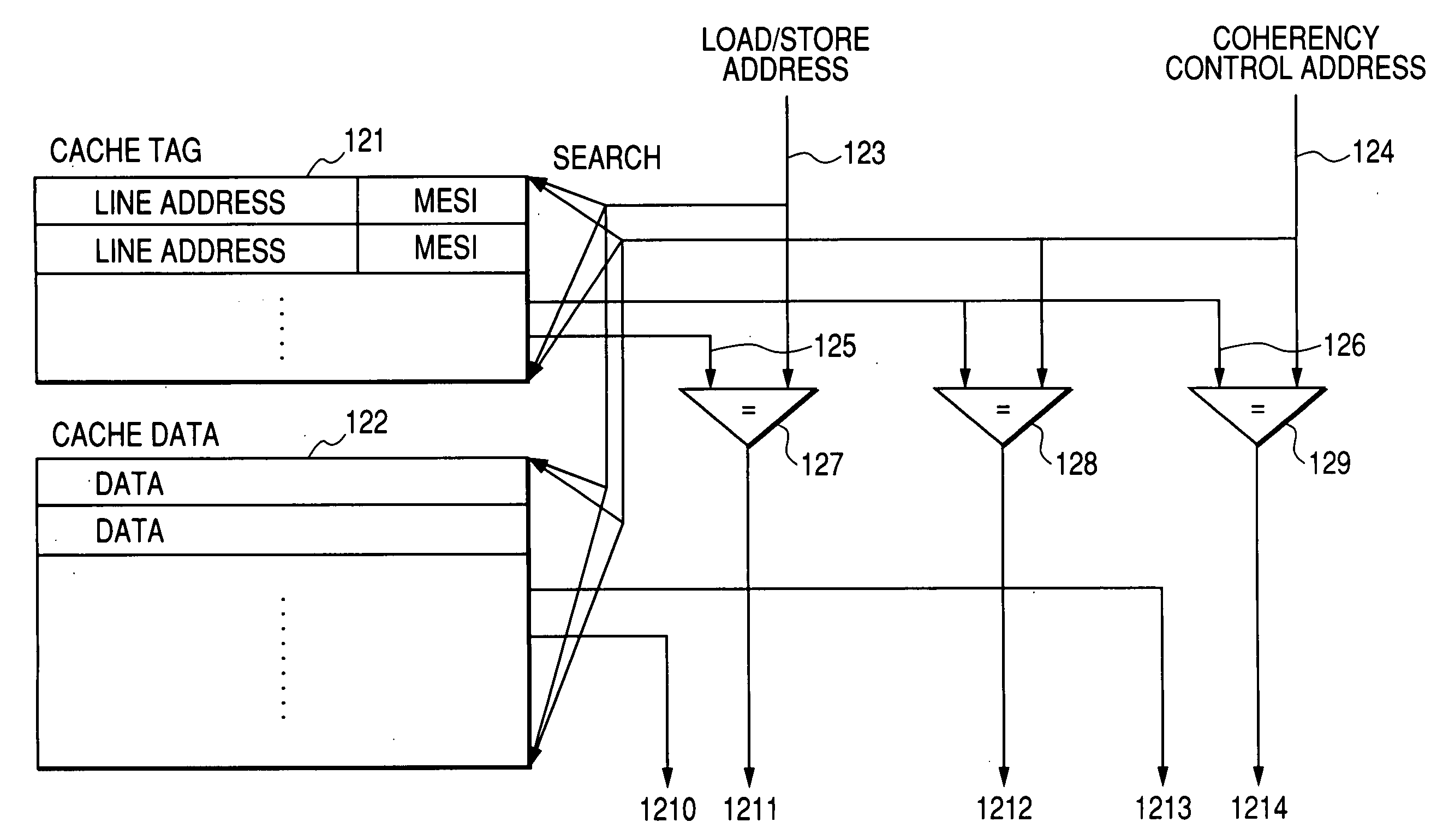

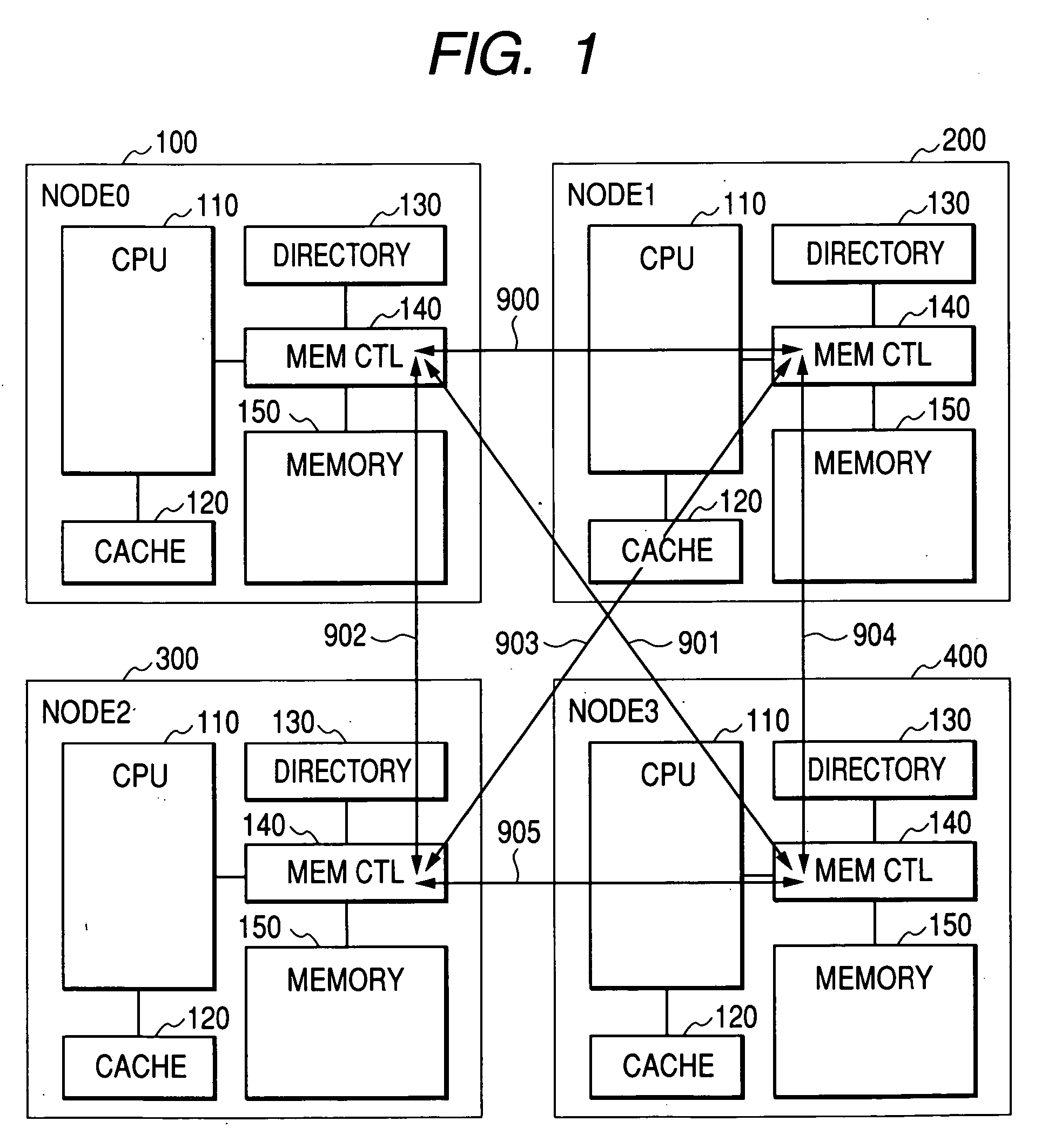

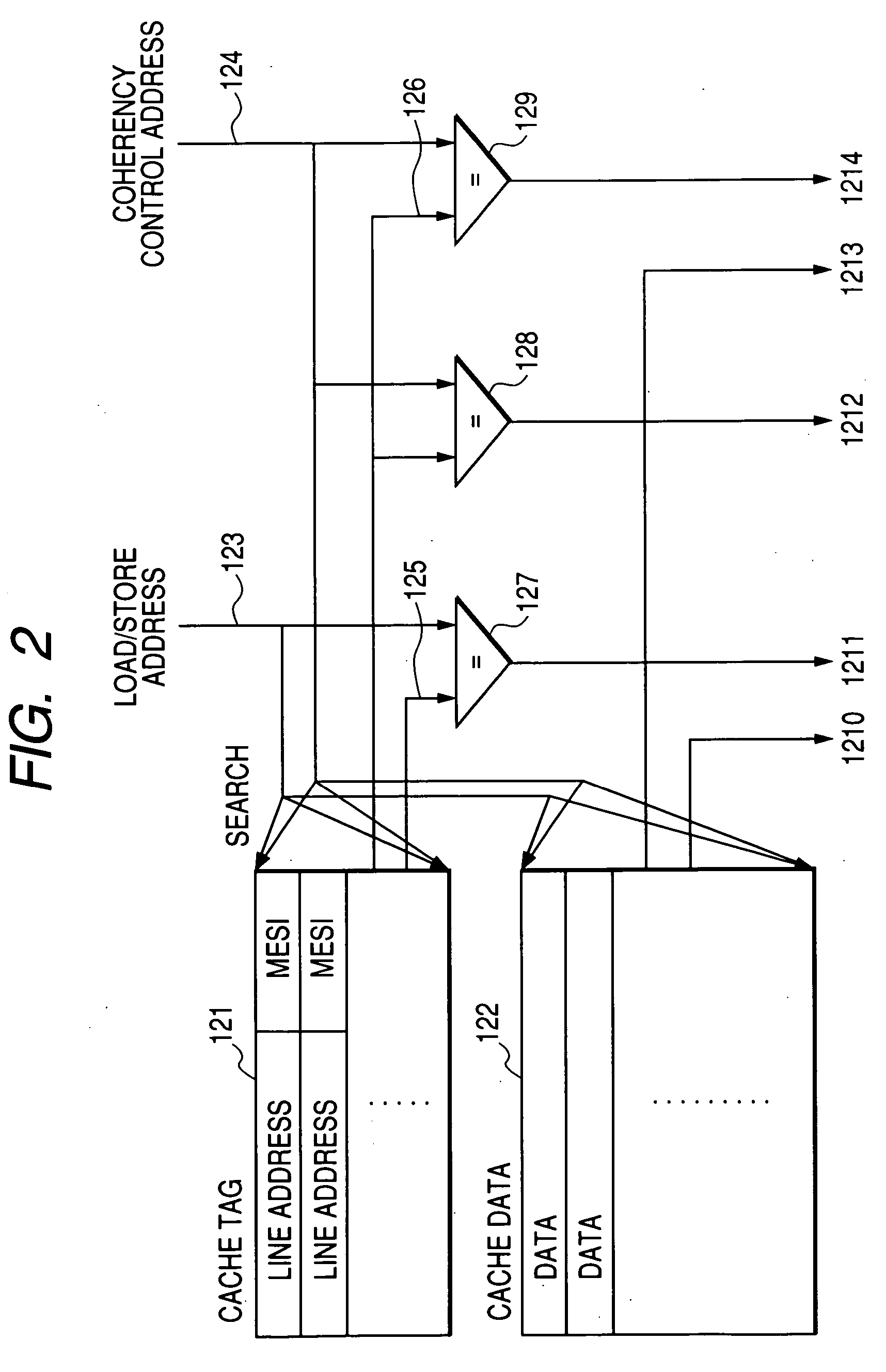

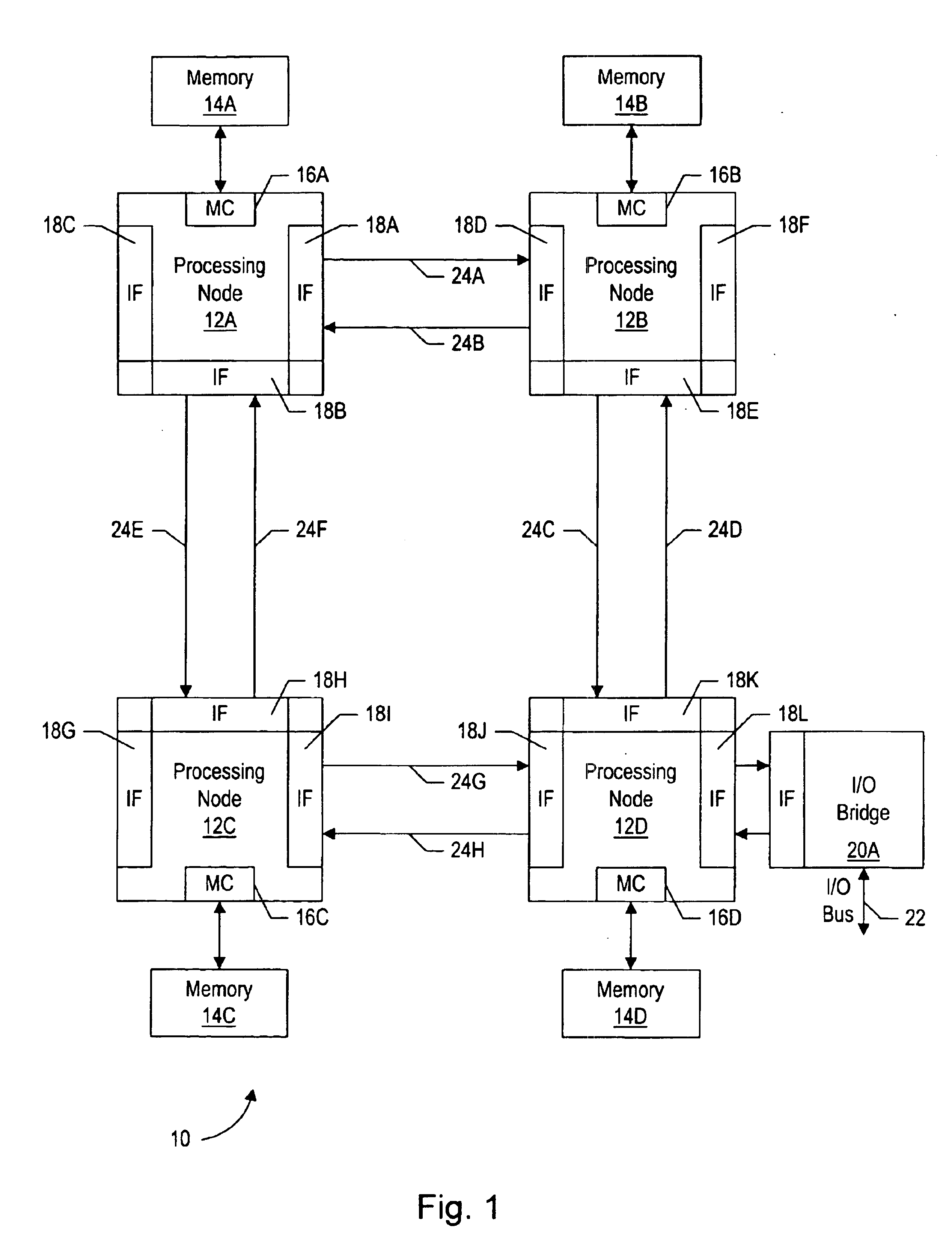

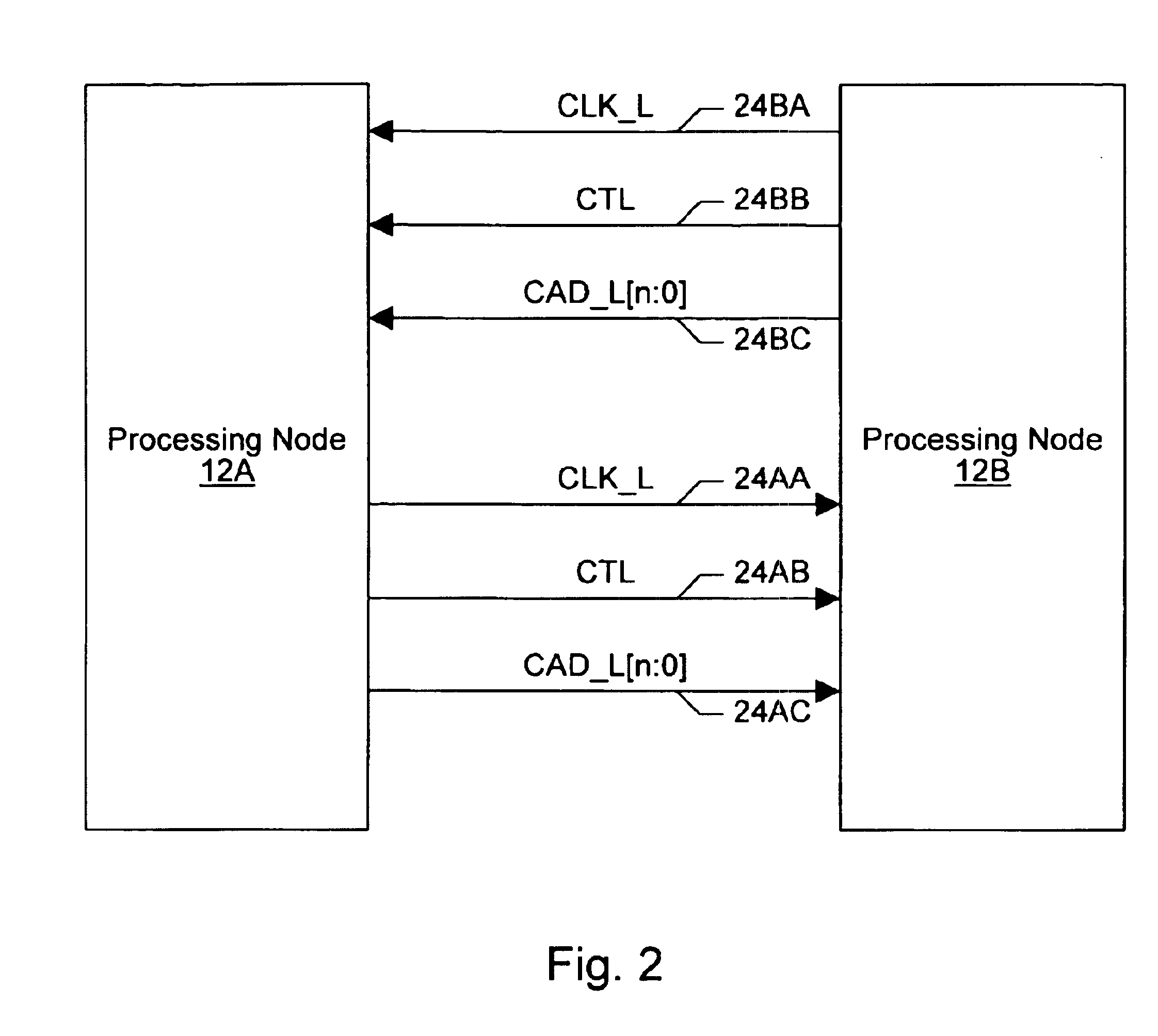

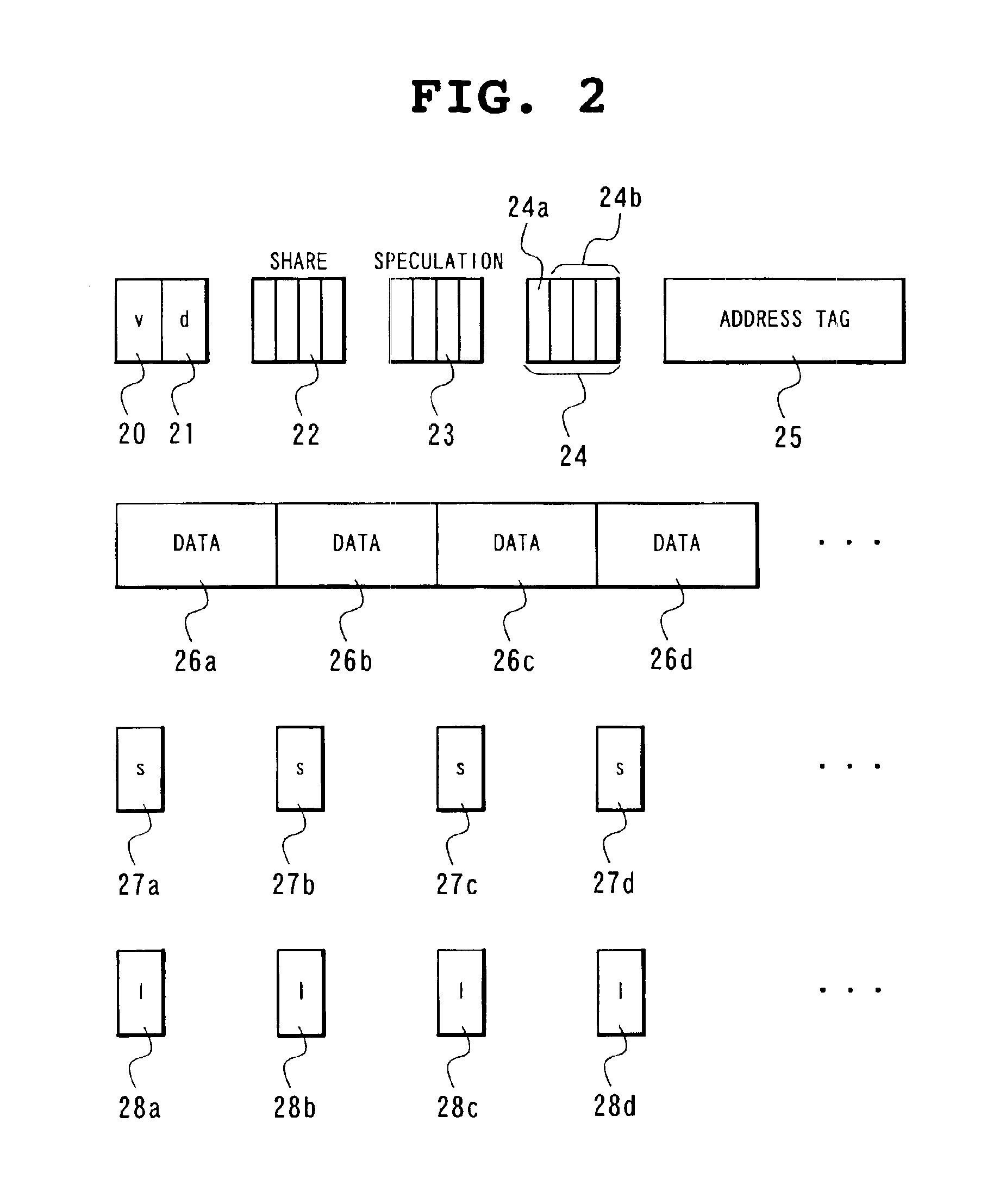

Multiprocessor system

InactiveUS20050198441A1Reduce the amount of hardwareReduce the amount requiredMemory adressing/allocation/relocationMemory addressMulti processor

A shared memory multiprocessor is provided which includes a plurality of nodes connected to one another. Each node includes: a main memory for storing data; a cache memory for storing a copy of data obtained from the main memory; and a CPU for accessing the main memory and the cache memory and processing data. The node further includes a directory and a memory region group. The directory is made up of directory entries each including one or more directory bits which each indicate whether the cache memory of another node stores a copy of a part of a memory region group of the main memory of this node. The memory region group includes of memory regions having the same memory address portion including a cache index portion. Each node is assigned to one of the one or more directory bits.

Owner:HITACHI LTD

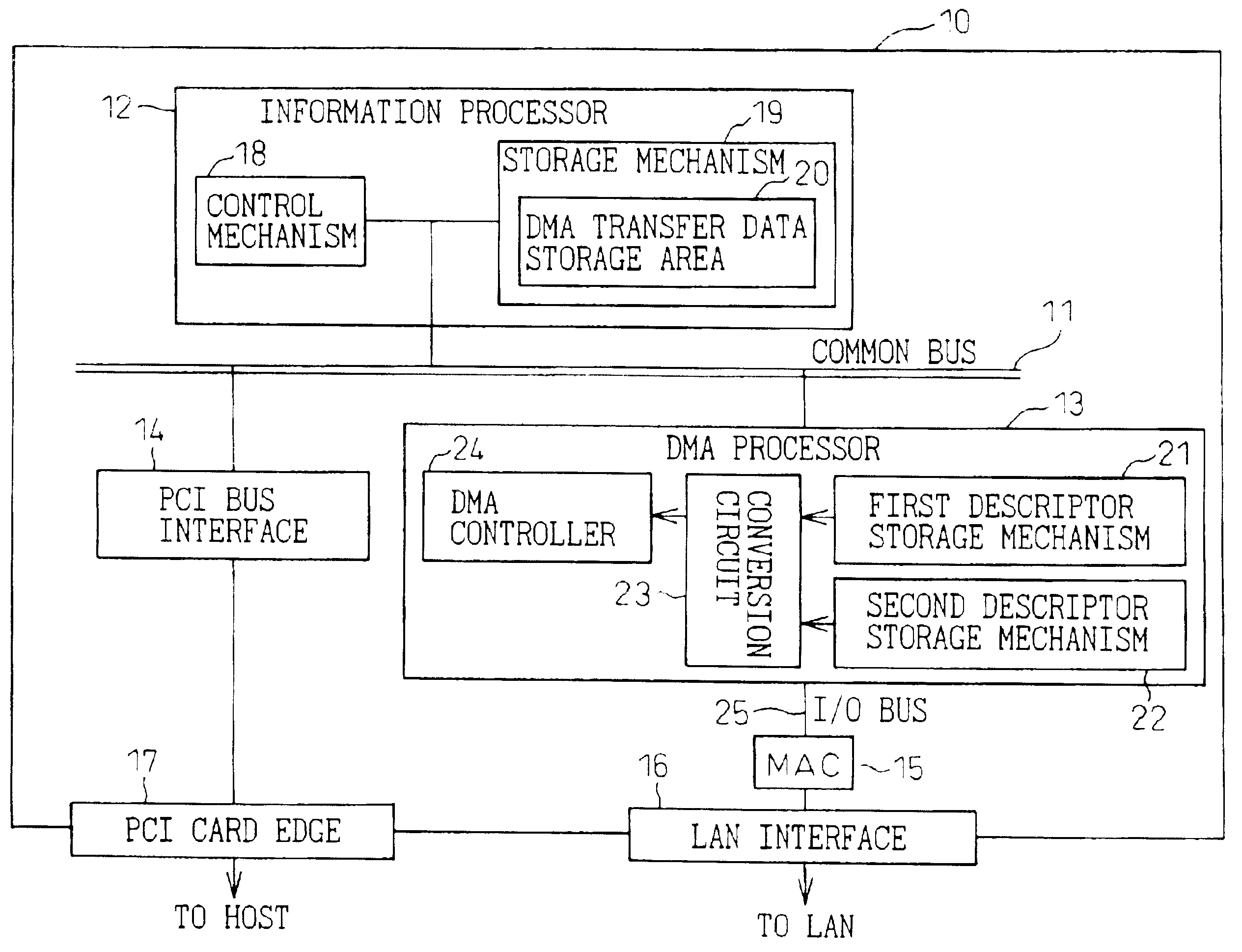

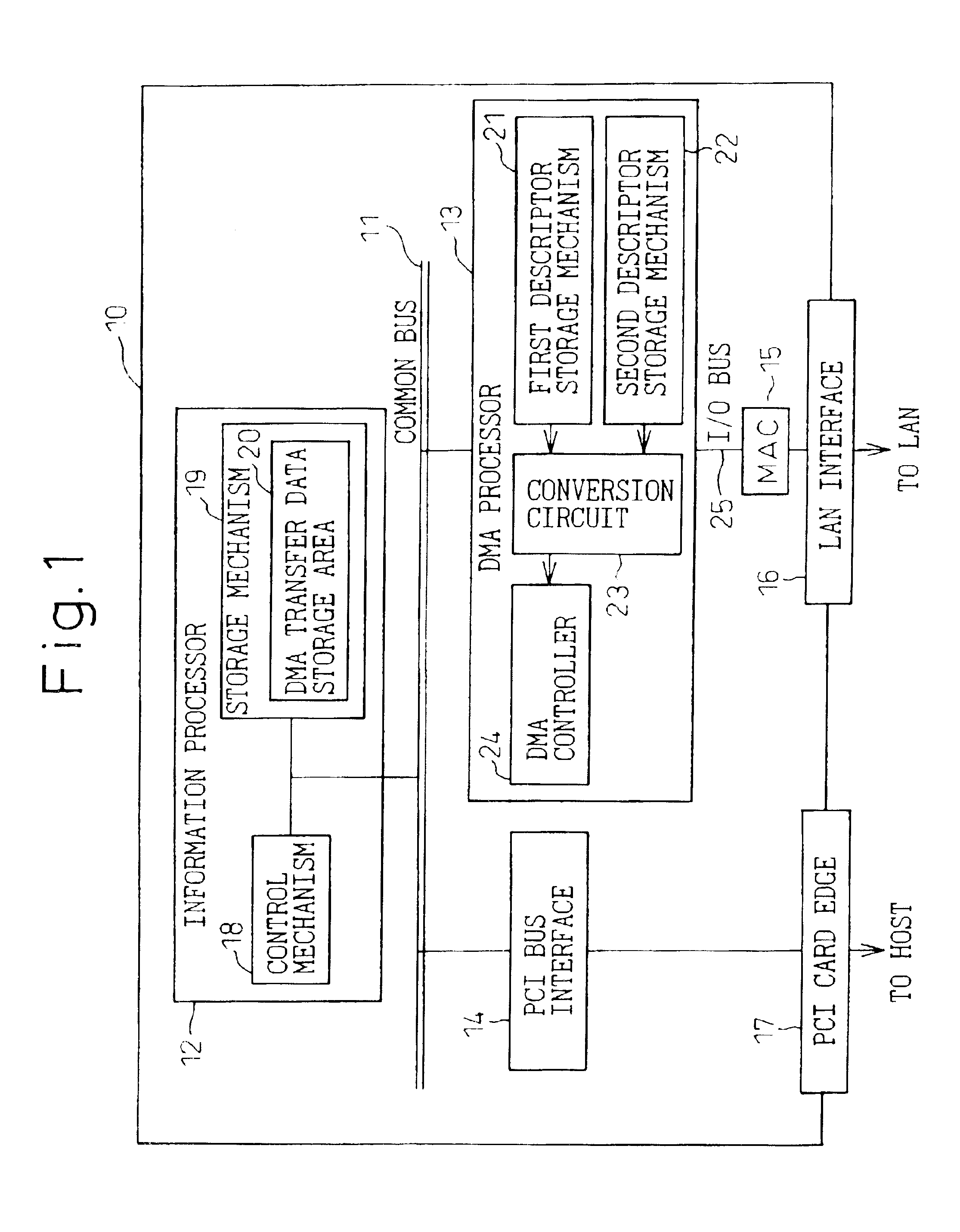

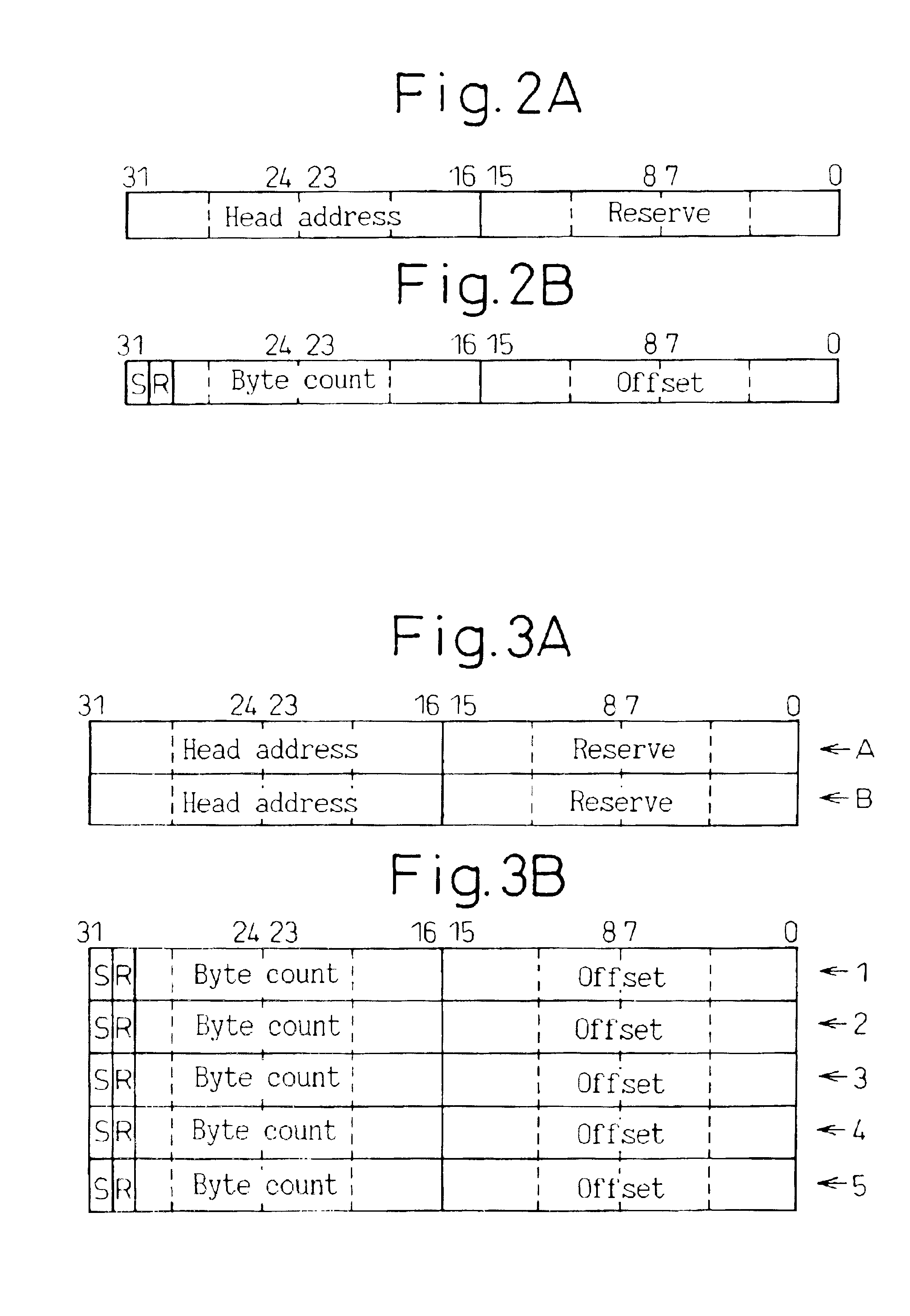

Data transfer apparatus and method

InactiveUS6954806B2Improve system performanceReduce the amount of hardwareElectric digital data processingData transmissionEmbedded system

A data transfer apparatus and method that can make efficient use of a memory and a common bus by controlling a DMA controller through descriptor control, and can thereby achieve a data transfer with increased communication processing speed. The data transfer apparatus, which executes a DMA transfer by controlling the DMA controller through the use of a descriptor, includes: a first storage mechanism for storing descriptor common information that can be shared among a plurality of descriptors; a second storage mechanism for storing descriptor individual information that differs for each individual descriptor; and a conversion circuit for taking as inputs the descriptor common information read out of the first storage mechanism and the descriptor individual information read out of the second storage mechanism, and for outputting descriptor information to be supplied to the DMA controller.

Owner:FUJITSU LTD

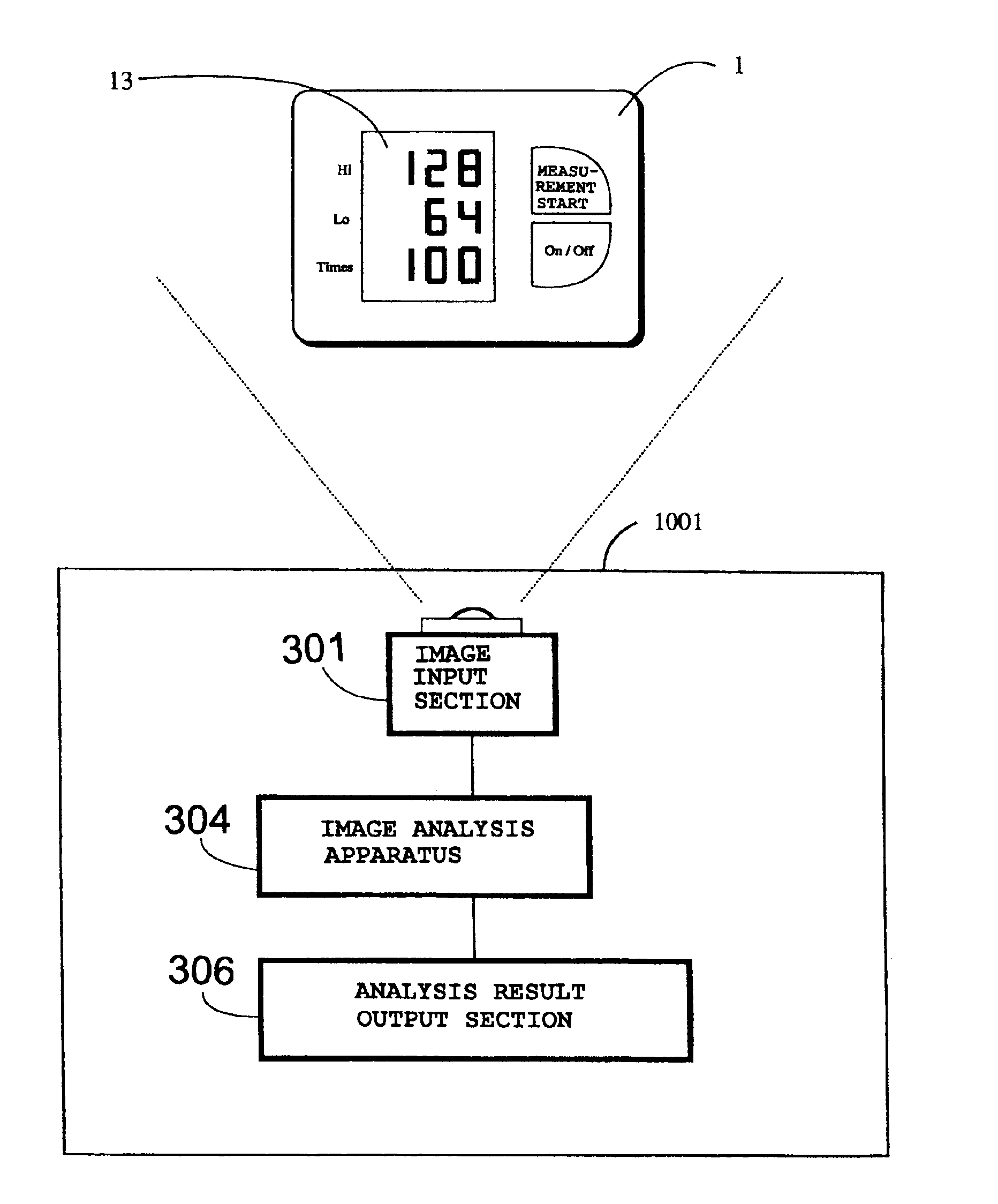

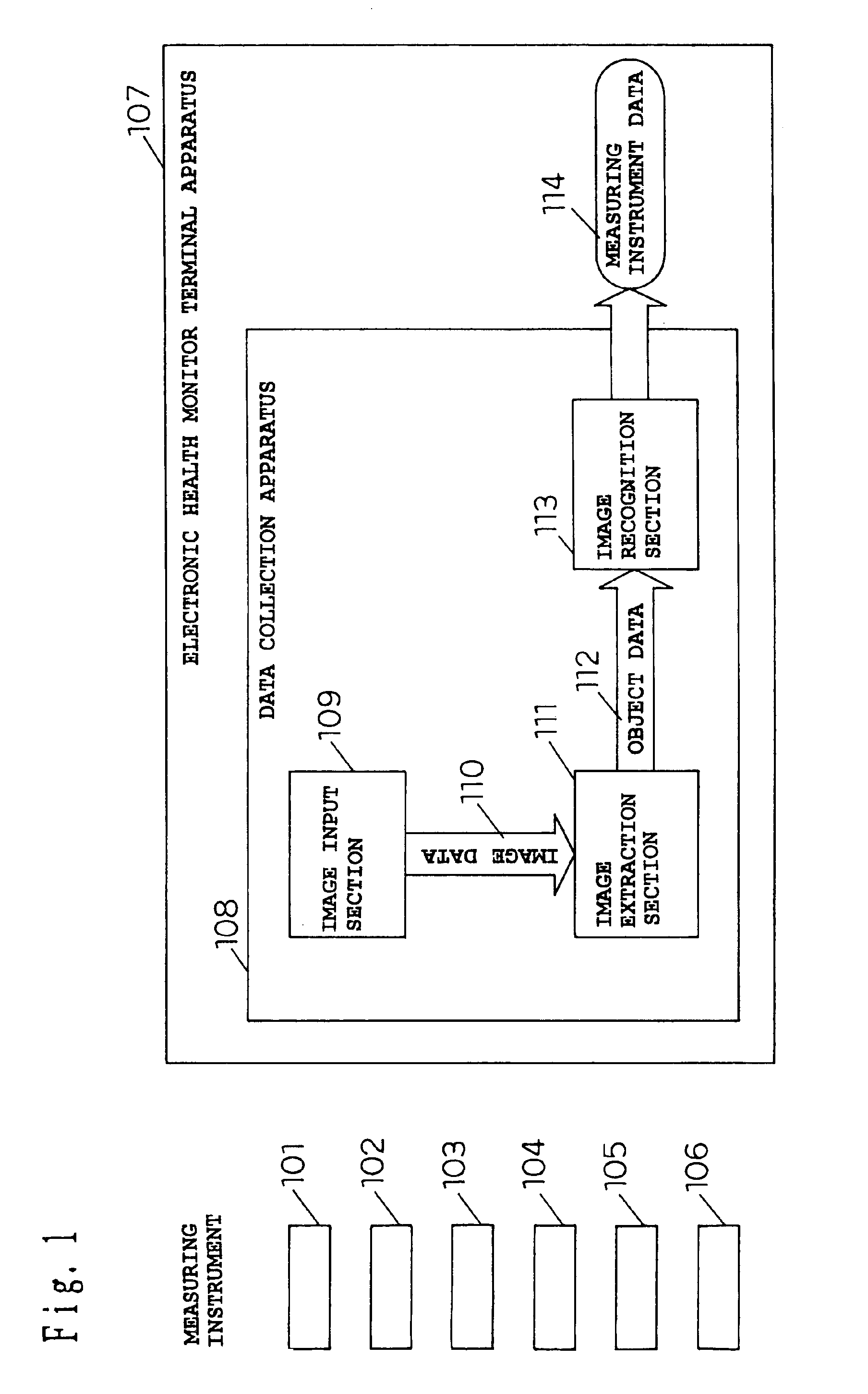

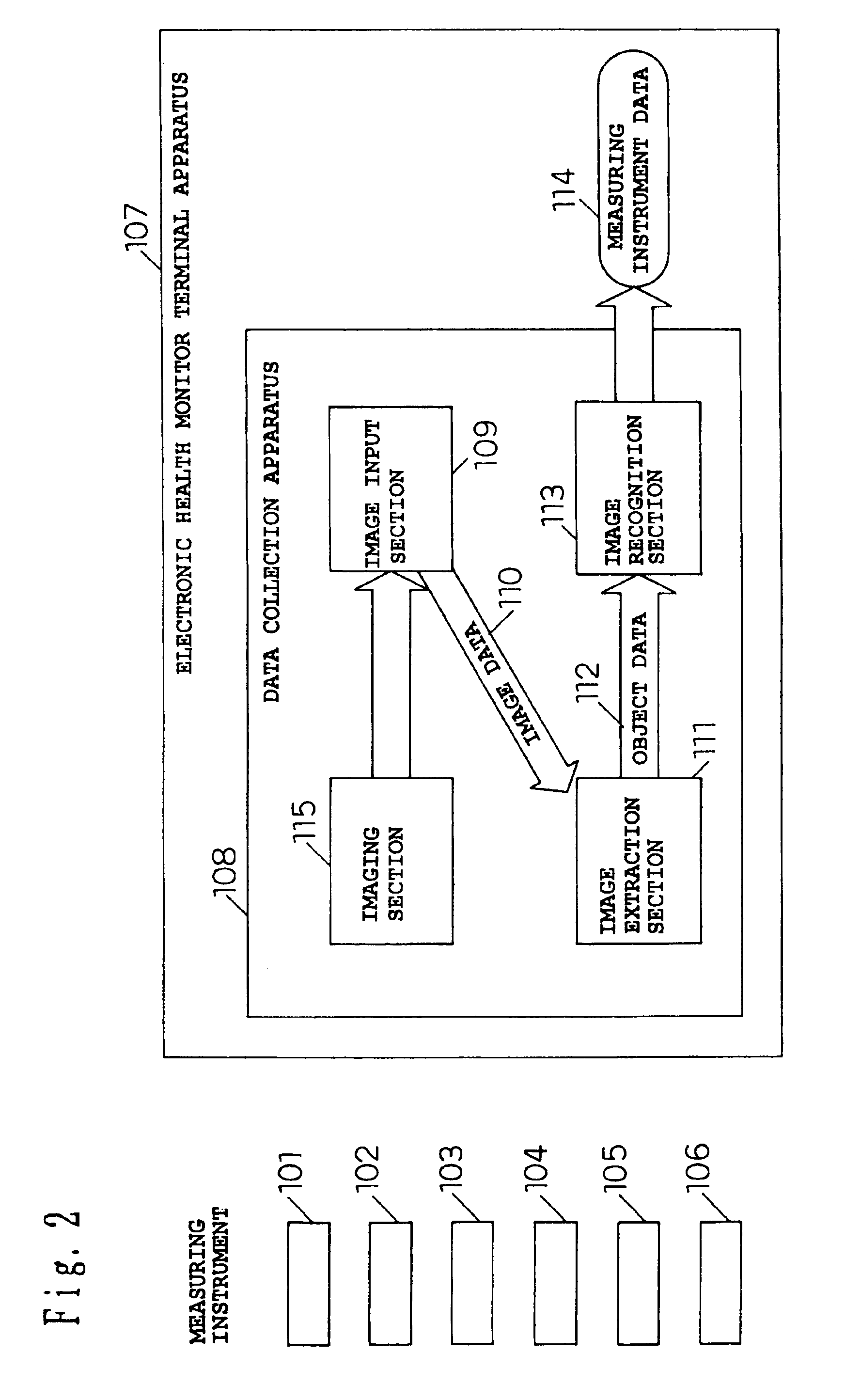

Data input apparatus, data input system, displayed data analyzing apparatus and medium

InactiveUS6909793B1Reduce the amount of hardwareLow costElectrocardiographyEvaluation of blood vesselsData displayMeasuring instrument

A data input apparatus that includes an image acquiring unit for acquiring the image of data displayed on the data display section of a measuring instrument, a number reading unit for reading numbers in the above described acquired image and a display unit for displaying the numbers read, with the above described image acquiring unit also acquiring the image of a portion other than the data display section of the above described measuring instrument at the same time, the image recognition unit reading information on the above described measuring instrument other than the above described numbers from the acquired image and the information on the read measuring instrument being used when the above described number reading unit reads numbers.

Owner:PANASONIC INTELLECTUAL PROPERTY CORP OF AMERICA

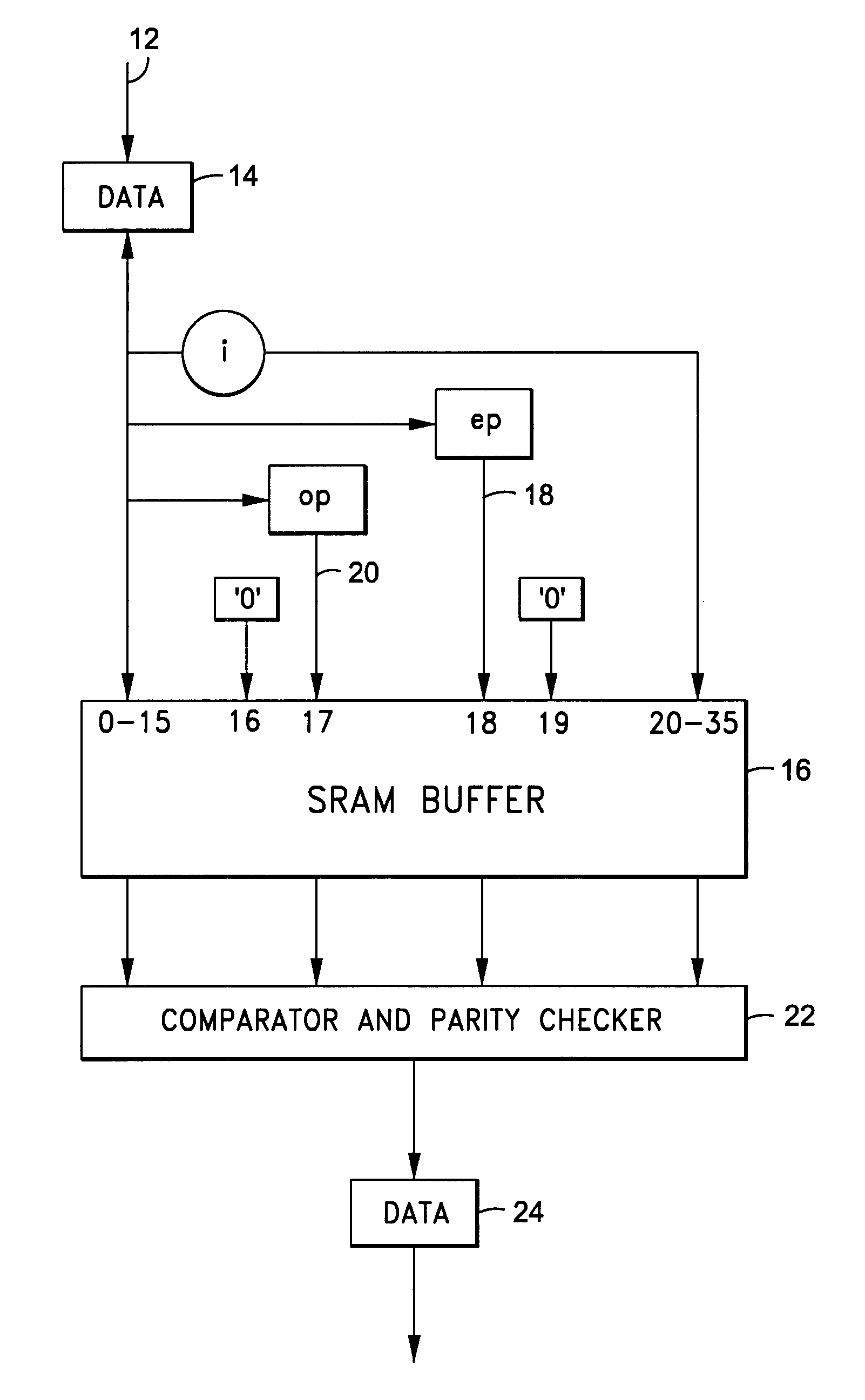

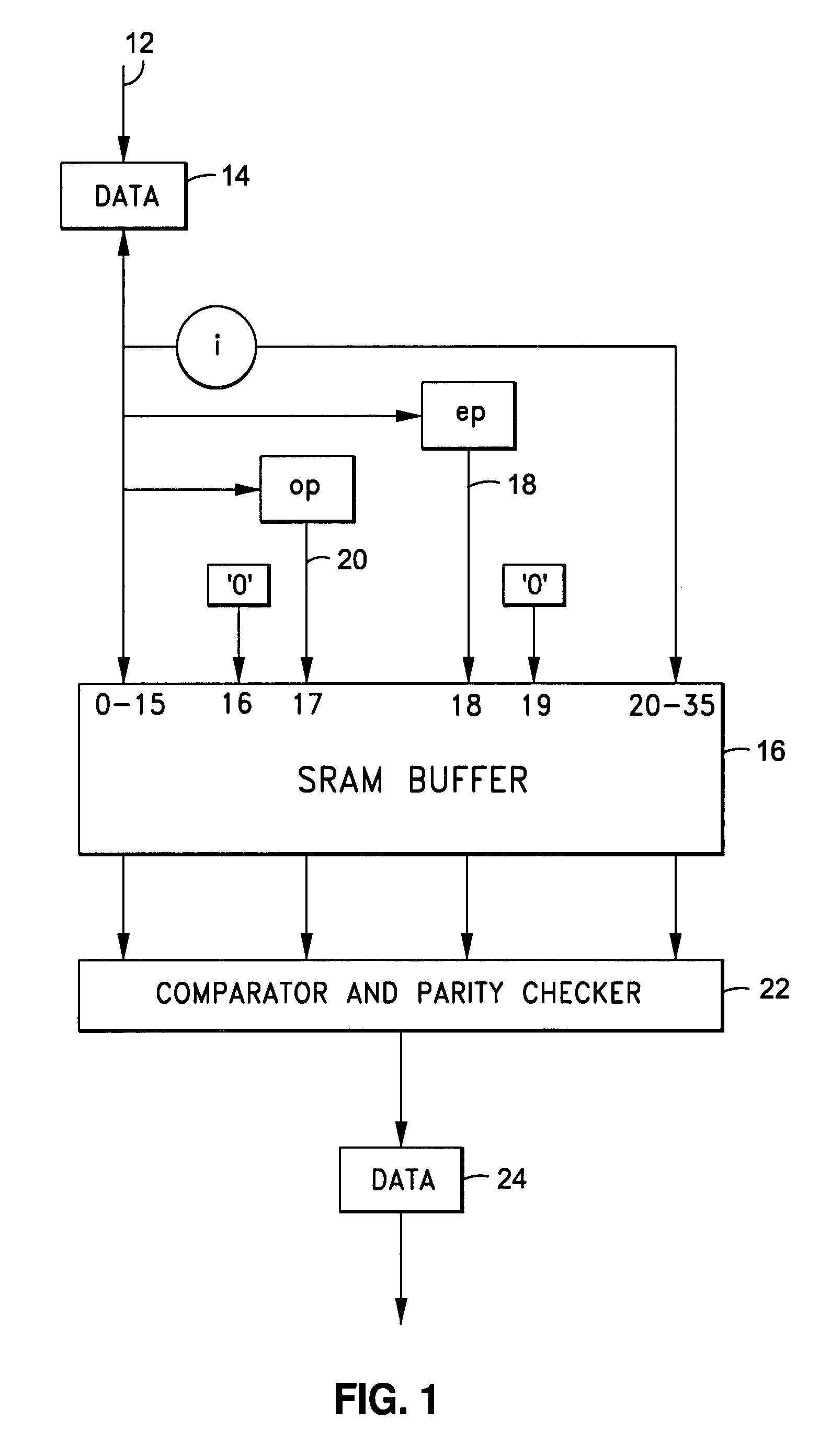

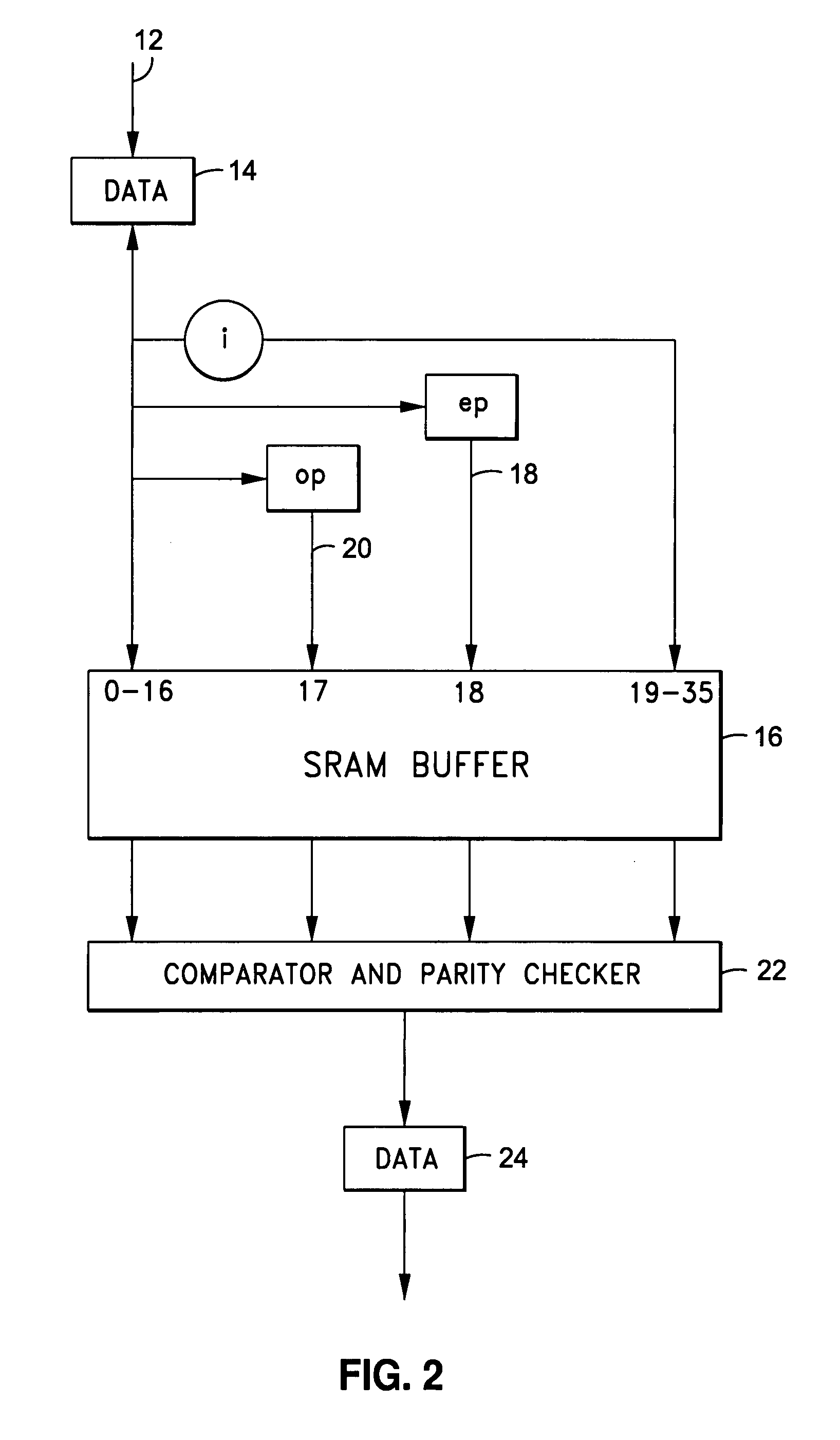

Multiple bit upset insensitive error detection and correction circuit for field programmable gate array based on static random access memory blocks

ActiveUS7865805B1Improve efficiencyReduce the amount of hardwareError detection/correctionDigital storageData streamStatic random-access memory

A method for detecting and correcting bit errors. The method includes the steps of receiving original data, partitioning the memory storage into a first portion and a second portion, storing the original data in the first portion of the memory buffer, modifying the original data into modified data, storing the modified data in the second portion of the memory buffer, comparing the original data with the modified data, combining the original data and the modified data to create a final data stream, and outputting the final data stream. The method may further include the step of calculating and storing parity data.

Owner:LOCKHEED MARTIN CORP

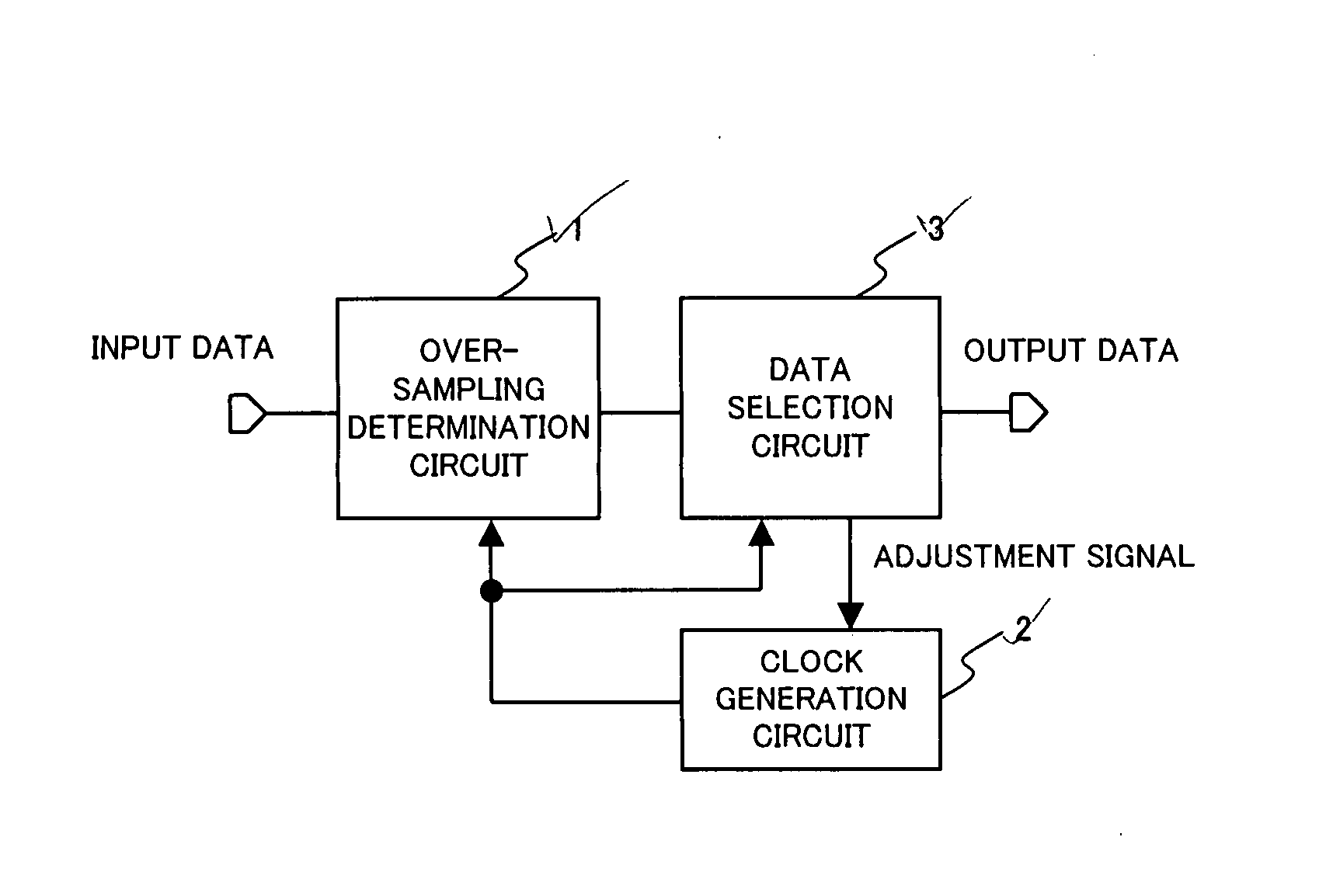

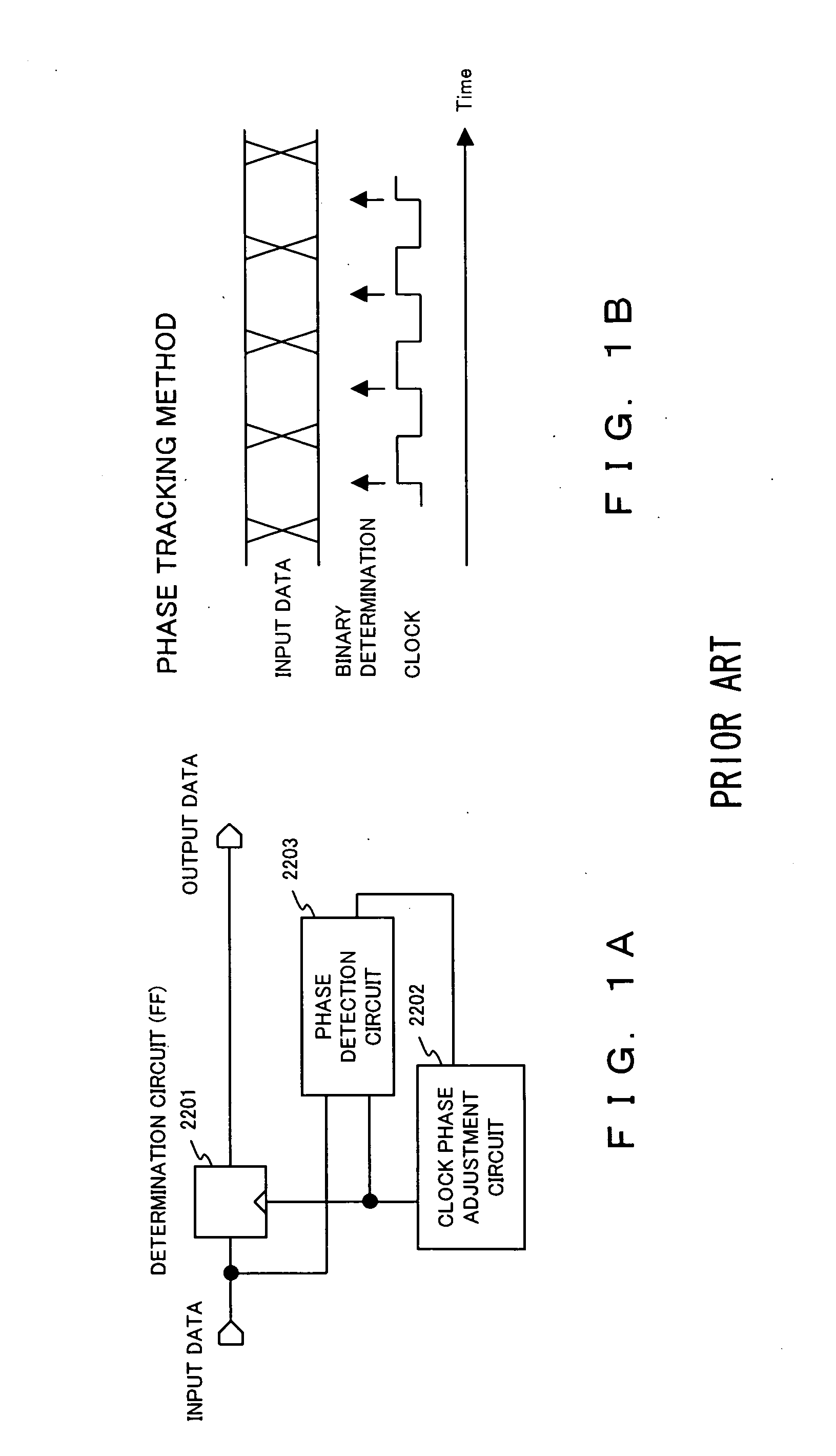

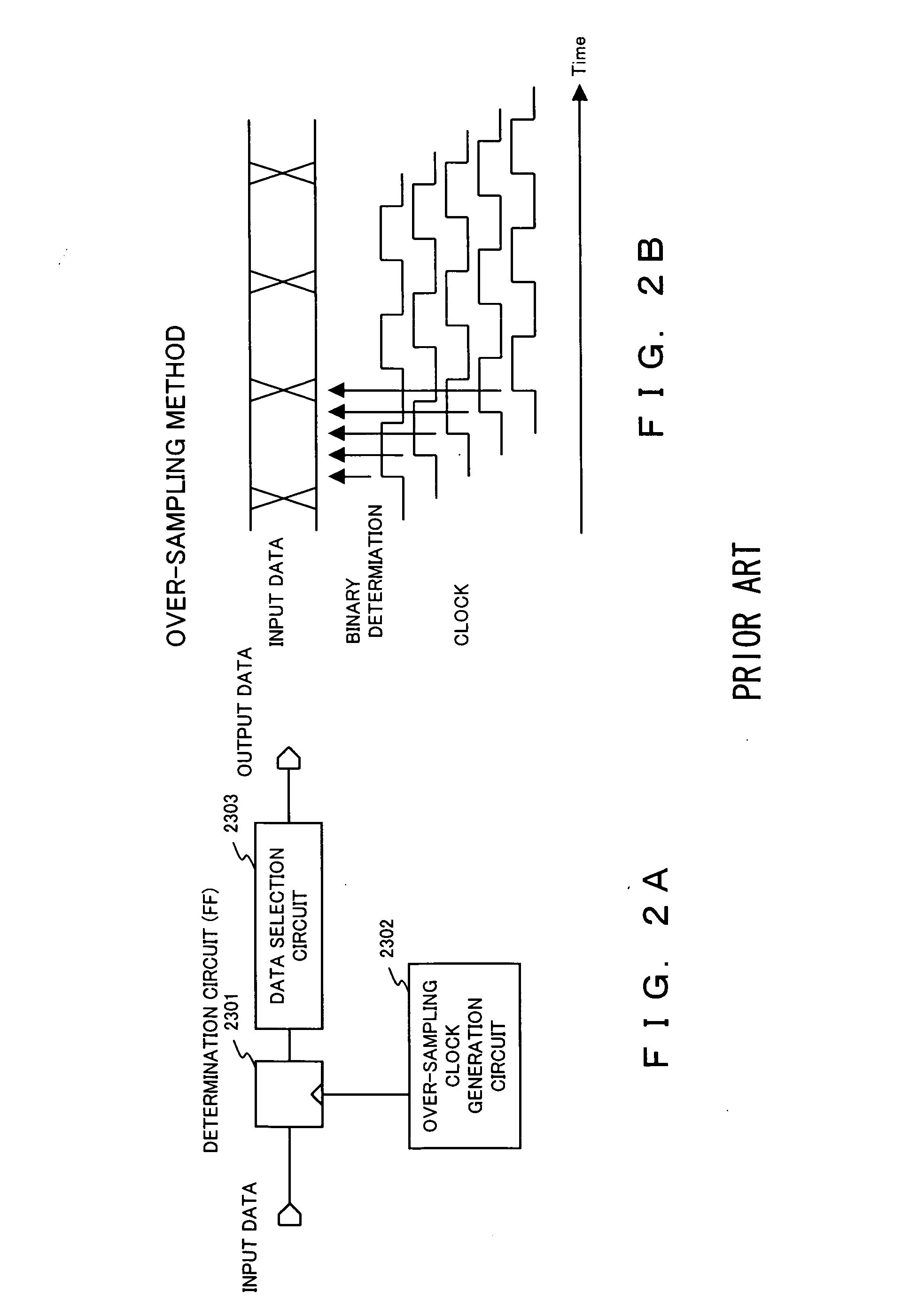

Data reproduction circuit

InactiveUS20070064850A1High jitter tracking capabilityReduce the amount of hardwareAngle demodulation by phase difference detectionSynchronising arrangementData selectionData rate

This is a data reproduction circuit for receiving data and reproducing the data and its clock which comprises an over-sampling determination circuit for sampling the received data by a clock with frequency higher than the data rate of the received data and converting the sampled data into digital signals, a circuit for selecting and outputting the reproduced data, a phase error detection circuit for detecting a phase error from its timing deviation with the received data, based on the reproduced clock, a data selection circuit for adjusting its phase, based on the output of the phase error detection circuit, a phase adjustment circuit for adjusting the phase of the reproduced clock to reproduce a new clock and a clock generation circuit for supplying the over-sampling determination circuit and the data selection circuit with the newly reproduced clock.

Owner:FUJITSU LTD

Response virtual channel for handling all responses

InactiveUS6888843B2Deadlock-free operationReduce the amount of hardwareStore-and-forward switching systemsElectric digital data processingNetwork packetComputerized system

A computer system employs virtual channels and allocates different resources to the virtual channels. Packets which do not have logical / protocol-related conflicts are grouped into a virtual channel. Accordingly, logical conflicts occur between packets in separate virtual channels. The packets within a virtual channel may share resources (and hence experience resource conflicts), but the packets within different virtual channels may not share resources. Since packets which may experience resource conflicts do not experience logical conflicts, and since packets which may experience logical conflicts do not experience resource conflicts, deadlock-free operation may be achieved. Additionally, nodes within the computer system may be configured to preallocate resources to process response packets. Some response packets may have logical conflicts with other response packets, and hence would normally not be allocable to the same virtual channel. However, by preallocating response-processing resources, response packets are accepted by the destination node. Thus, any resource conflicts which may occur are temporary (as the response packets which make forward progress are processable). Viewed in another way, response packets may be logically independent if the destination node is capable of processing the response packets upon receipt. Accordingly, a response virtual channel is formed to which each response packet belongs.

Owner:GLOBALFOUNDRIES INC

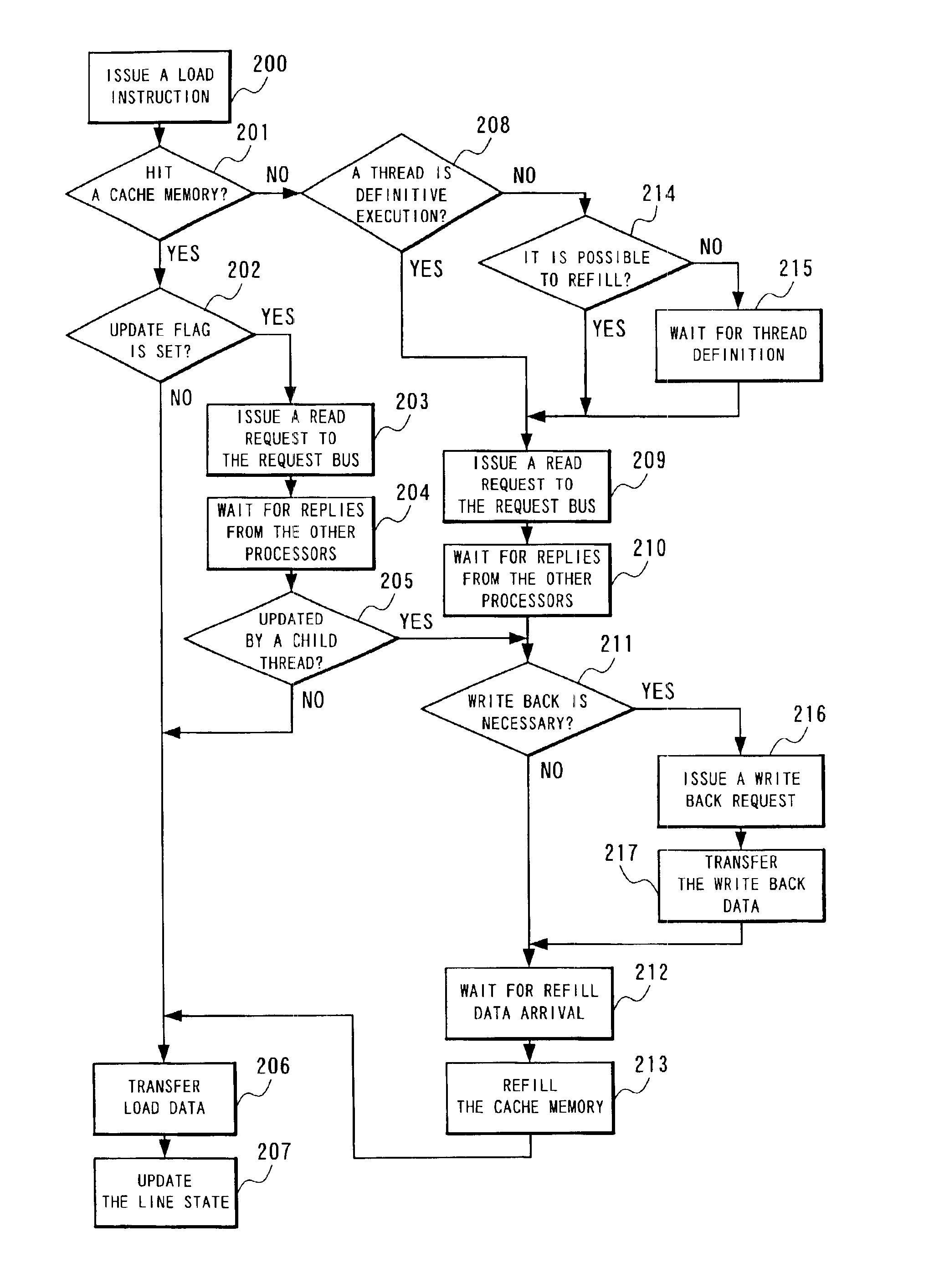

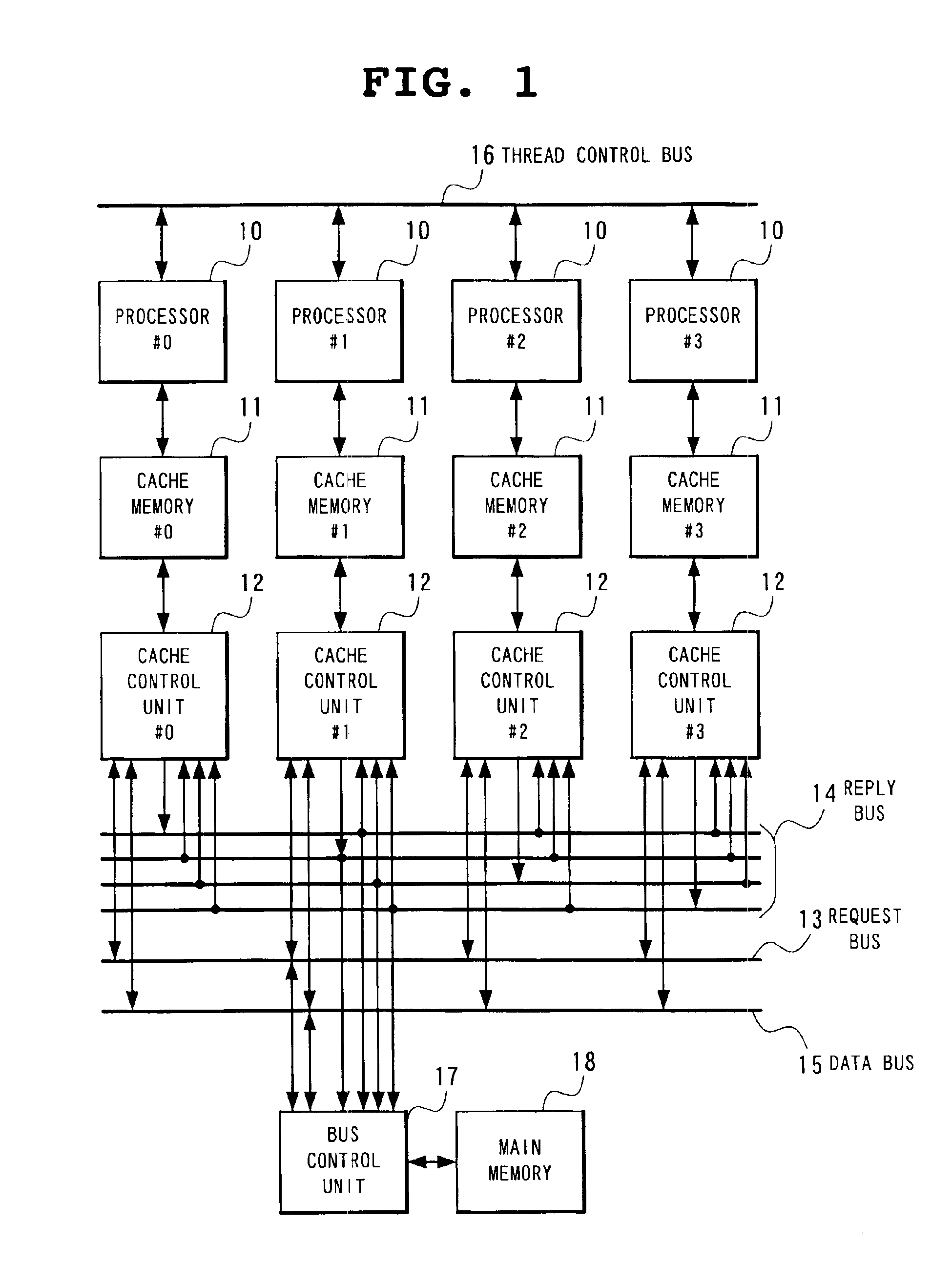

Speculative cache memory control method and multi-processor system

InactiveUS6950908B2SpeedReduce the amount of hardwareProgram synchronisationMemory adressing/allocation/relocationMulti processorParallel computing

The processors #0 to #3 execute a plurality of threads whose execution sequence is defined, in parallel. When the processor #1 that executes a thread updates the self-cache memory #1, if the data of the same address exists in the cache memory #2 of the processor #2 that executes a child thread, it updates the cache memory #2 simultaneously, but even if it exists in the cache memory #0 of the processor #0 that executes a parent thread, it doesn't rewrite the cache memory #0 but only records that rewriting has been performed in the cache memory #1. When the processor #0 completes a thread, a cache line with the effect that the data has been rewritten recorded from a child thread may be invalid and a cache line without such record is judged to be effective. Whether a cache line which may be invalid is really invalid or effective is examined during execution of the next thread.

Owner:NEC CORP

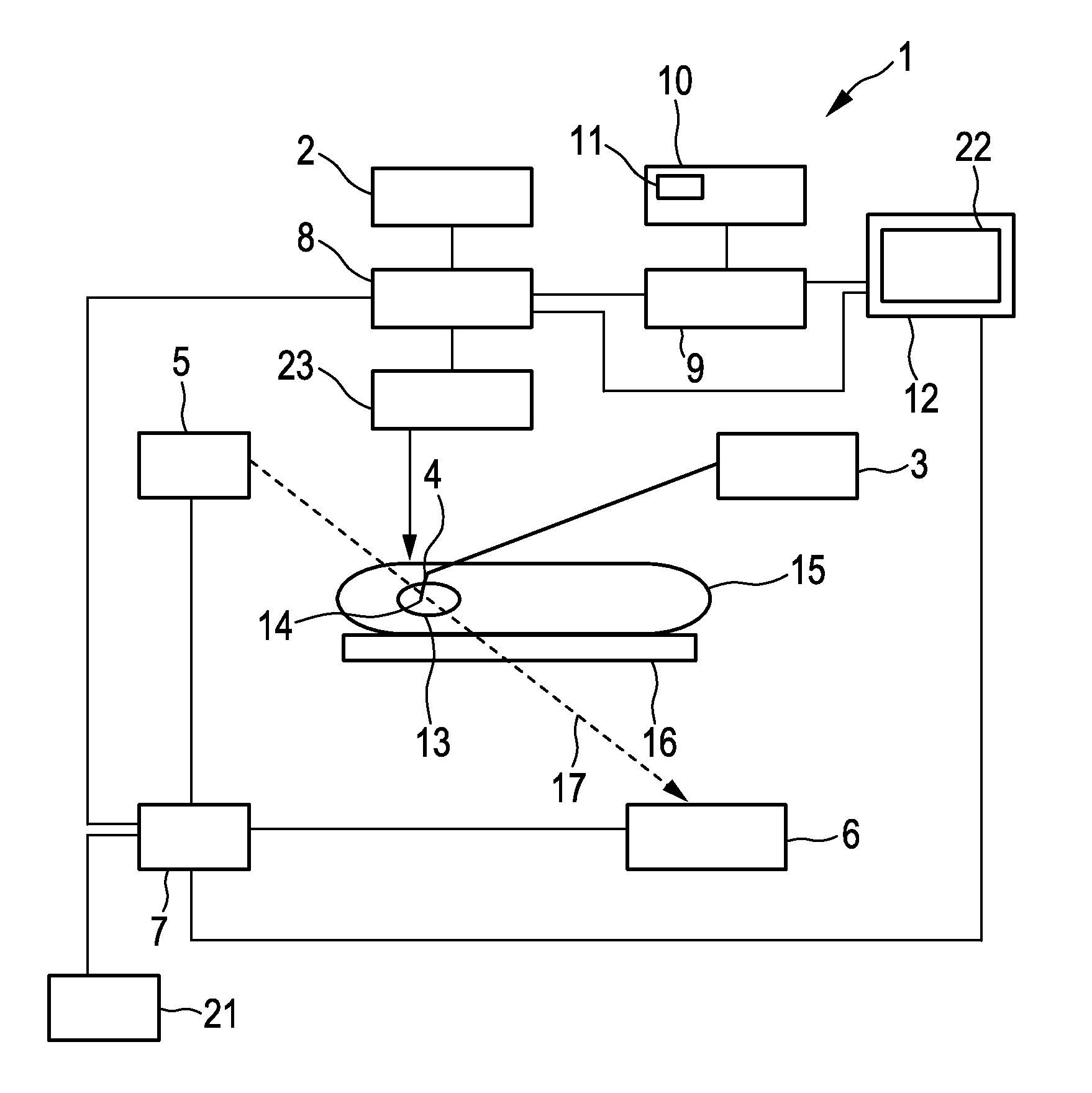

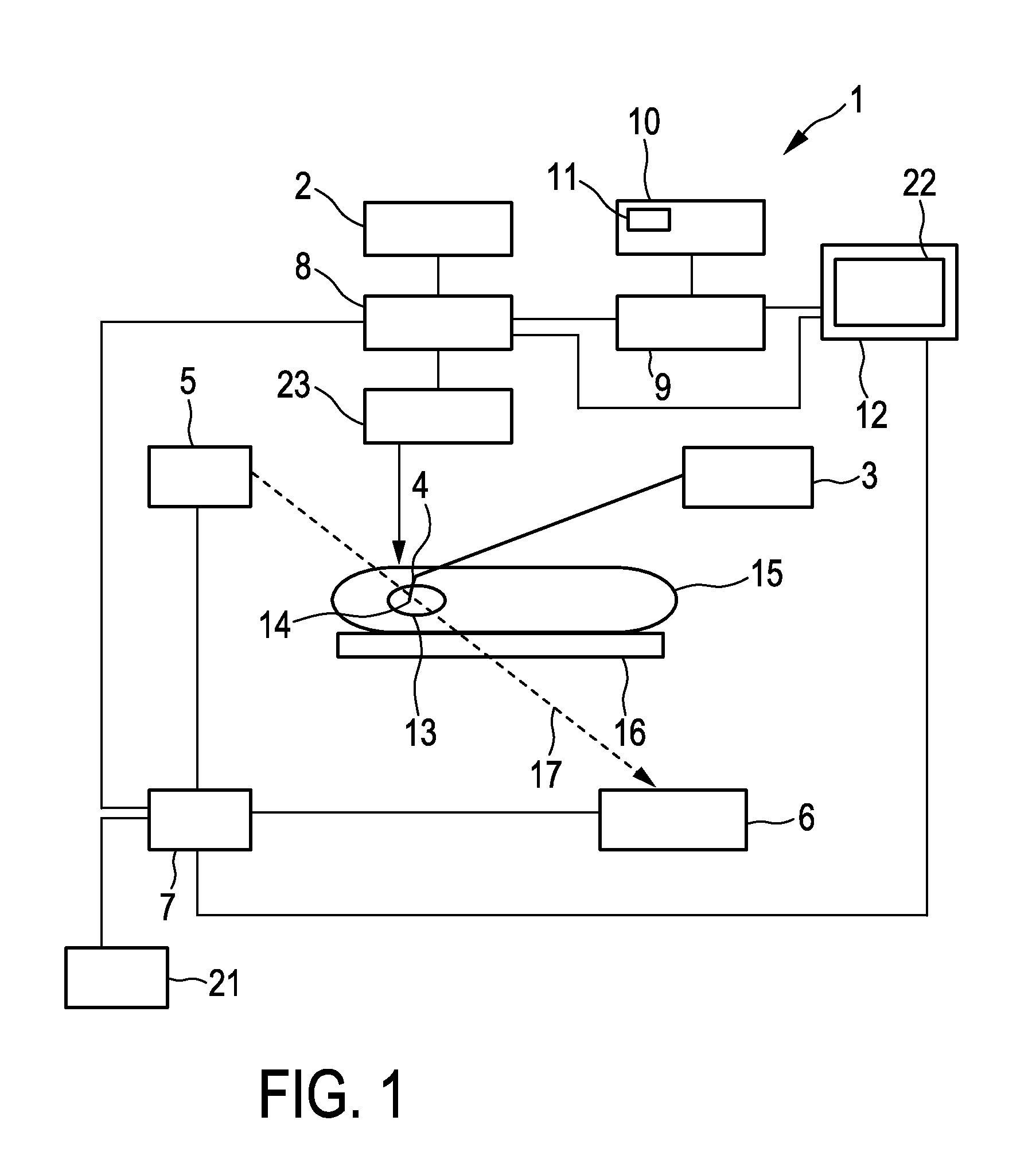

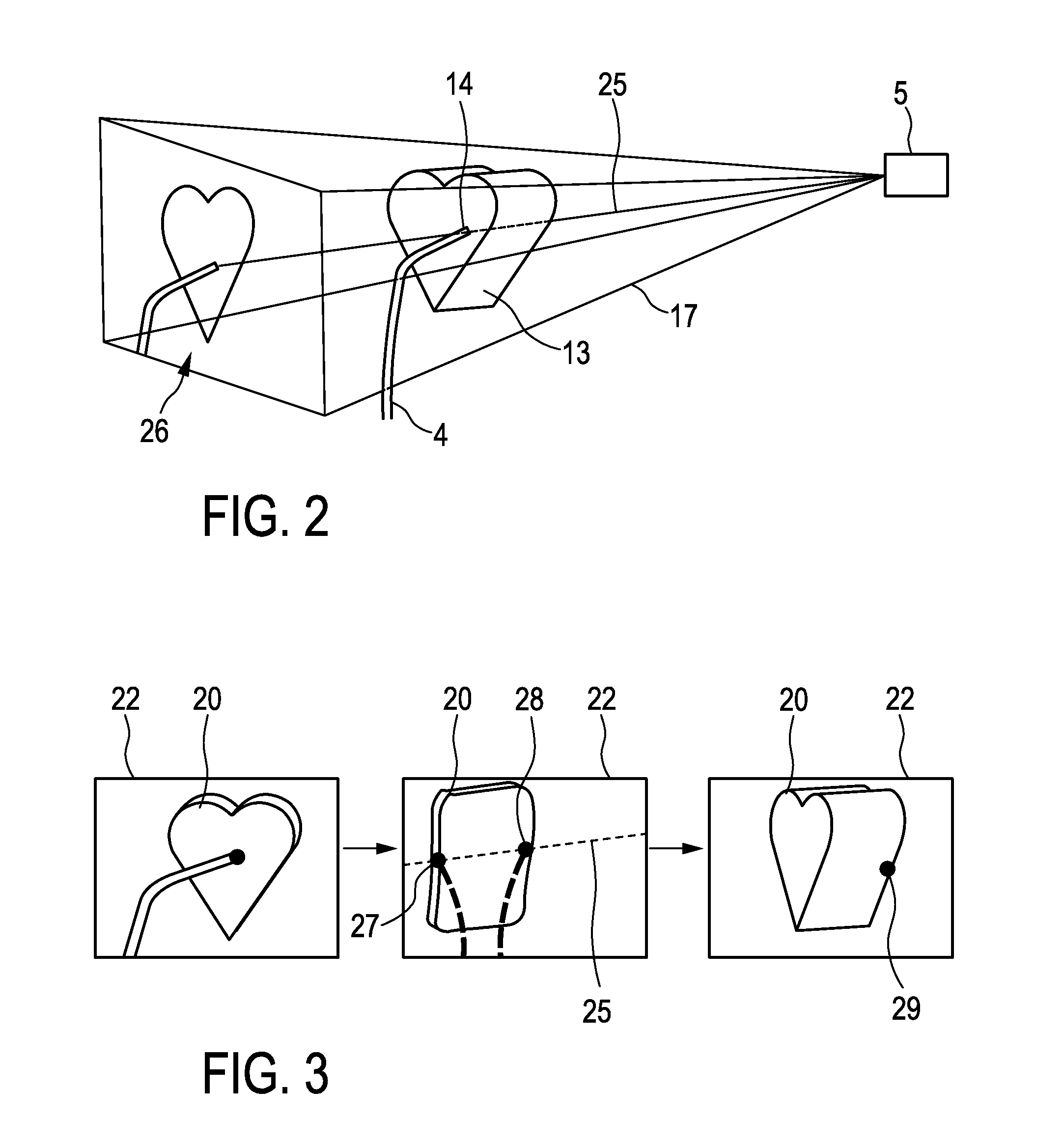

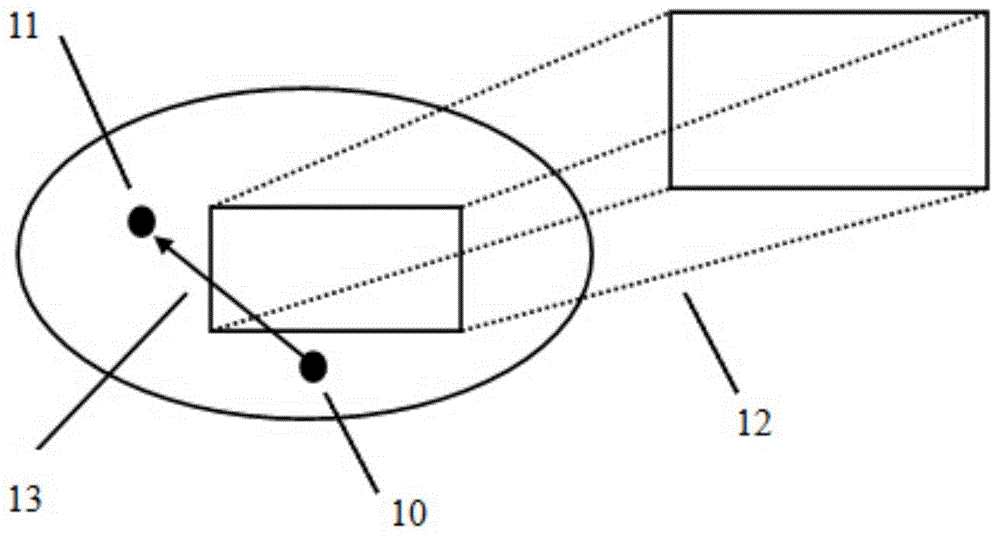

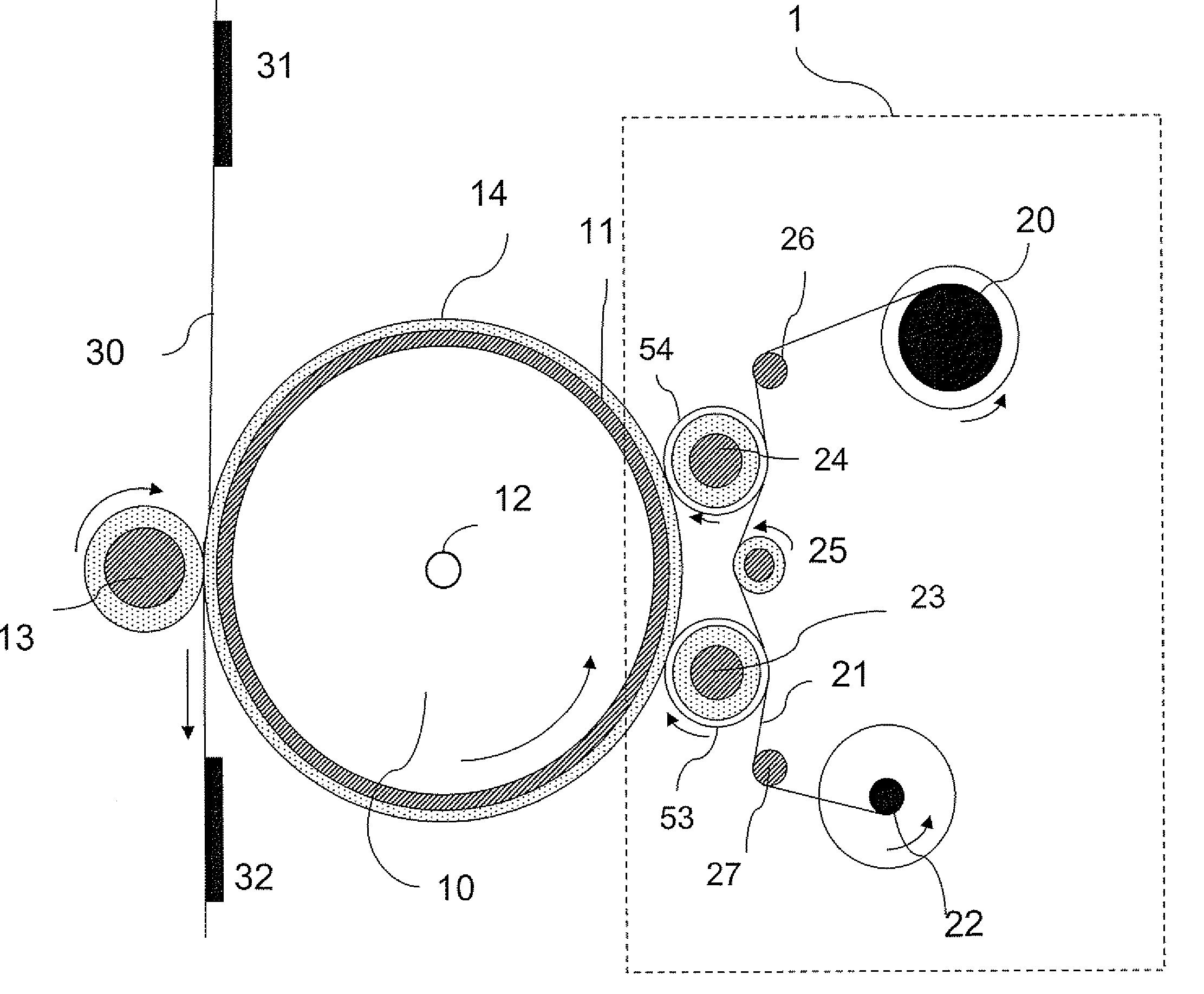

Apparatus for determining a position of a first object within a second object

ActiveUS20100020161A1Accurately determineReduce the amount of hardwareImage enhancementImage analysisProjection imageContact region

The present invention relates to an apparatus for determining a position of a first object (14) within a second object (13), wherein the first object (14) contacts the second object (13) at a contact region. The apparatus (1) comprises a provision unit (2) for providing a three-dimensional model (20) of the second object (13). A projection unit (5, 6, 7, 21) generates a two-dimensional projection image (26) of the first object (14) and of the second object (13), and a registration unit (8) registers the three-dimensional model (20) with the two-dimensional projection image (26). A determination unit (9) determines the position of the contact region from the position of the first object (14) on the two-dimensional projection image (26) and the registered three-dimensional model (20) of the second object (13), wherein the position of the contact region is the position of the first object (14) within the second object (13).

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

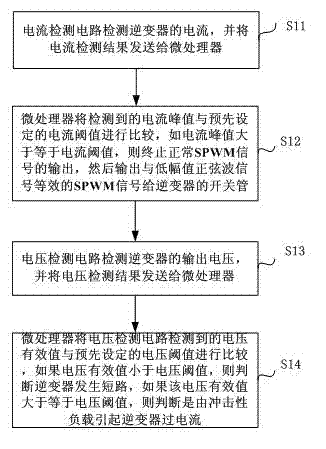

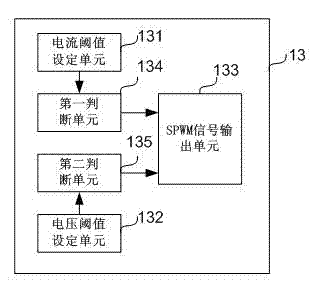

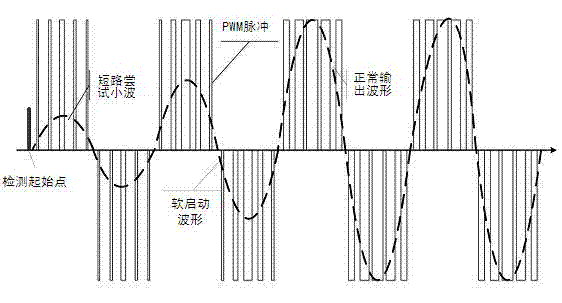

Method and device for determining over-current of inverter

ActiveCN103207339AReduce the amount of hardwareLow implementation costCurrent/voltage measurementElectrical testingPower inverterCurrent threshold

The invention discloses a method for determining the over-current of an inverter. The method comprises the steps that a current detection circuit detects the current of the inverter and sends a current detection result to a microprocessor; the microprocessor compares a detected current peak with a preset current threshold, stops normal outputting of sinusoidal pulse width modulation (SPWM) signals if the current peak is larger than or equal to the current threshold and outputs the SPWM signals equivalent to low-amplitude sinusoidal wave signals to the inverter; a voltage detection circuit detects the output voltage of the inverter and sends a voltage detection result to the microprocessor; and the microprocessor compares a detected voltage effective value with a preset voltage threshold and determines that the inverter is short-circuited if the voltage effective value is smaller than the voltage threshold, and the over-current occurs to the inverter due to impact loads. The invention further discloses a device for implementing the method. By means of the method and the device, whether the over-current of the inverter is caused by impact loads or short-circuit can be distinguished accurately.

Owner:KEBODA TECH CO LTD +1

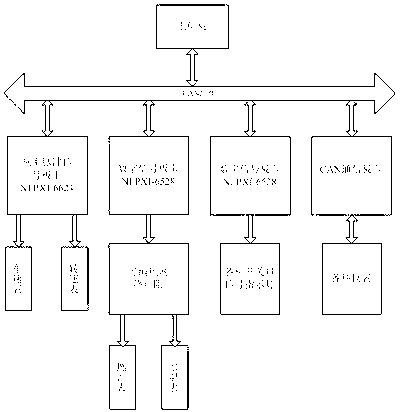

Check system for LabVIEW-based automobile instrument

InactiveCN103234572AQuick buildReduce the amount of hardwareTesting/calibration apparatusThermometer testing/calibrationArea networkPCI eXtensions for Instrumentation

The invention discloses a check system for a LabVIEW-based automobile instrument. The check system for the LabVIEW-based automobile instrument comprises an upper computer, a national instruments corporation PCI extensions for instrumentation-6624 (NIPXI-6624) board card, two NIPXI-6528 board cards, a programmable network resistor, a controller area network (CAN) communication board card, an NIPXI case, a serial port to universal serial bus (USB) data line and a LabVIEW human-computer interface software program. The upper computer communicates with the NIPXI case by the serial port to USB data line; the NIPXI board cards are inserted into corresponding slots in the NIPXI case; the NIPXI-6624 board card is respectively connected with a speedometer and a tachometer; one of the two NIPXI-6528 board cards is connected with a fuel meter and a water-thermometer by the programmable network resistor; the other NIPXI-6528 board card is connected with various switching value signal indicating lamps; the upper computer, the NIPXI board cards and various instruments communicate with the switching value signal indicating lamps by a CAN bus of the CAN communication board card; and the LabVIEW human-computer interface software program is a software platform of the check system. The portable automobile instrument check system is compact and flexible and is high in reliability, and the real-time feedback of automobile state information can be realized by aiming at different automobiles.

Owner:ANHUI UNIVERSITY OF TECHNOLOGY AND SCIENCE

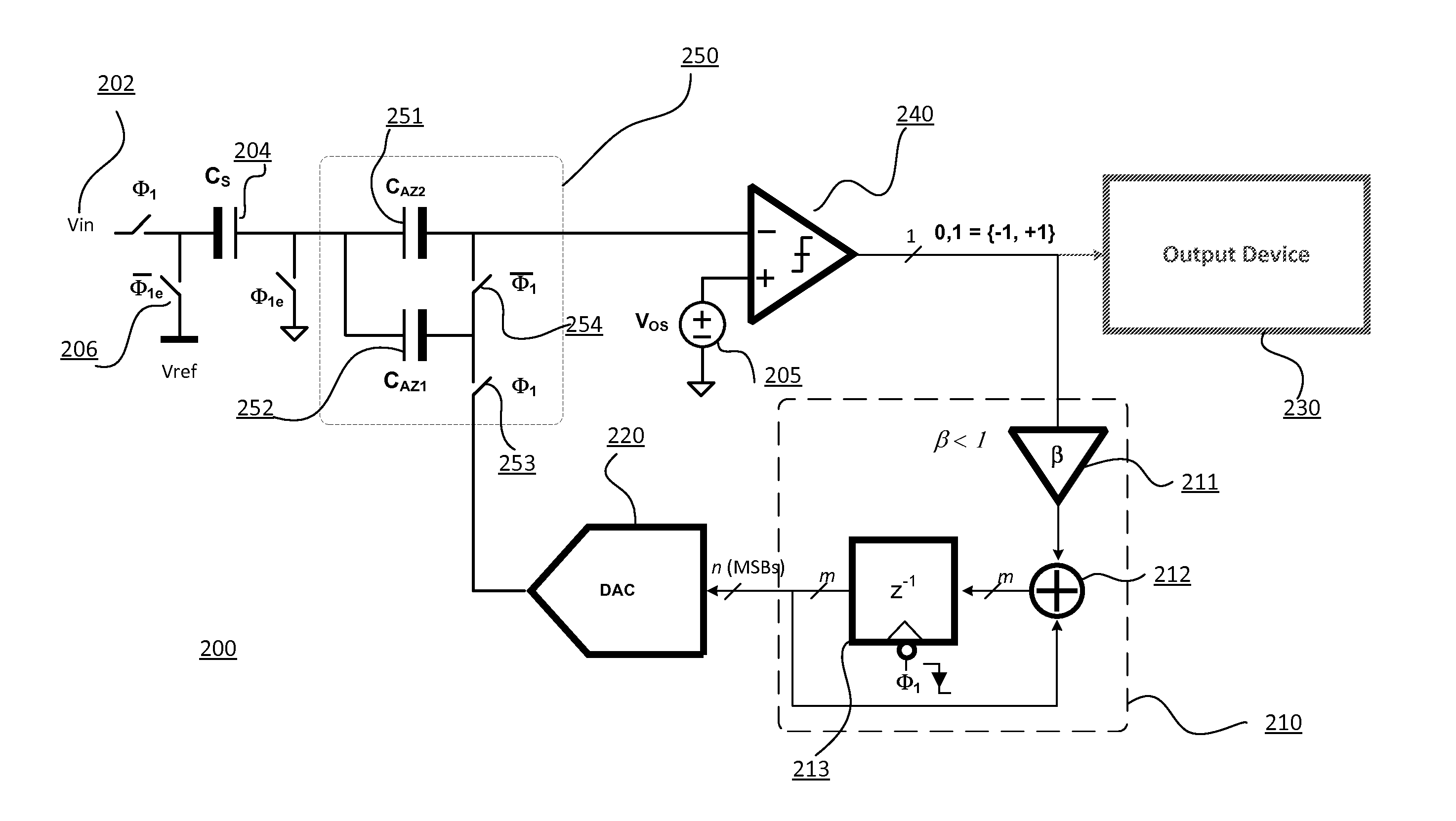

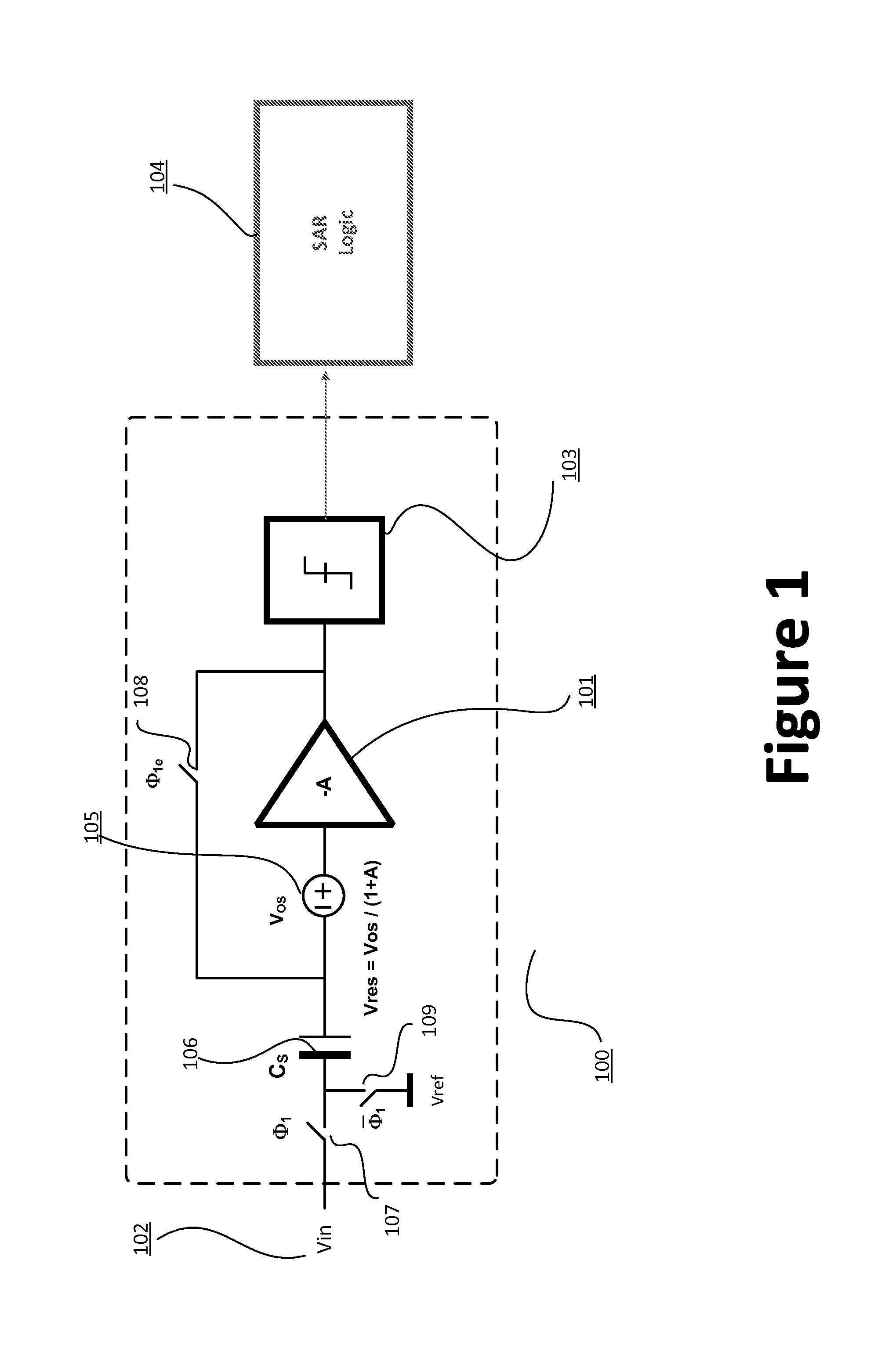

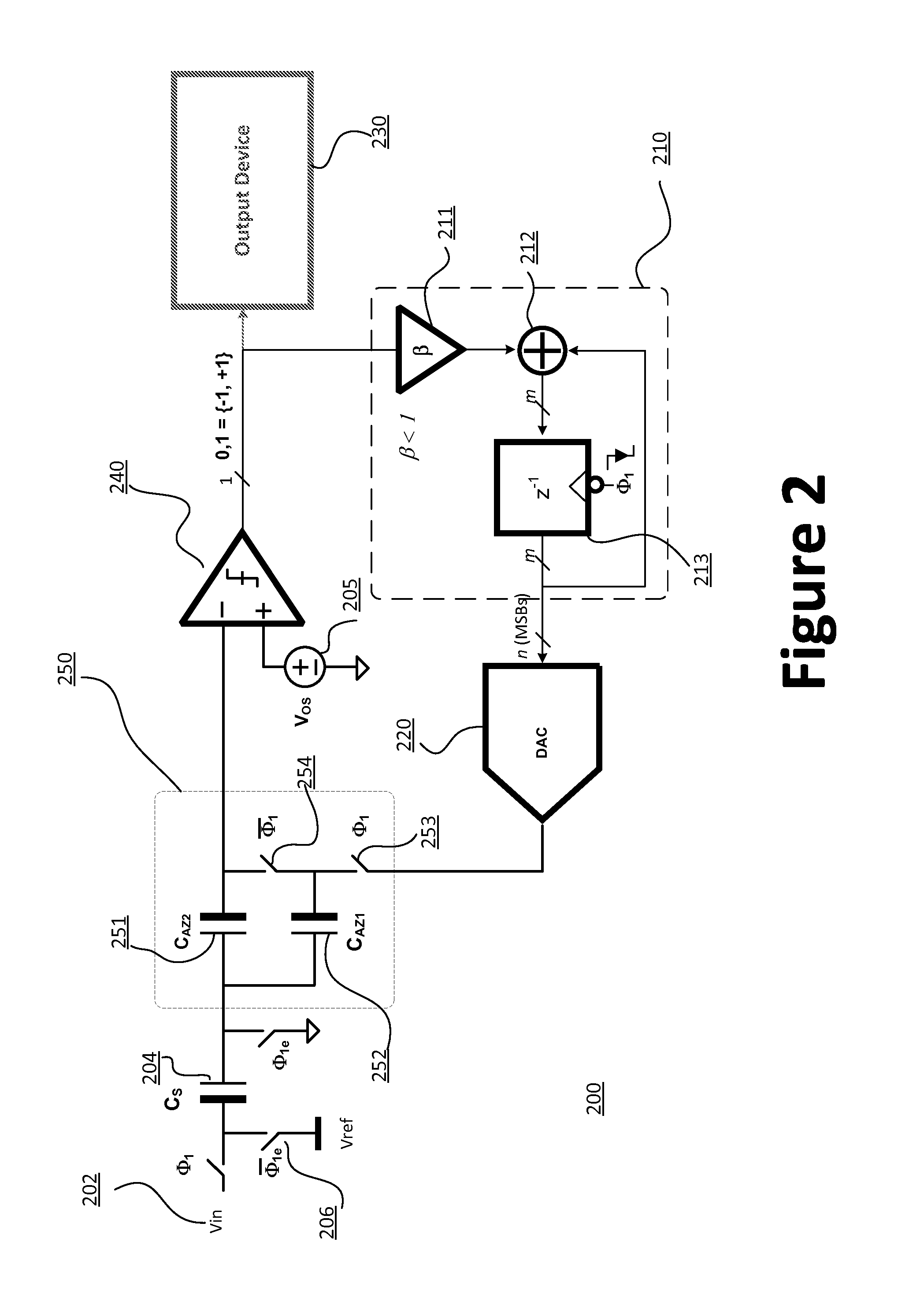

Systems and methods for comparator calibration

ActiveUS9356615B1Reduce interferenceReducing of slow downElectric signal transmission systemsDigital-analogue convertorsIntegratorLow-pass filter

The present invention is directed integrated circuits and methods thereof. More specifically, an embodiment of the present invention provides a comparator calibration loop where a digital integrator stores a running sum based on the output of a comparator. A DAC converts the running sum and generates an offset calibration voltage, which is filtered by a low-pass filter module, and the filtered offset calibration voltage is used to cancel out the intrinsic offset voltage and low frequency noise of the comparator. There are other embodiments as well.

Owner:MARVELL ASIA PTE LTD

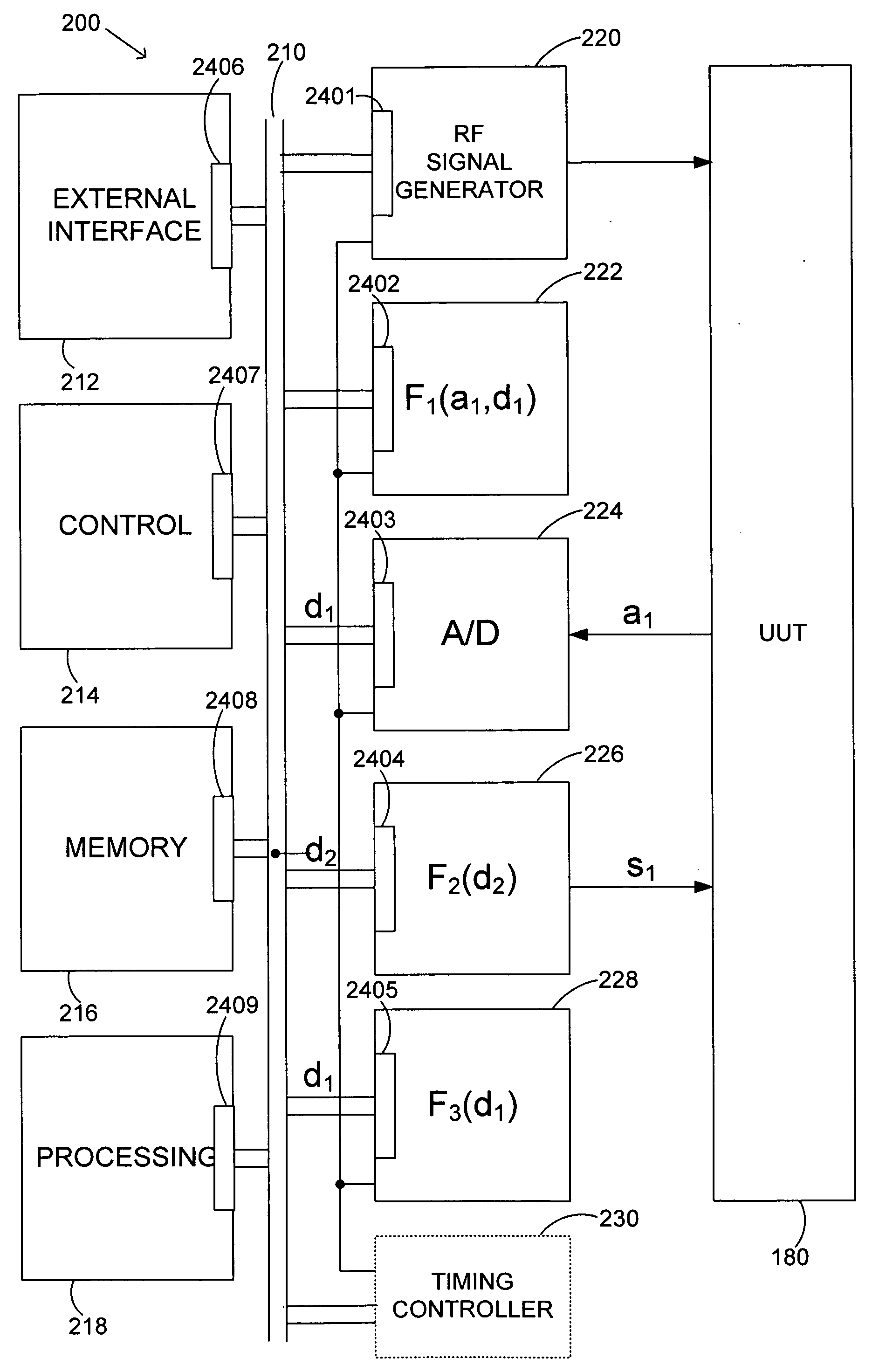

Networked test system

ActiveUS7908531B2Reduce the amount of hardwareReducing the total hardware requiredDigital circuit testingDetecting faulty hardware by remote testComputer moduleTest requirements

An automatic test system that can be configured to perform any of a number of test processes. The test system contains multiple functional modules that are interconnected by a network. By using software to configure data flow between functional modules, combinations of modules can be made, thereby creating virtual instruments. As test requirements change, the test system can be reconfigured to contain other virtual instruments, eliminating or reducing the need to add instruments to meet changing test requirements. To ensure adequate performance of the test system, a proposed configuration may be simulated, and if a virtual instrument does not provide a required level of performance, the test system may be reconfigured.

Owner:TERADYNE

Timestamp Neural Network

ActiveUS20100257130A1Reduce the number of connectionsReduce the amount of hardwareDigital computer detailsDigital dataTimestampMachine learning

A timestamp neural network comprised of sensor elements, internal elements, and motor elements is responsive to timestamps. Sensor elements transform a wide variety of signals into events that trigger the updating of timestamps. Internal elements are responsive to timestamps. Motor elements convert timestamps into useful output signals. A real time video pattern recognition system is implemented.

Owner:SMALLRIDGE BRAD

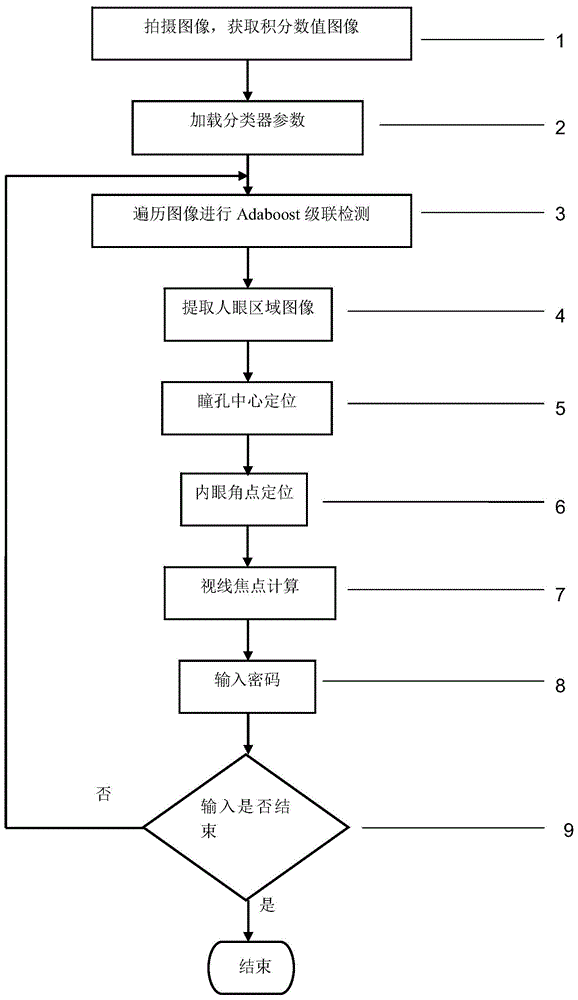

Eye sight-based password inputting method and hardware device thereof

ActiveCN104156643AReduce the amount of hardwareSimple structureCharacter and pattern recognitionDigital data authenticationAdaBoostDisplay device

The invention relates to an eye sight-based password inputting method and a hardware device thereof. The hardware device comprises a shooting unit, a display unit and a processing unit. The eye sight-based password inputting method includes the steps of subjecting the shooting unit to shooting a facial image to form an integral numerical image, determining a target area containing eyes of the user by using Adaboosts to perform a traversal to the integral numerical image and a cascade detection, determining positions of pupil centers of the left and the right eyes and inner eye corner points in the target area, and determining specific positions of sight focuses on the display unit according to geometrical relationship to achieve password inputting. Compared with the prior art, the eye sight-based password inputting method is safer, more rapid and convenient, higher in inputting accuracy, simplified in the required hardware device and lower in cost.

Owner:SUN YAT SEN UNIV

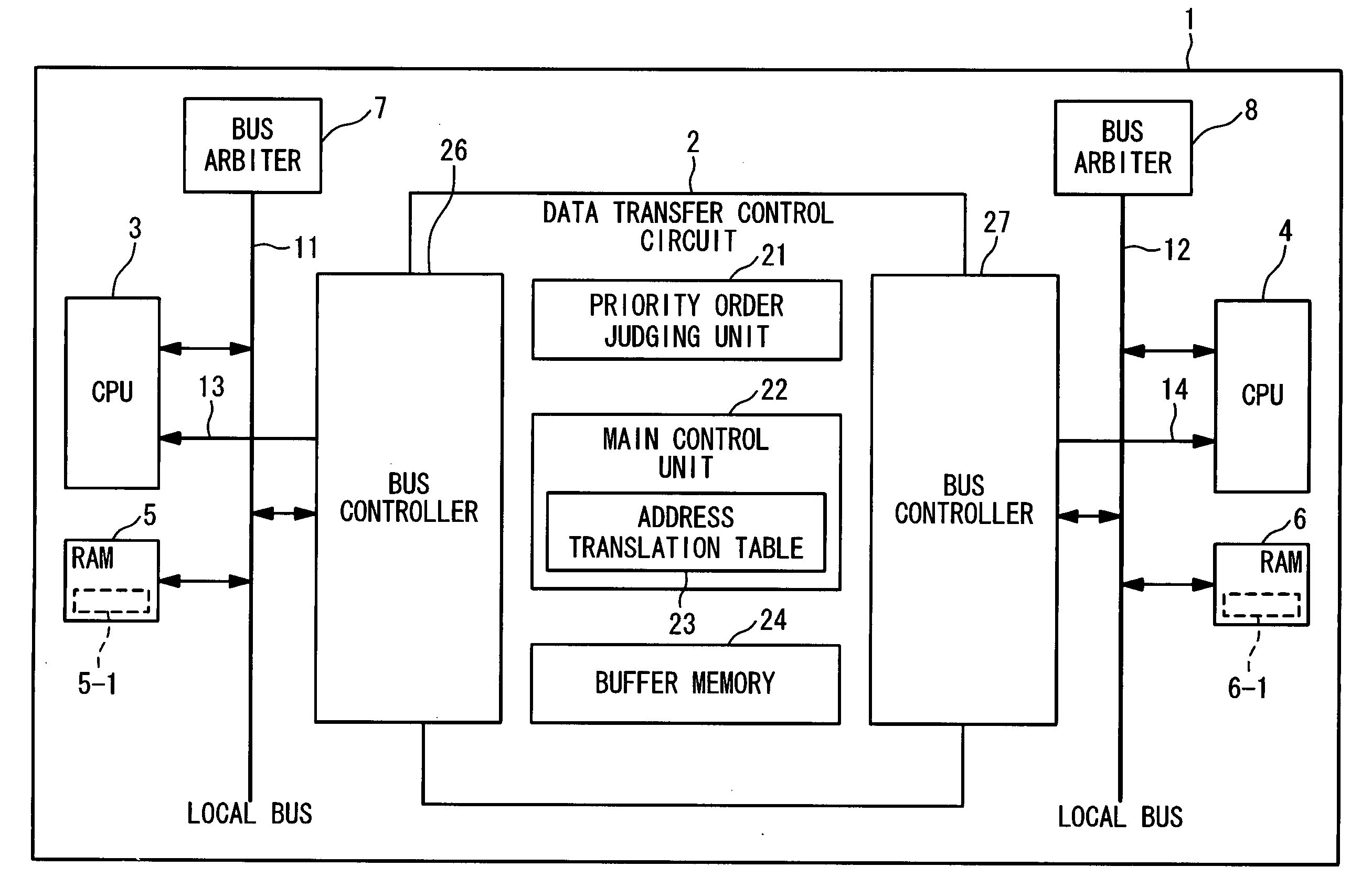

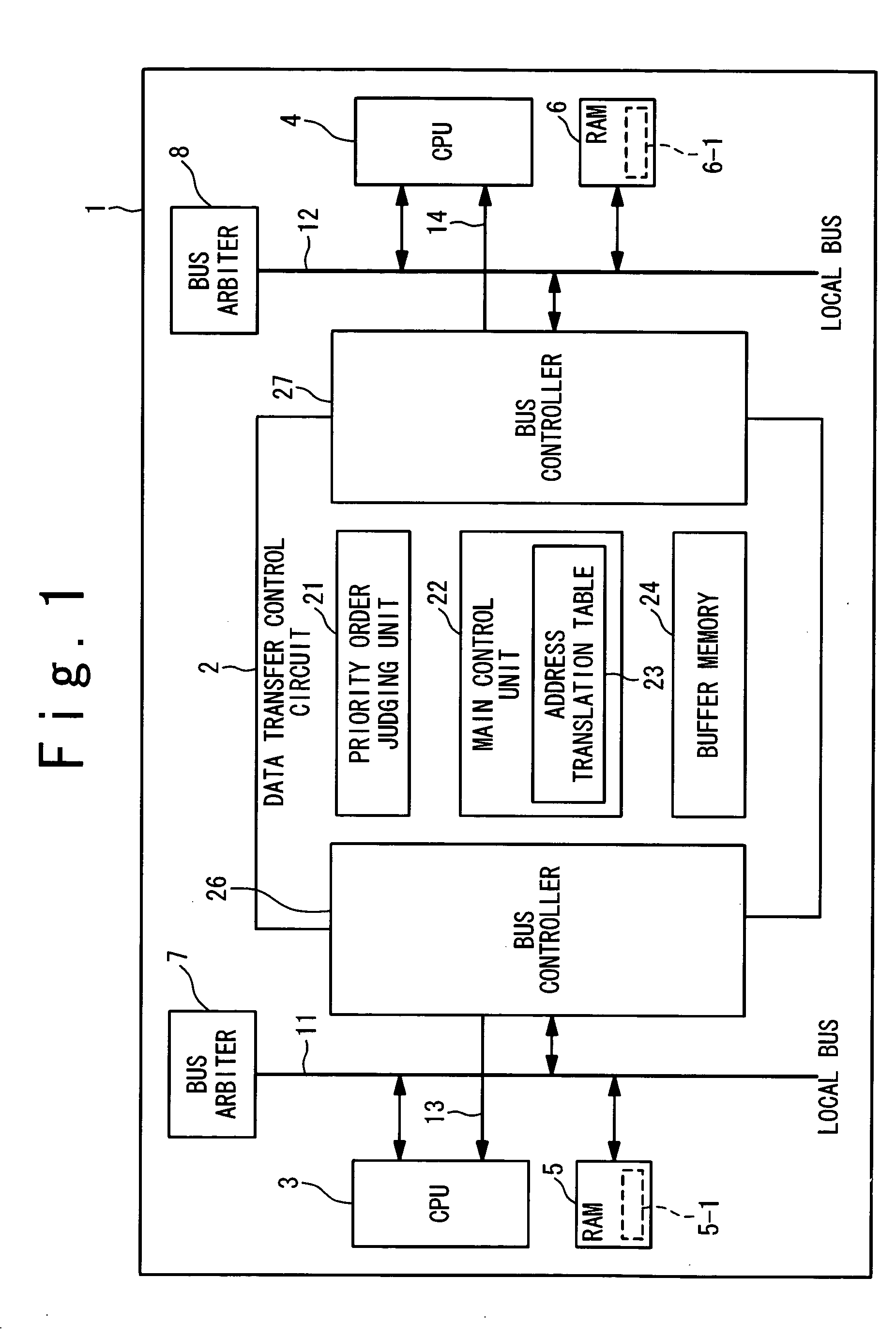

Data transfer control circuit, control apparatus and data transfer method

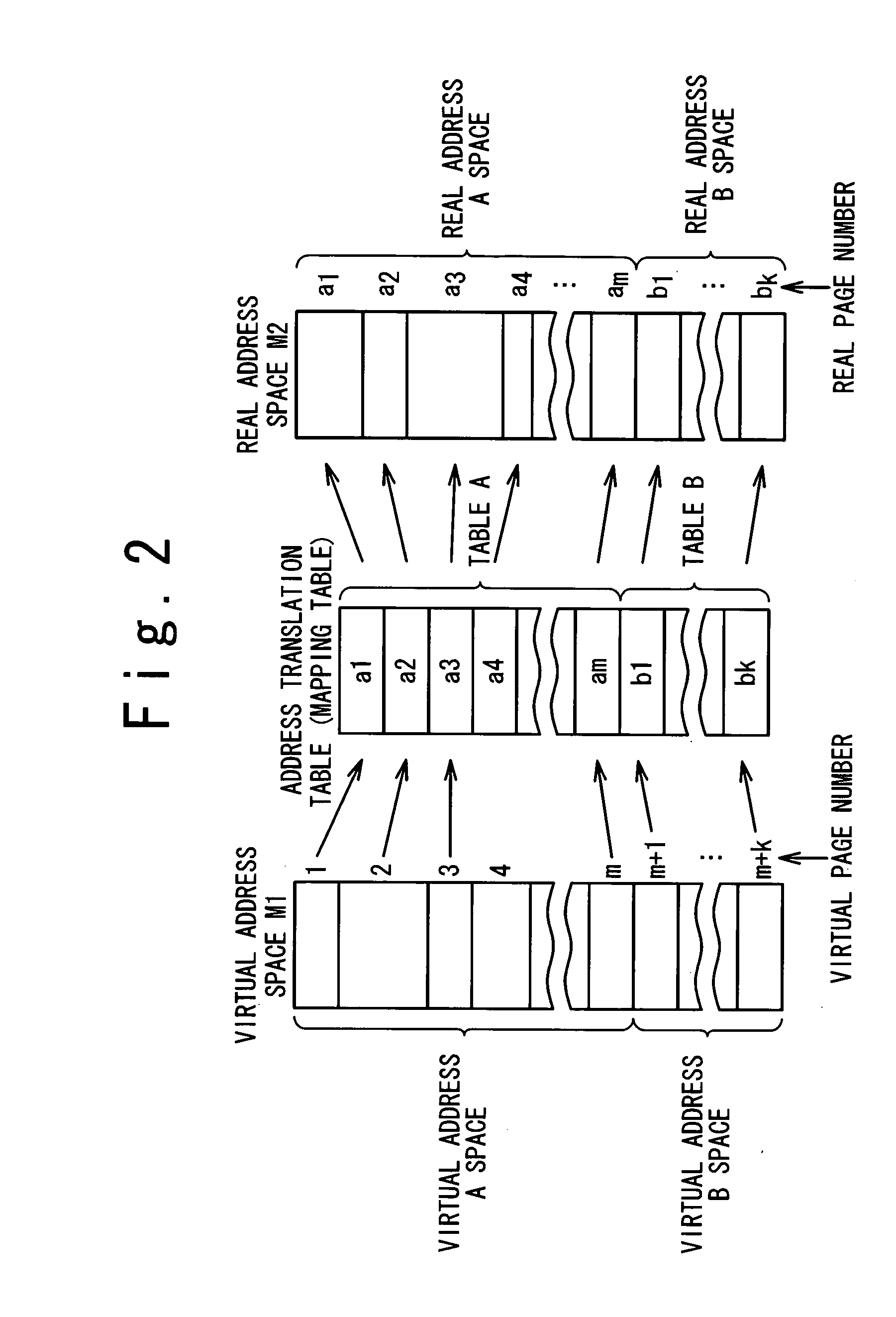

InactiveUS20050262327A1Easy accessReduce the amount of codeMemory adressing/allocation/relocationDigital computer detailsTranslation tableControl circuit

A data transfer control circuit is connected between a first bus and a second bus. The first bus is connected with a first CPU and a first memory. The second bus is connected with a second CPU and a second memory. The data transfer control circuit includes a temporary memory and a control unit. The temporary memory is configured to temporarily stores a first address and a first write data which are outputted by the first CPU through the first bus. The control unit is configured to translate the first address into a second address in the second memory with reference to an address translation table. The control unit occupies the second bus to write the first write data to the second address in the second memory through the second bus, when the first CPU releases the first bus after outputting the first address and the first write data to the data transfer control circuit through the first bus.

Owner:NEC ELECTRONICS CORP

Sound heterodyne apparatus and method

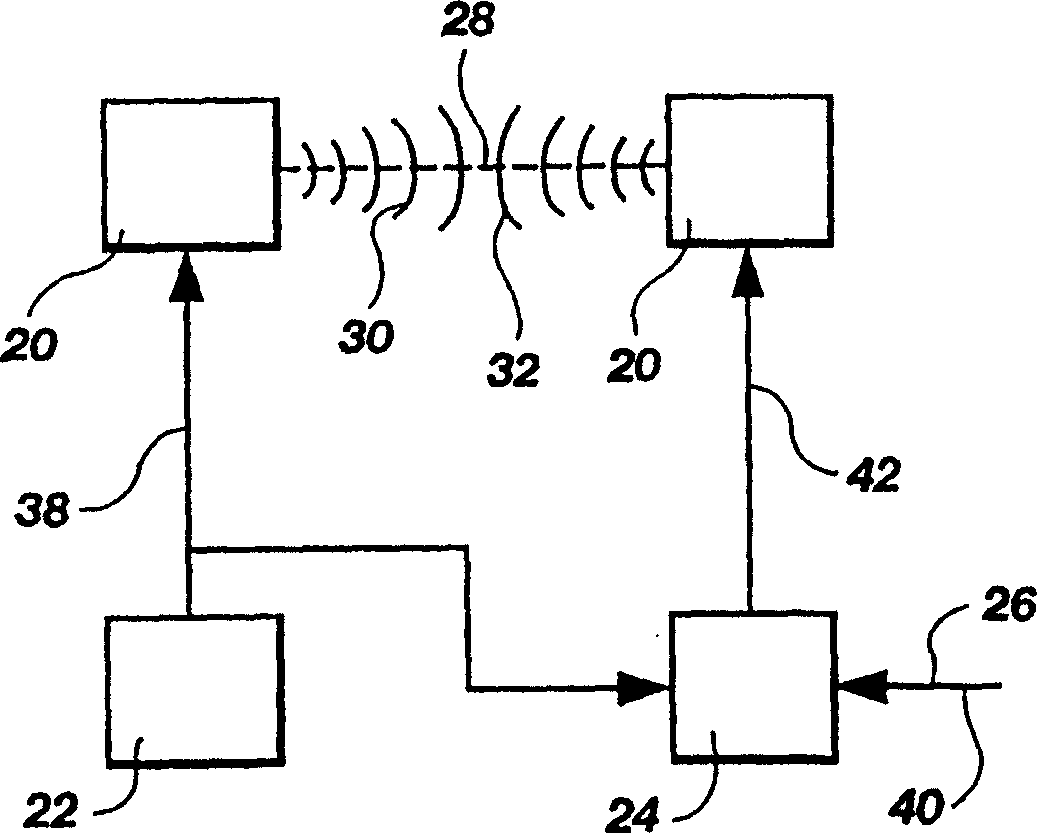

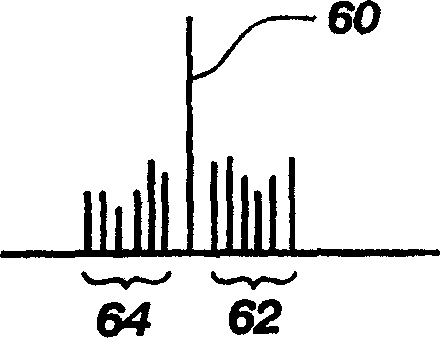

InactiveCN1638533AReduce the amount of hardwareSonic/ultrasonic/infrasonic transmissionPiezoelectric/electrostrictive transducersSonificationUltrasonic radiation

The invention relates to the emission of new acoustic or infrasonic compression waves from a resonant cavity (80) due to the coherence of at least two ultrasonic trains (30, 32). In one embodiment, two ultrasound emitters (20) are directed towards the cavity. When the frequency difference between two ultrasonic wave trains is in the acoustic or infrasonic frequency range, a new sound or infrasonic wave train of this frequency is emitted from the interference cavity or region according to the principle of acoustic heterodyning. The preferred embodiment is a system consisting of a single ultrasound radiating element, which is oriented towards a cavity emitting multiple waves.

Owner:AMERICAN TECH

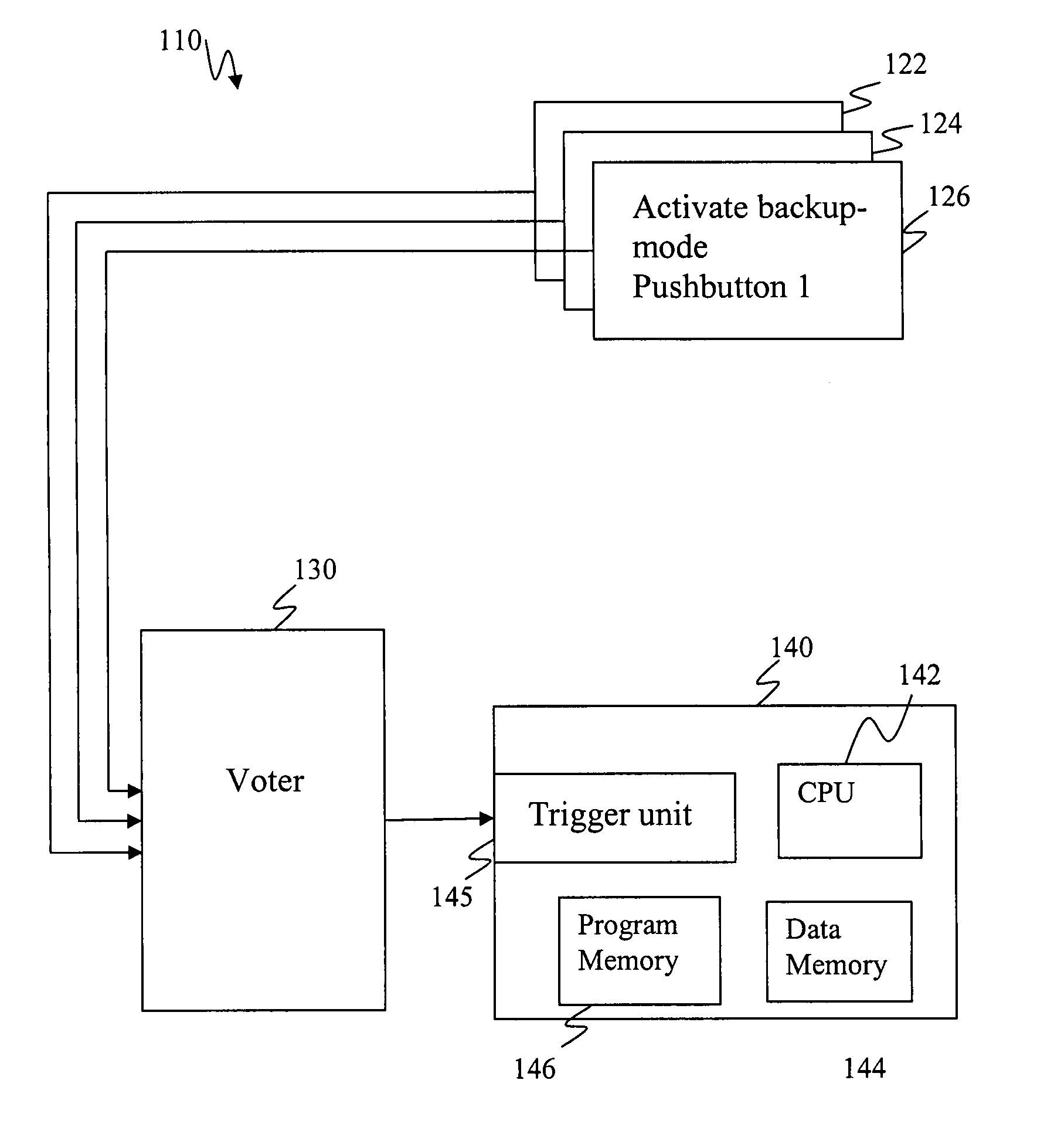

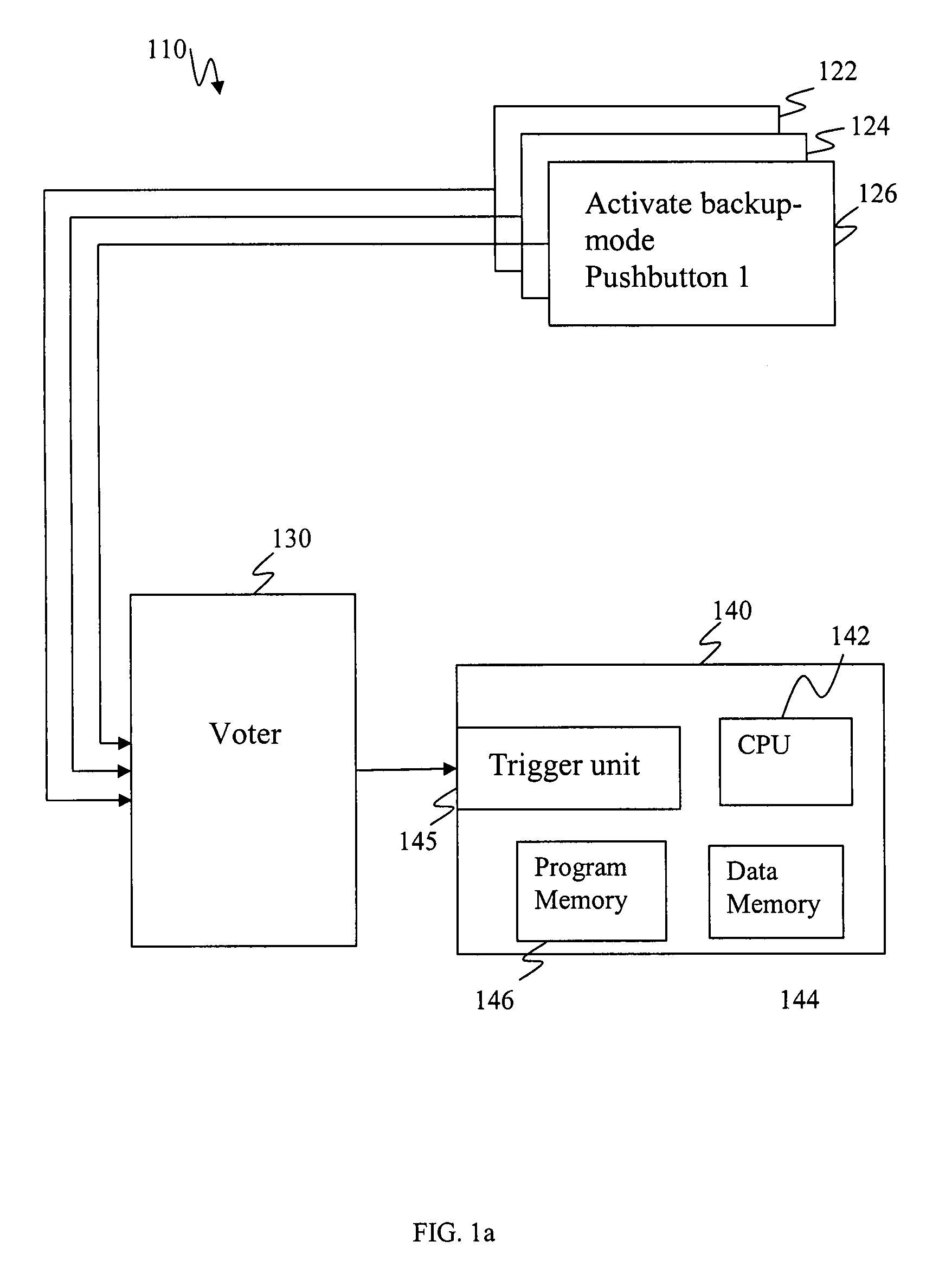

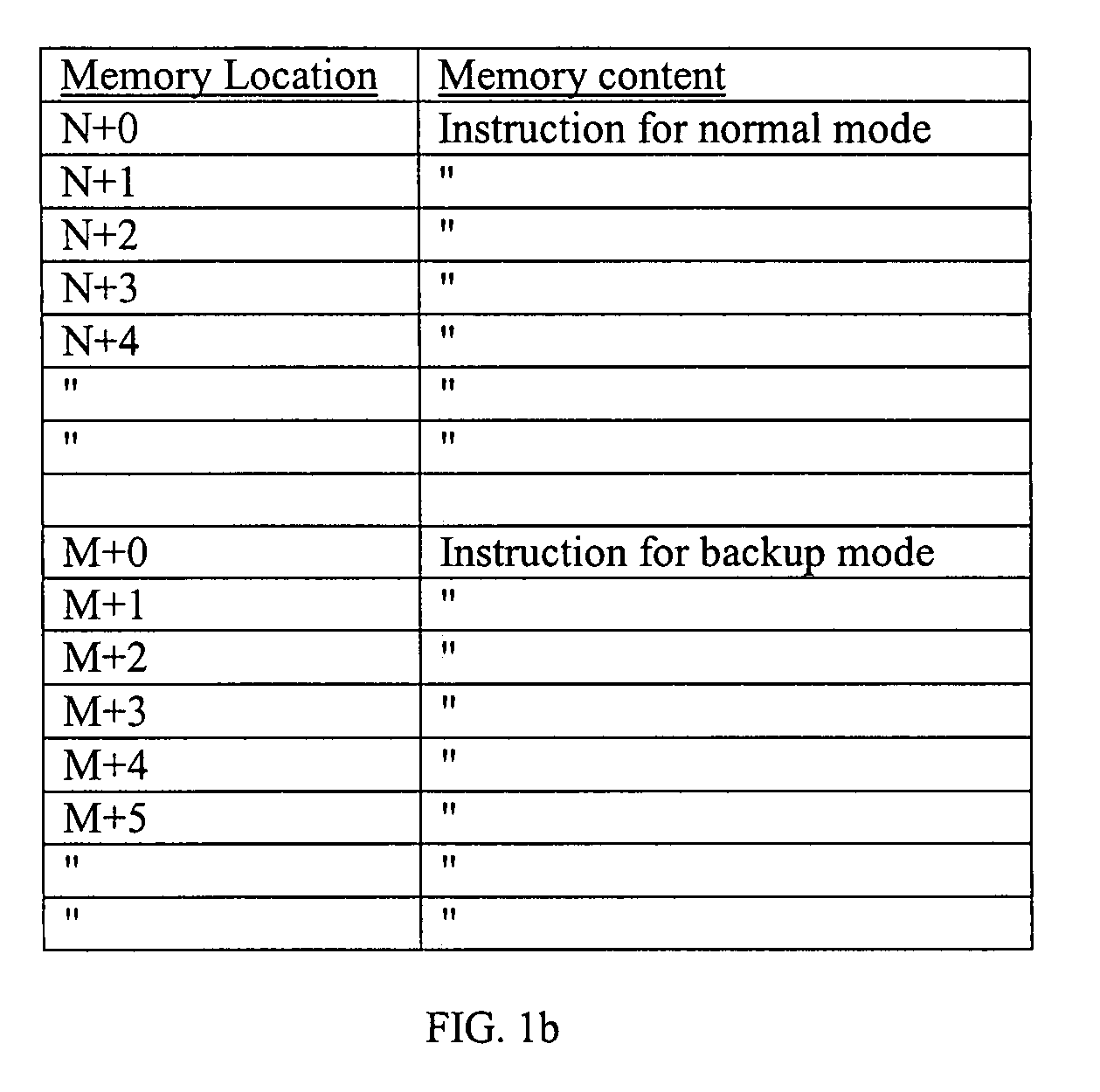

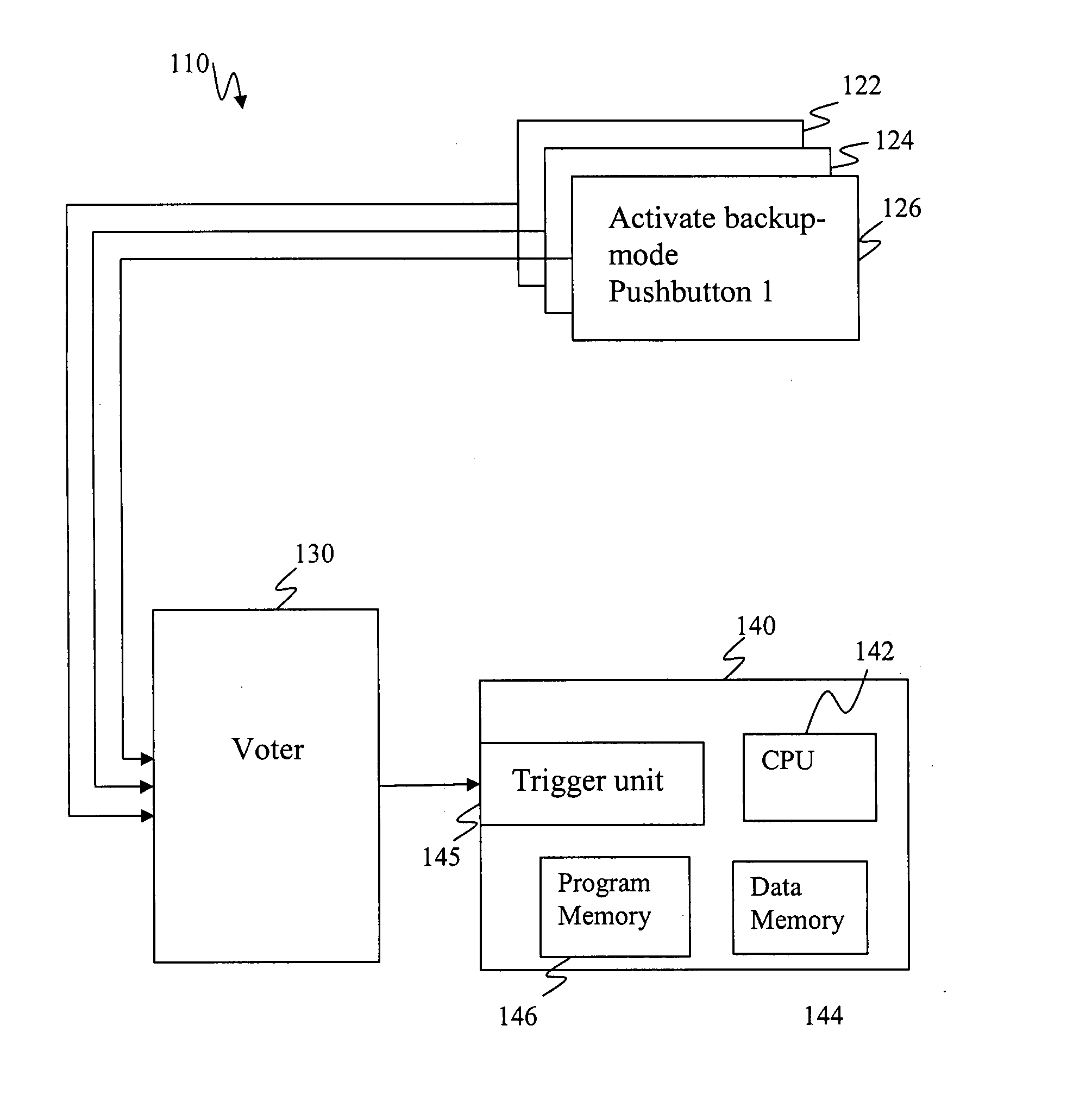

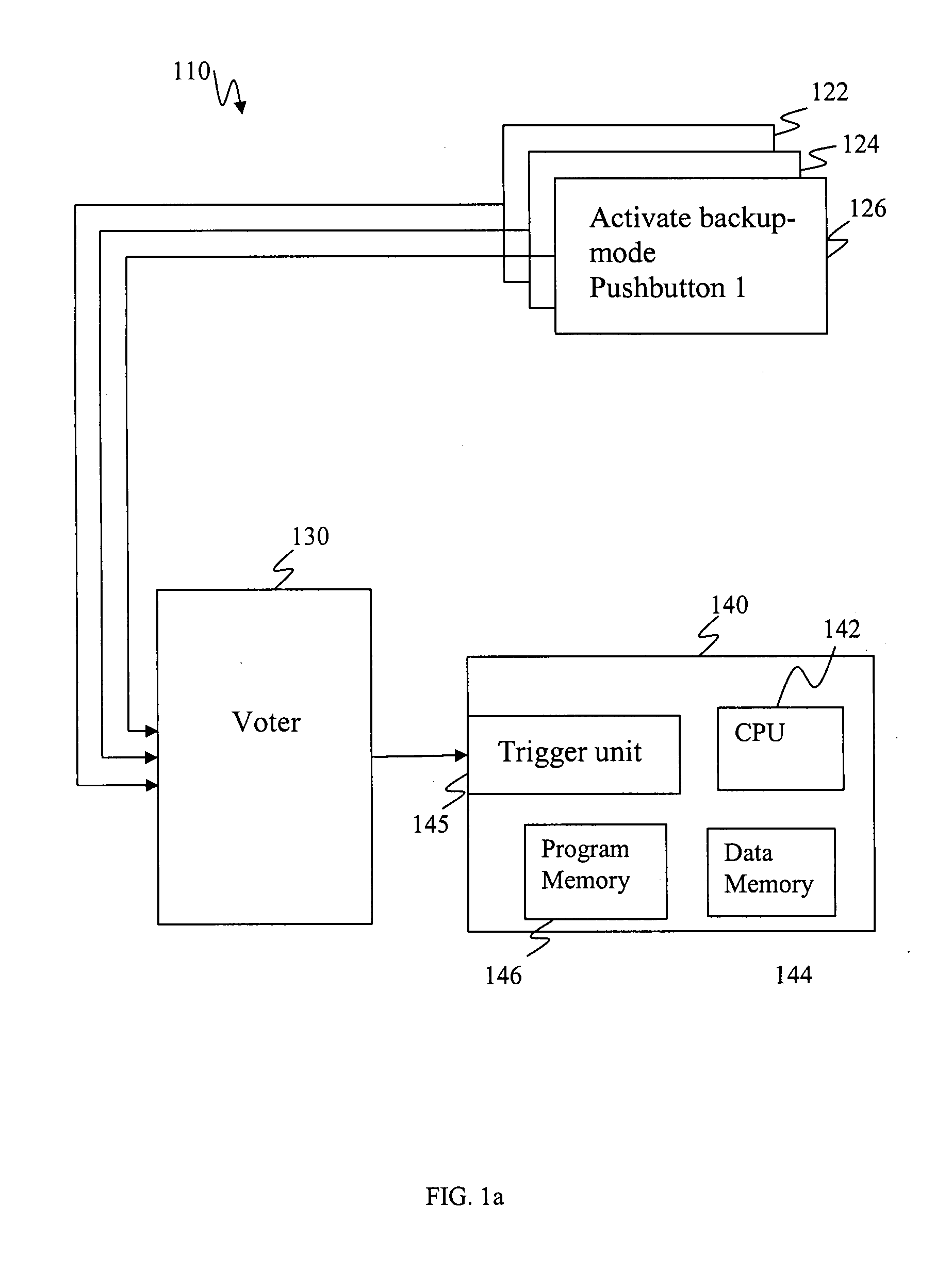

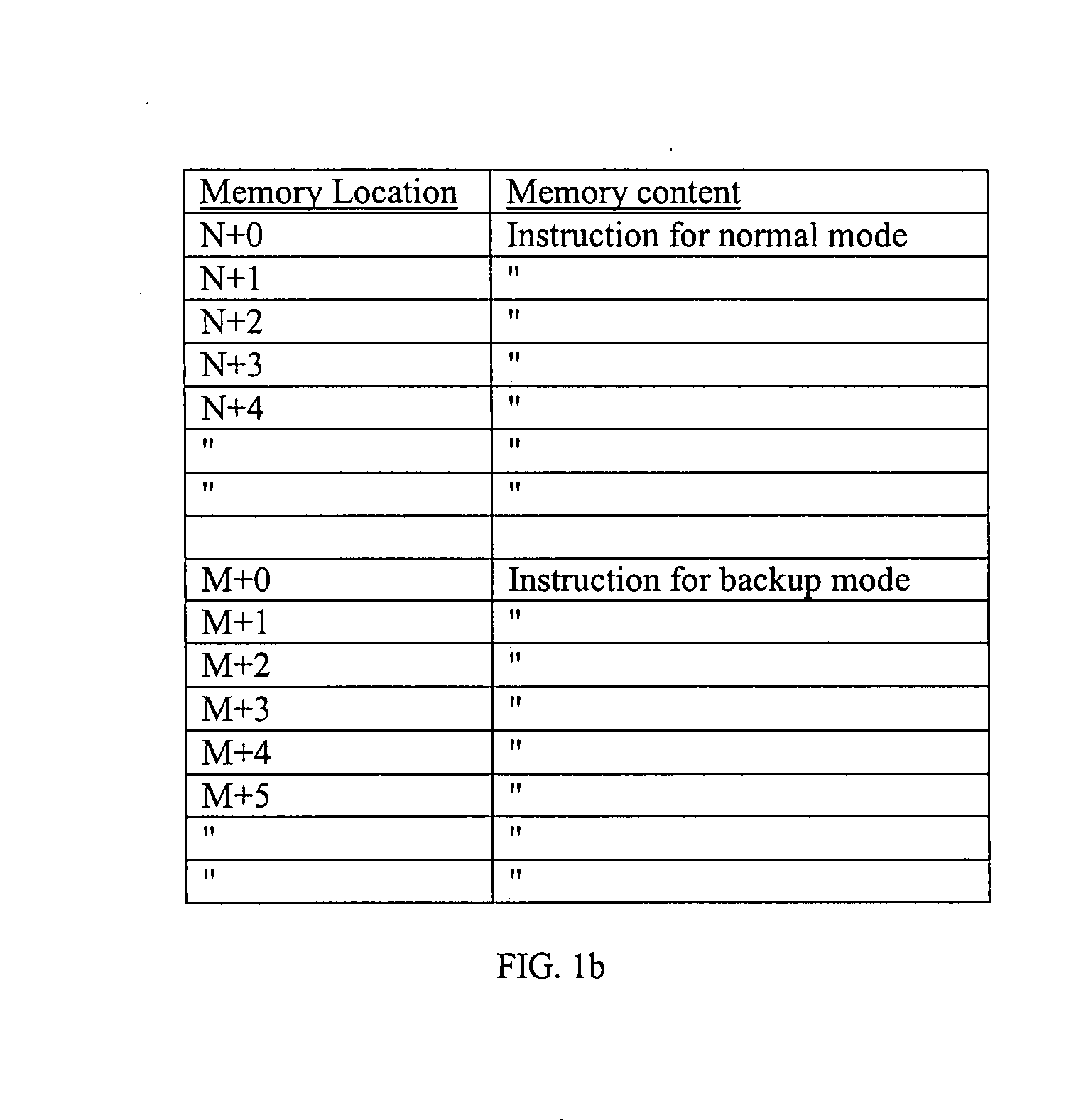

Fault tolerant control system

ActiveUS7840832B2Reduce the amount of hardwareReduce the amount requiredError detection/correctionData processing systemNormal mode

A fault tolerant data processing system for controlling a real time process. The system is tolerant to systematic faults in its software. The system includes a data processor unit with a program memory and a data memory and input and output units where program software residing in the program memory can be executed on the data processor unit. The system includes a normal-mode software program residing in the program memory, and a backup-mode software program also residing in the program memory arranged to perform the same or similar function of the normal mode software program but being differently implemented than the normal-mode software program, and where a trigger signal received by the data processor unit can switch execution control such that the normal-mode software program stops executing and the backup-mode software program starts executing.

Owner:SAAB AB

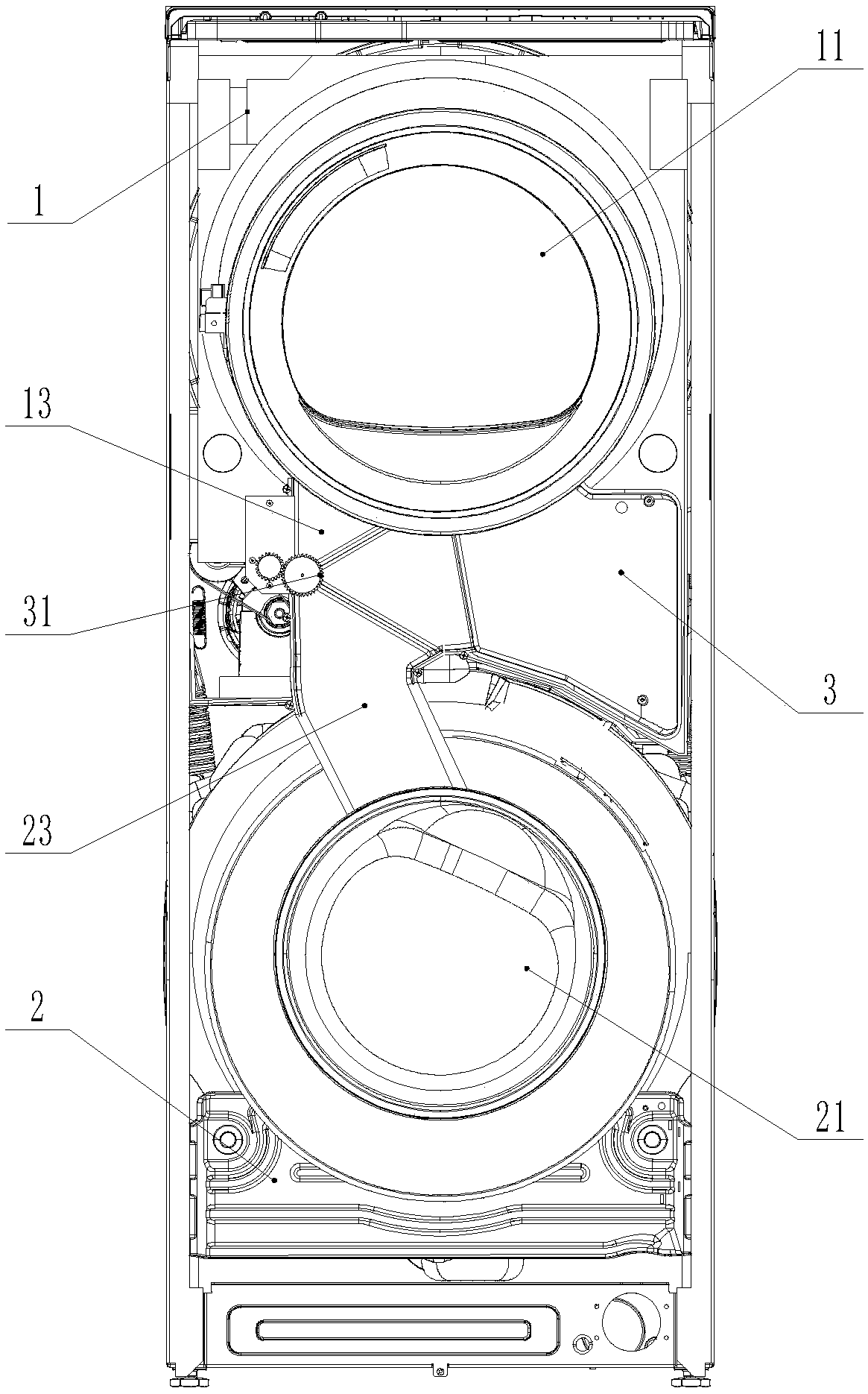

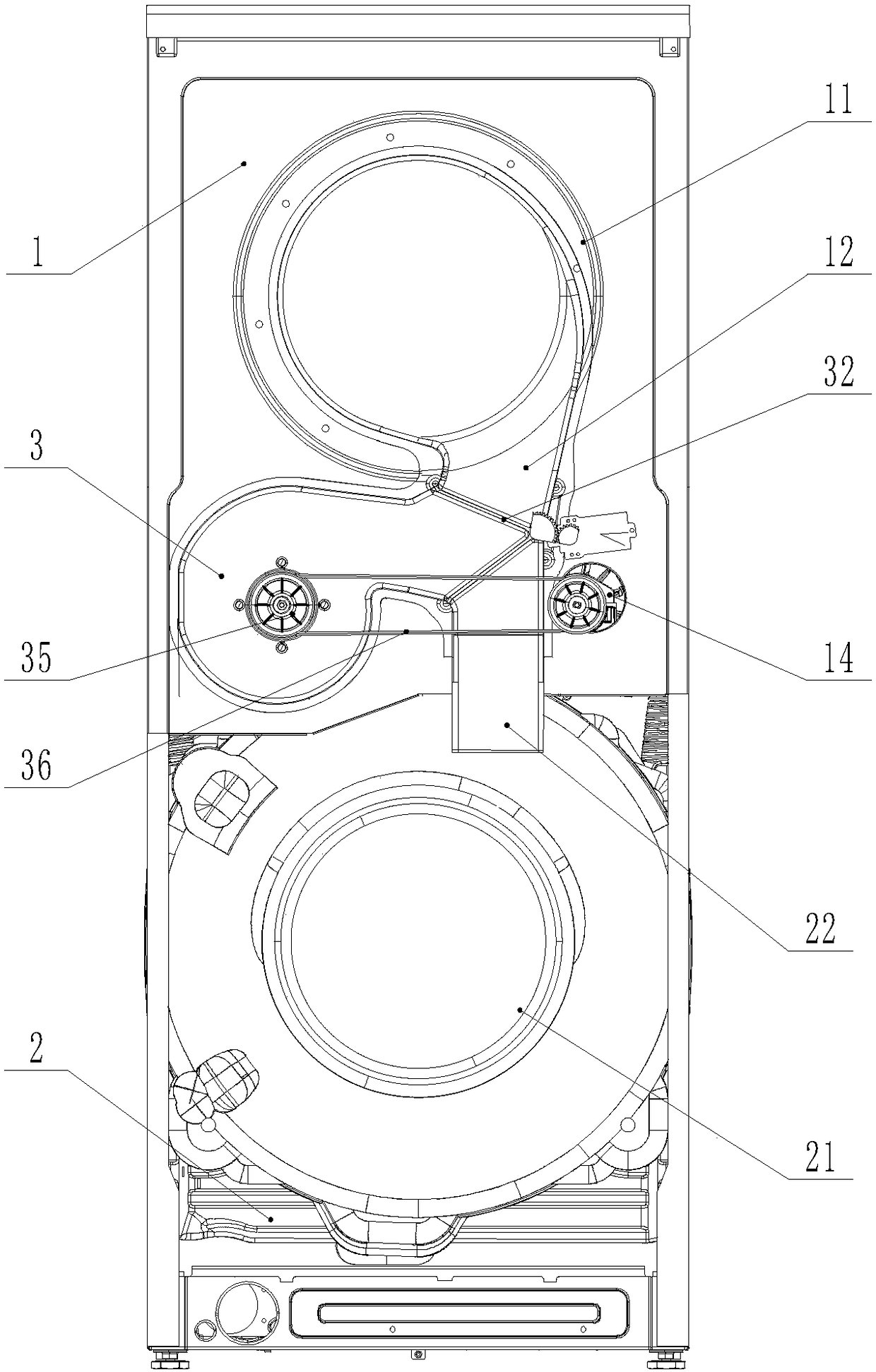

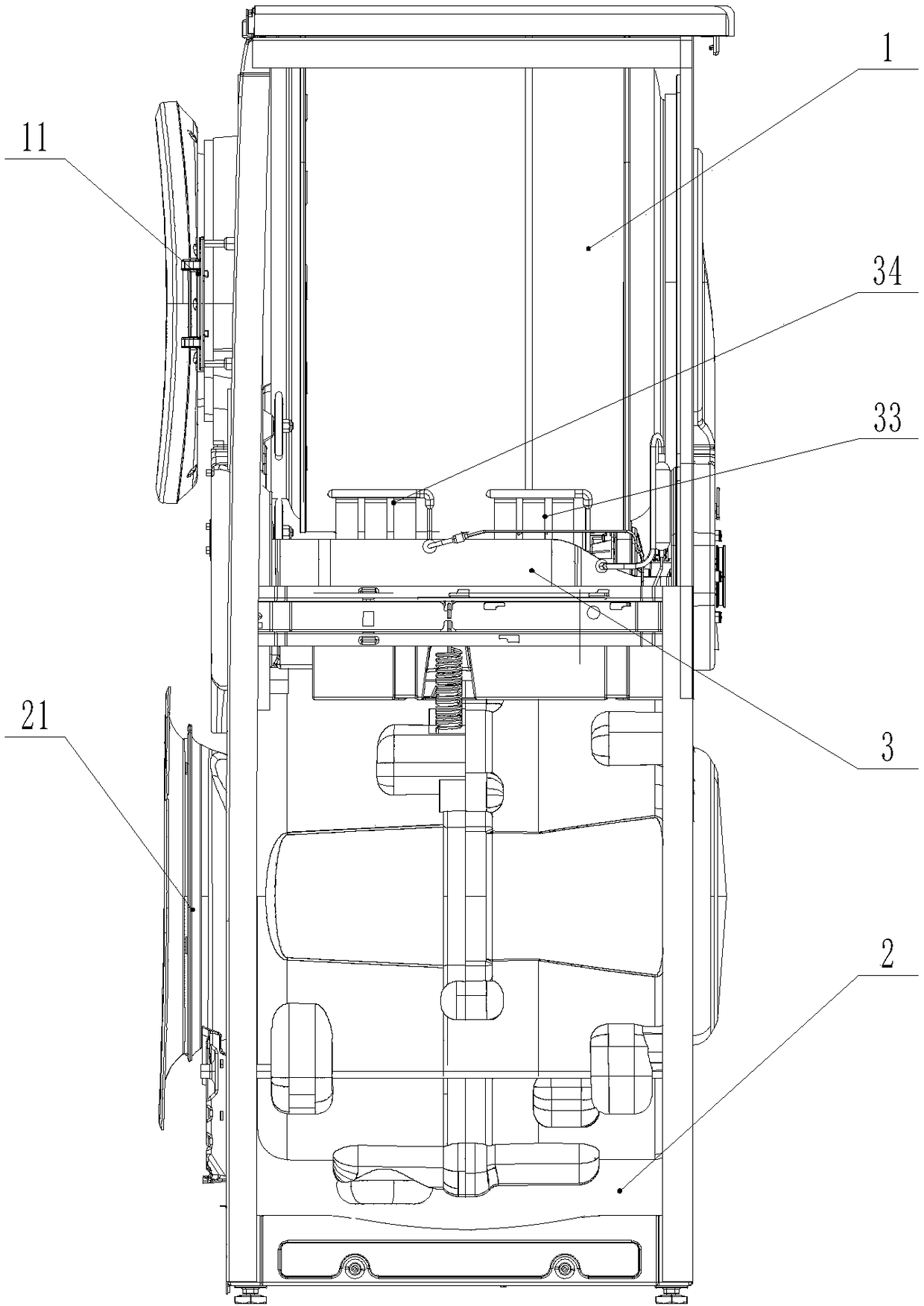

Clothes processing device

InactiveCN108950976AImprove user experienceReduce the amount of hardwareOther washing machinesWashing machine with receptaclesPulp and paper industryAirflow

The invention belongs to the field of household appliances, and particularly provides a clothes processing device. The clothes processing device is aimed at solving the problem that an existing clothes washing machine can not dry clothes through a drying system of the clothes dryer. For the purpose, the clothes processing device comprises a clothes dryer, a clothes washing machine and a drying system. The drying system comprises a reversing device. The drying system can produce drying air flow. By switching the state of the reversing device, the drying air flow can be alternatively conveyed into the clothes dryer or the clothes washing machine. Thus, the clothes processing device can dry the clothes in the clothes dryer and the clothes washing machine through the drying system, and the useexperience of the user is improved.

Owner:QINGDAO HAIER DRUM WASHING MACHINE

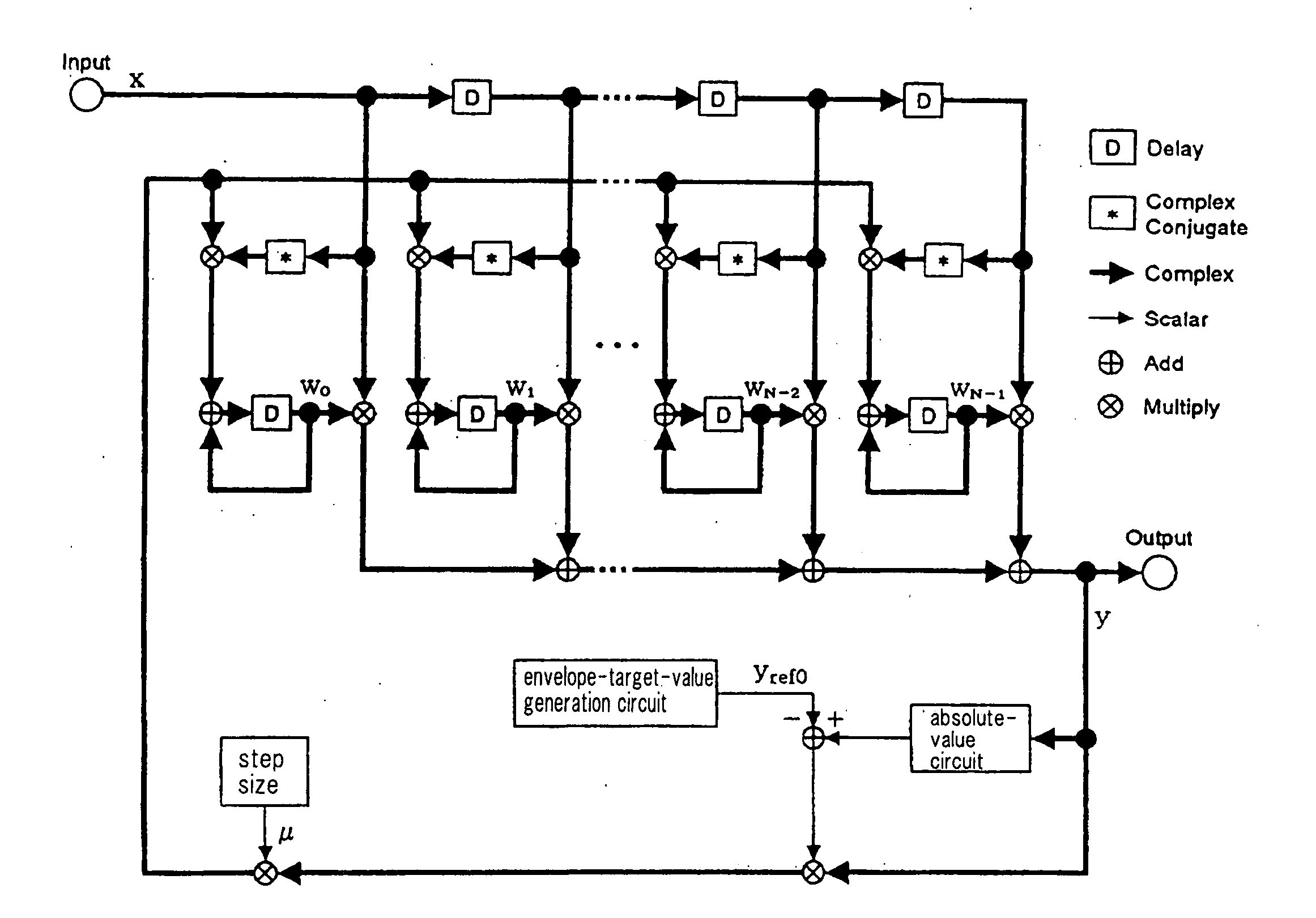

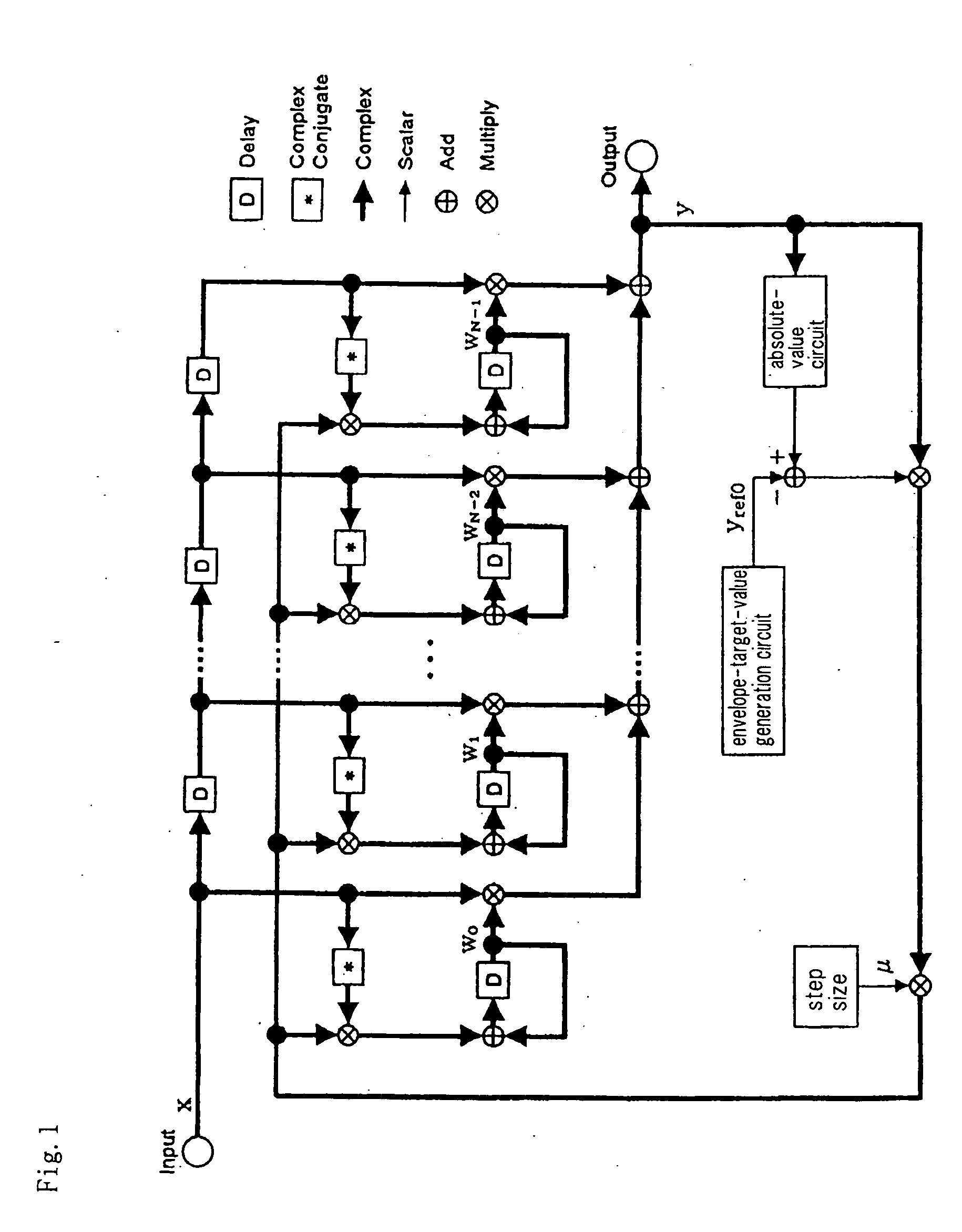

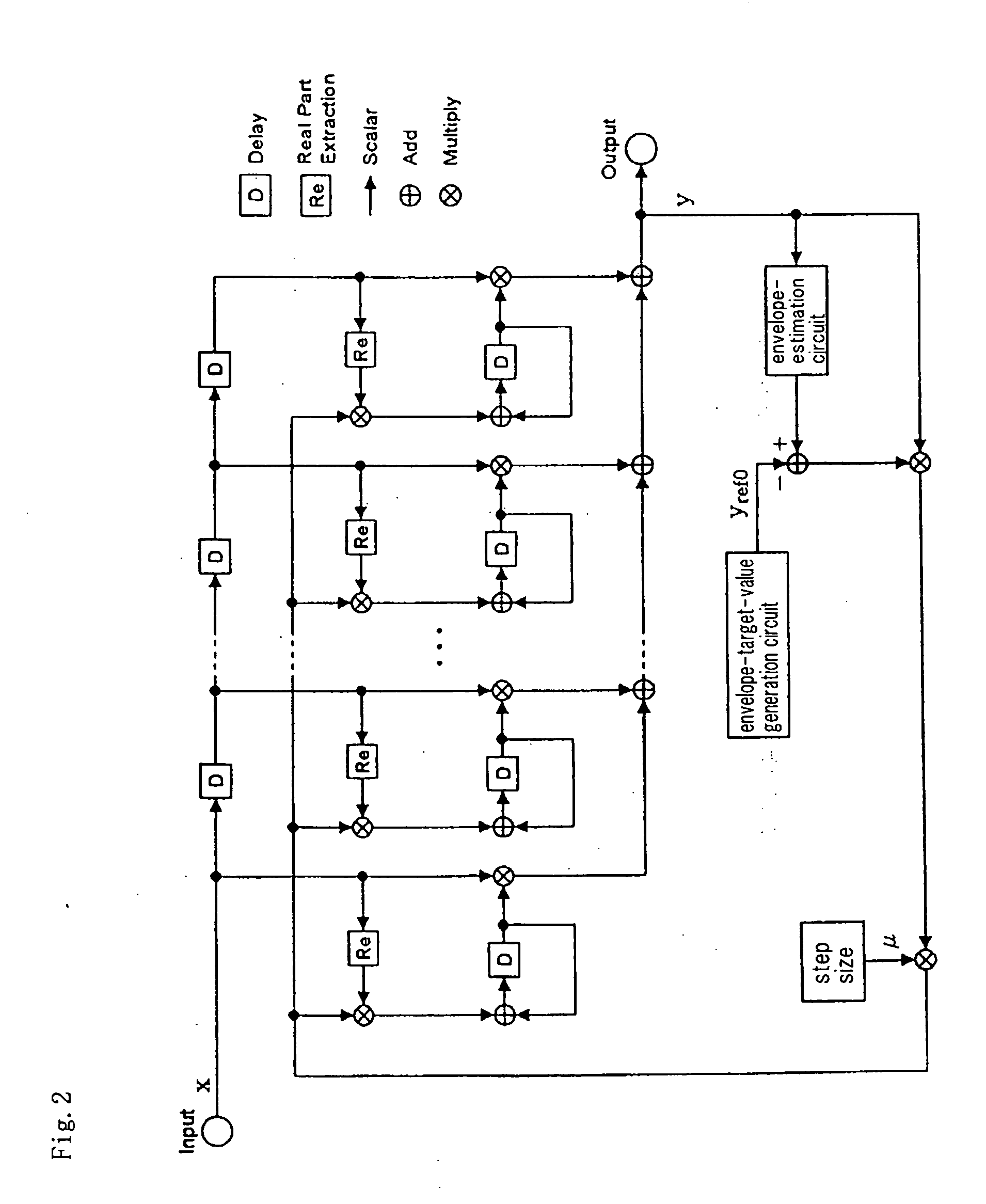

Adaptive Digital Filter, FM Receiver, Signal Processing Method, and Program

InactiveUS20090207955A1A large amountReduce the amount of solutionTransmission control/equlisationError preventionBinary multiplierTarget signal

The adaptive digital filter of the present invention includes: a filter unit that includes a plurality of multipliers (3360-336N-1) that are divided into groups of at least one multiplier and the other multipliers based on expected values of filter coefficients and that generates first signals by means of convolution operations of an input signal and filter coefficients; an adder (338) that adds the input signal that is applied to at least one multiplier (336M-1) and first signals and supplies the results as second signals; and coefficient control unit (318 and 3190-319N-1) that control filter coefficients based on error between a target signal and an index value derived from the second signals.

Owner:NEC CORP

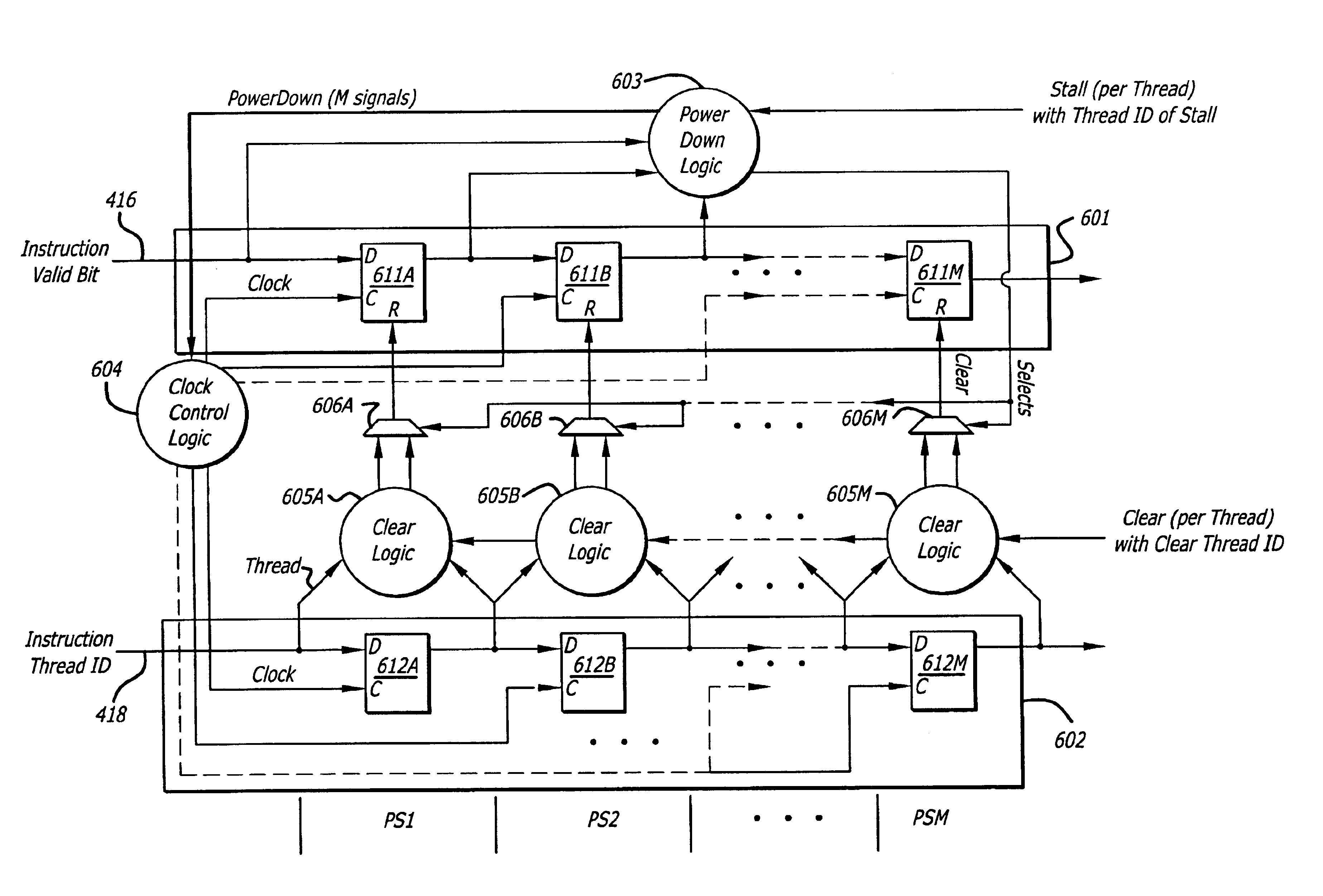

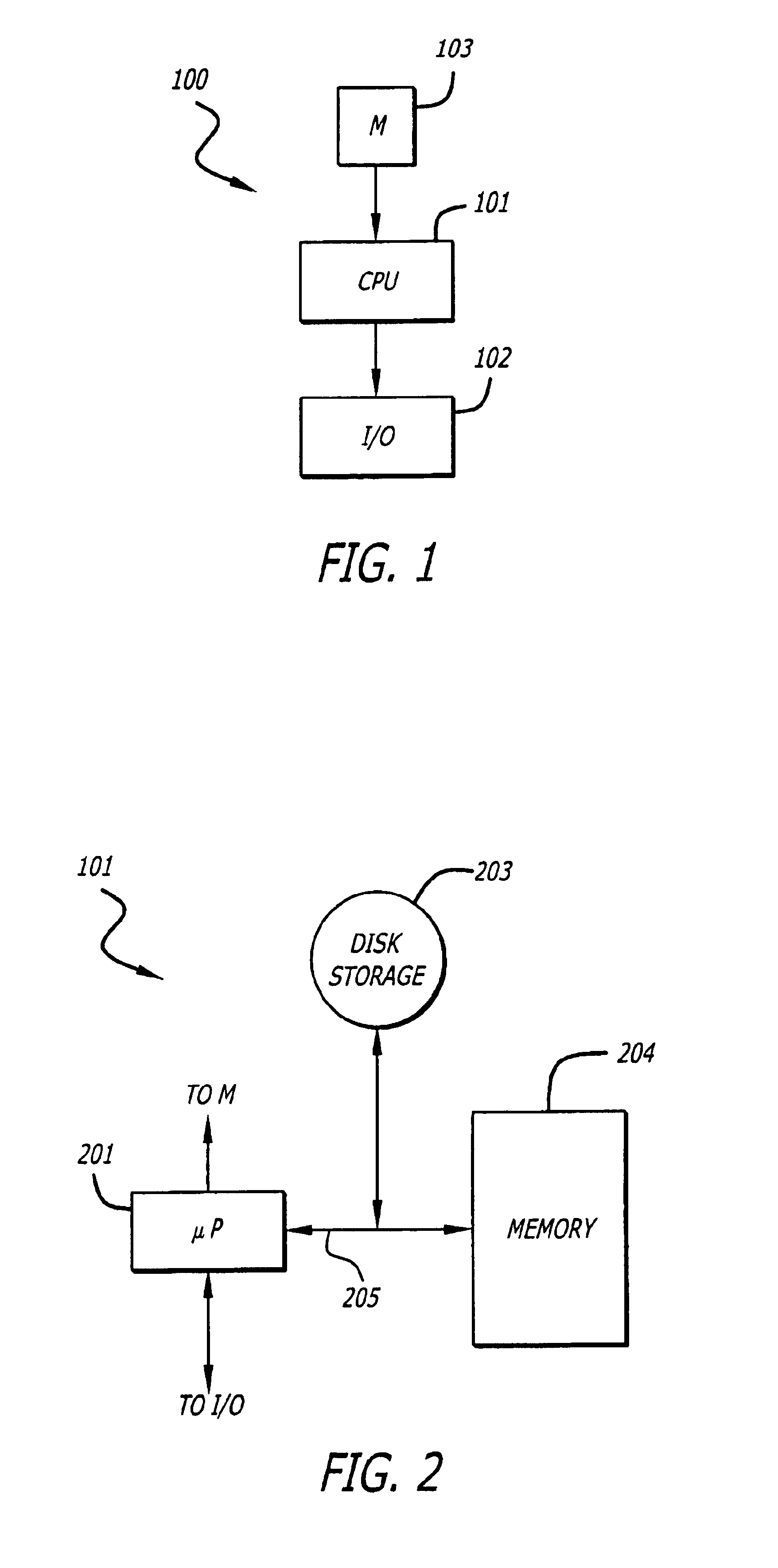

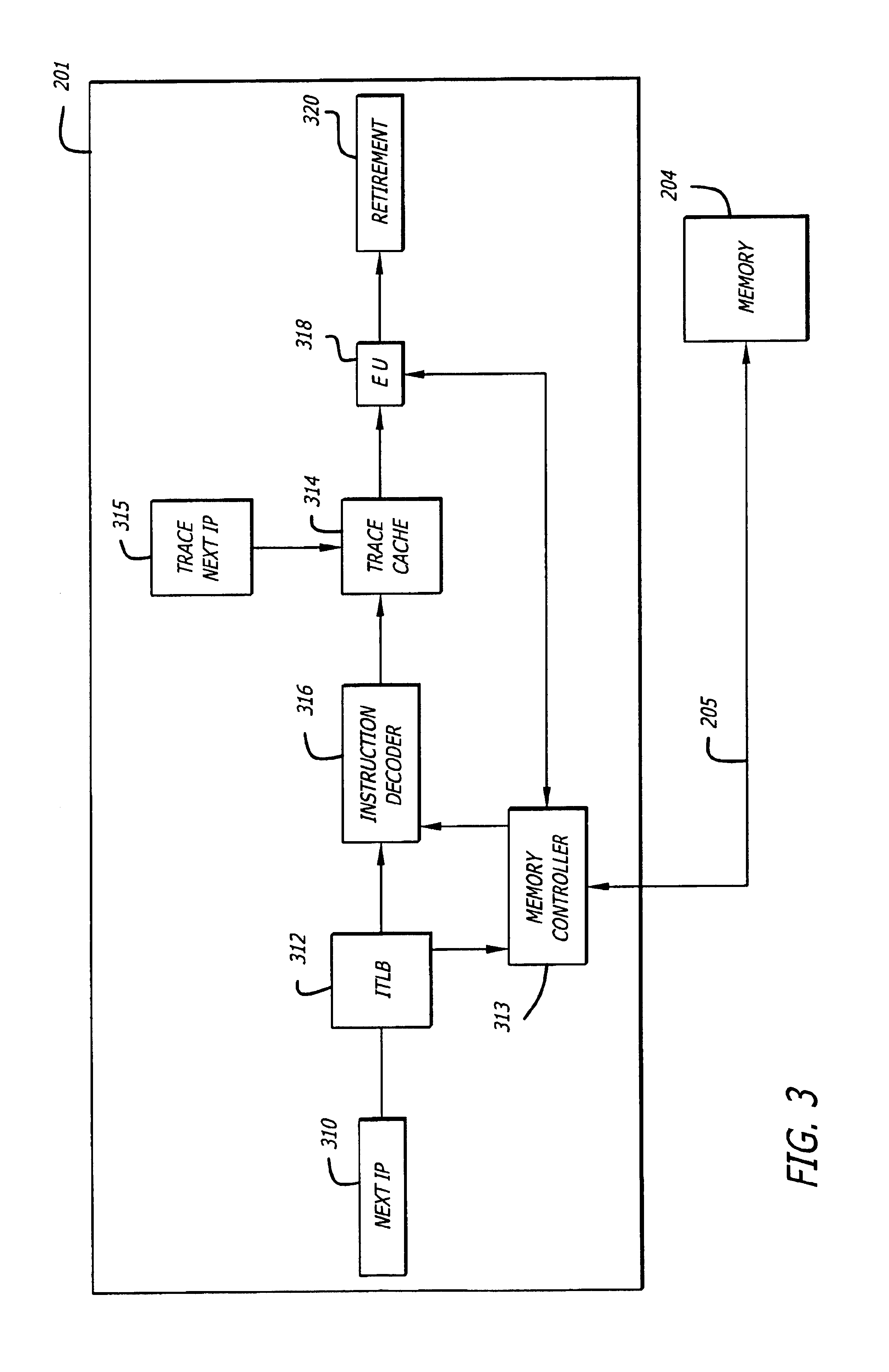

Pipelined instruction decoder for multi-threaded processors

InactiveUS6931516B2High bandwidthSave powerDigital data processing detailsDigital computer detailsParallel computingInstruction decoder

A pipelined instruction decoder for a multithread processor including an instruction decode pipeline, a valid bit pipeline, and a thread identification pipeline in parallel together, with each having the same predetermined number of pipe stages. The instruction decode pipeline to decode instructions associated with a plurality of instruction threads. The valid bit pipeline to associate a valid indicator at each pipe stage with each instruction being decoded in the instruction decode pipeline. The thread identification pipeline to associate a thread-identification at each pipestage with each instruction being decoded in the instruction decode pipeline. The pipelined instruction decoder may further include a pipeline controller to control the clocking of each pipe stage of the instruction decode pipeline, the valid bit pipeline, and the thread identification pipeline. The pipeline controller may invalidate an entire thread of instructions, squeeze out invalid instructions, and / or conserve power by selectively stopping the clocking of pipestages.

Owner:INTEL CORP

Fault tolerant control system

ActiveUS20080072099A1Reduce the amount of hardwareReduce the amount requiredFault responseData processing systemParallel computing

A fault tolerant data processing system for controlling a real time process. The system is tolerant to systematic faults in its software. The system includes a data processor unit with a program memory and a data memory and input and output units where program software residing in the program memory can be executed on the data processor unit. The system includes a normal-mode software program residing in the program memory, and a backup-mode software program also residing in the program memory arranged to perform the same or similar function of the normal mode software program but being differently implemented than the normal-mode software program, and where a trigger signal received by the data processor unit can switch execution control such that the normal-mode software program stops executing and the backup-mode software program starts executing.

Owner:SAAB AB

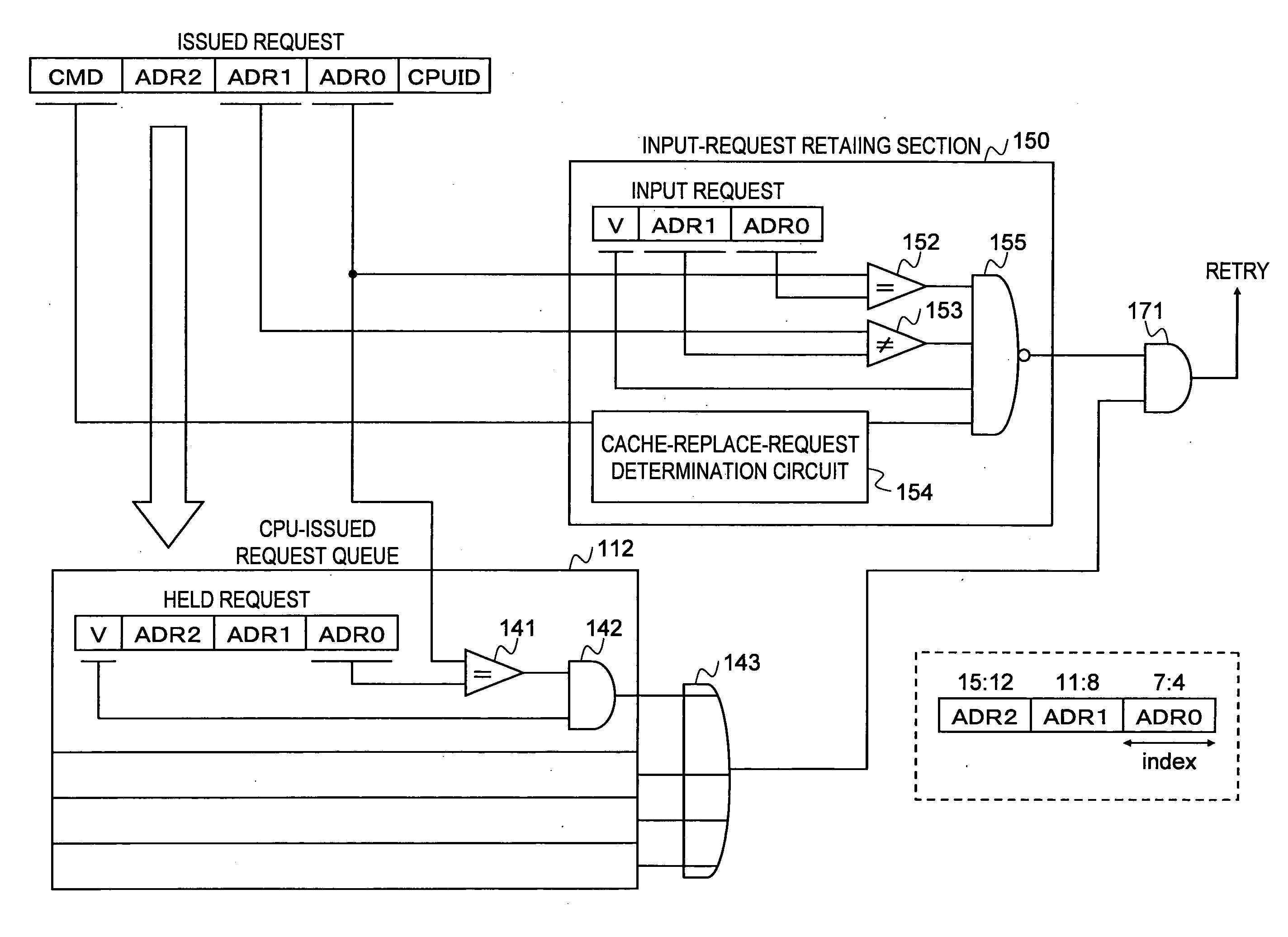

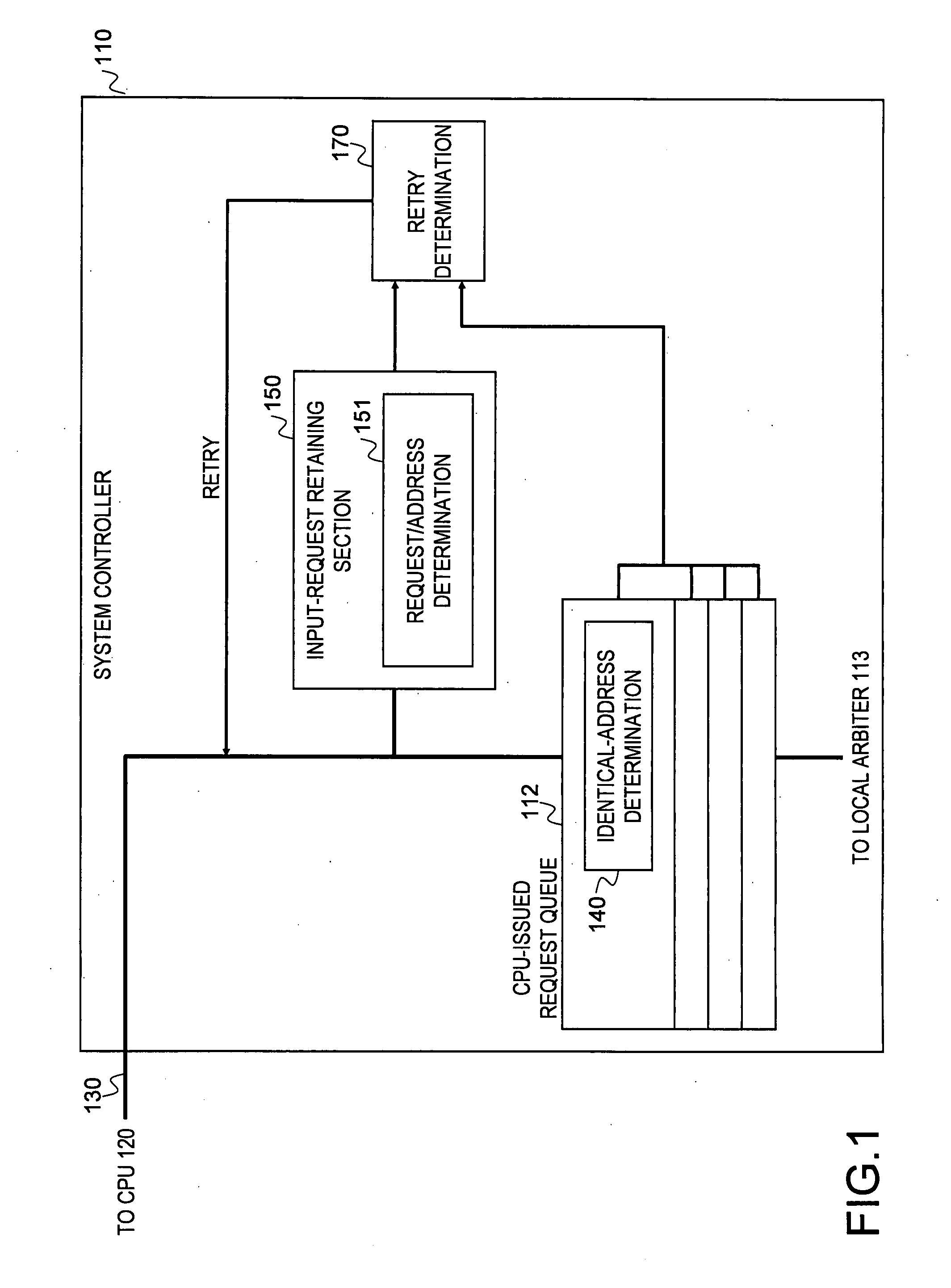

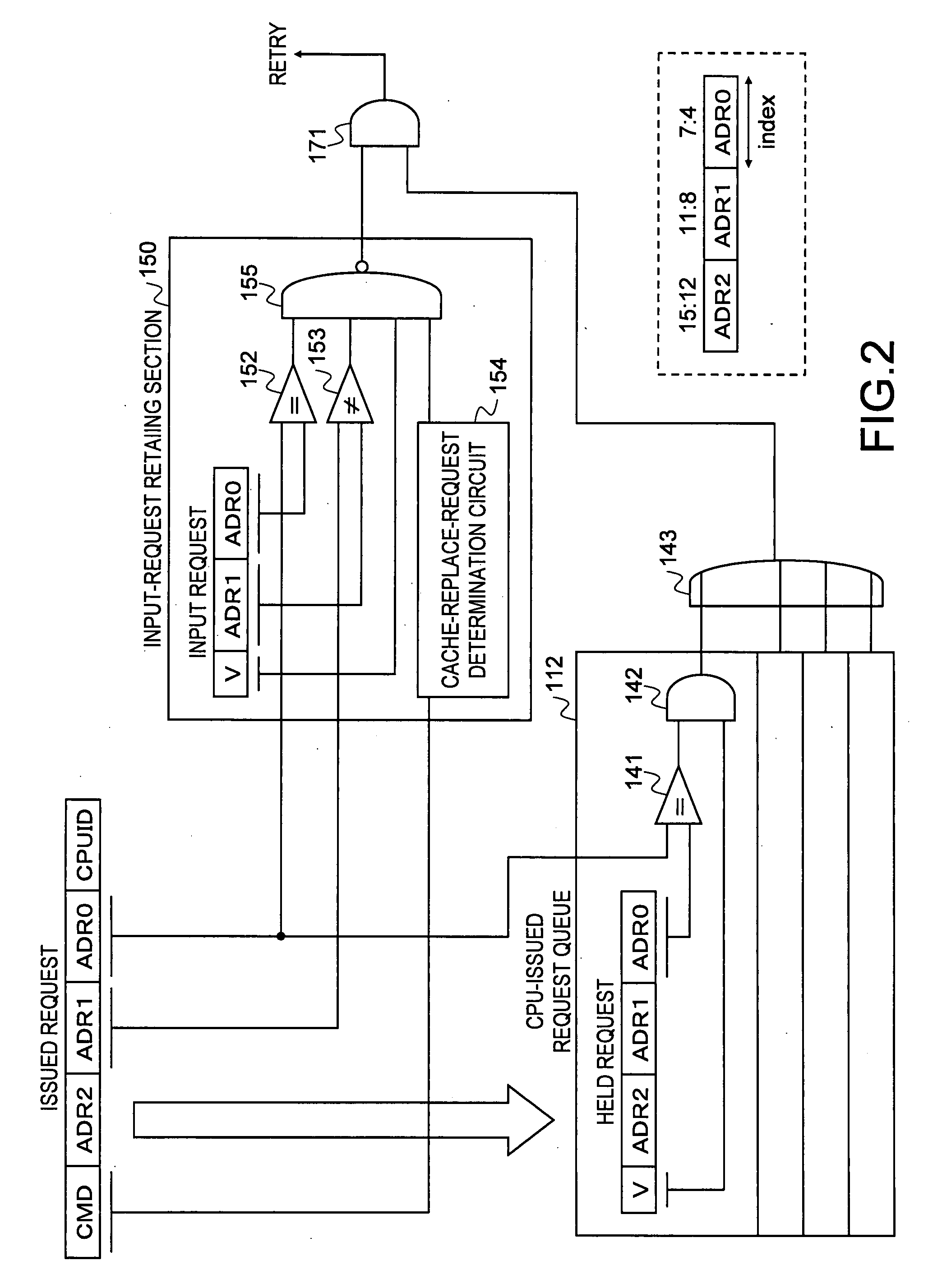

System controller, identical-address-request-queuing preventing method, and information processing apparatus having identical-address-request-queuing preventing function

InactiveUS20080046695A1Reduce the amount of hardwareAvoid queuingMemory adressing/allocation/relocationDigital computer detailsInformation processingSystem controller

In a system controller including a CPU-issued request queue having a circuit that processes plural requests having identical addresses not to be inputted to the CPU-issued request queue, a latest request other than a cache replace request is retained by an input-request retaining section. Consequently, even if an address of an issued request for cache replace request matches an address of a request retained by the CPU-issued request queue, the issued request for the cache replace request is not retried but is queued in the CPU-issued request queue when the address of the issued request for the cache replace request does not match the entire address retained by the input-request retaining section.

Owner:FUJITSU LTD

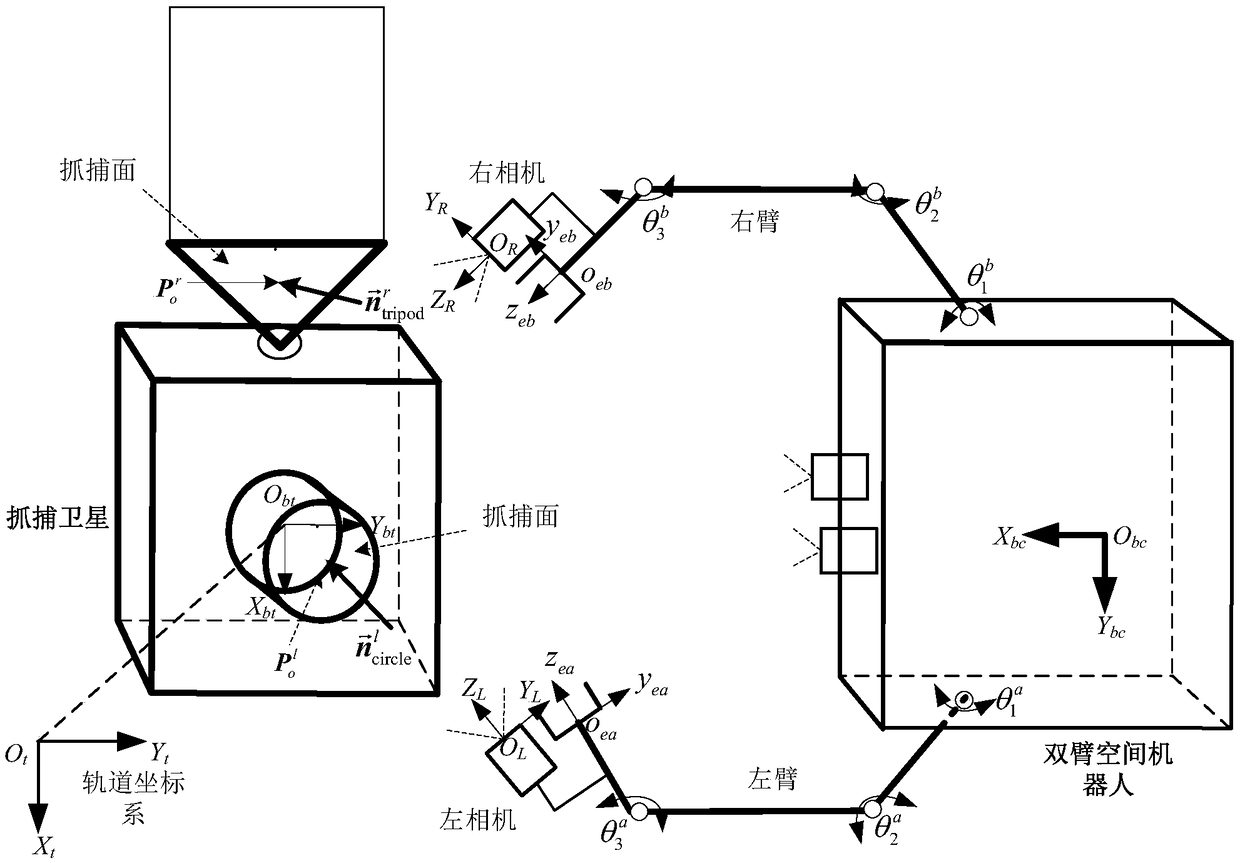

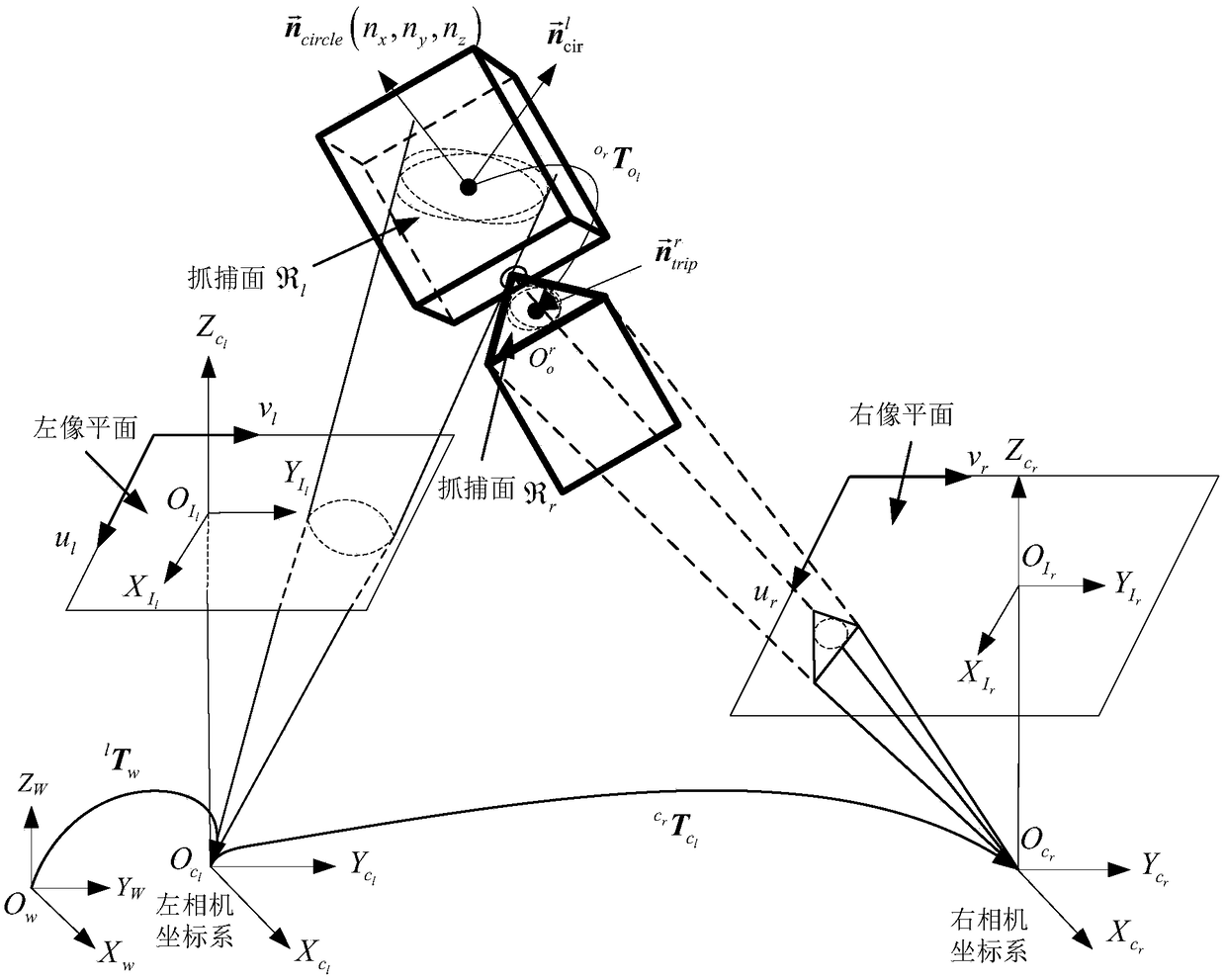

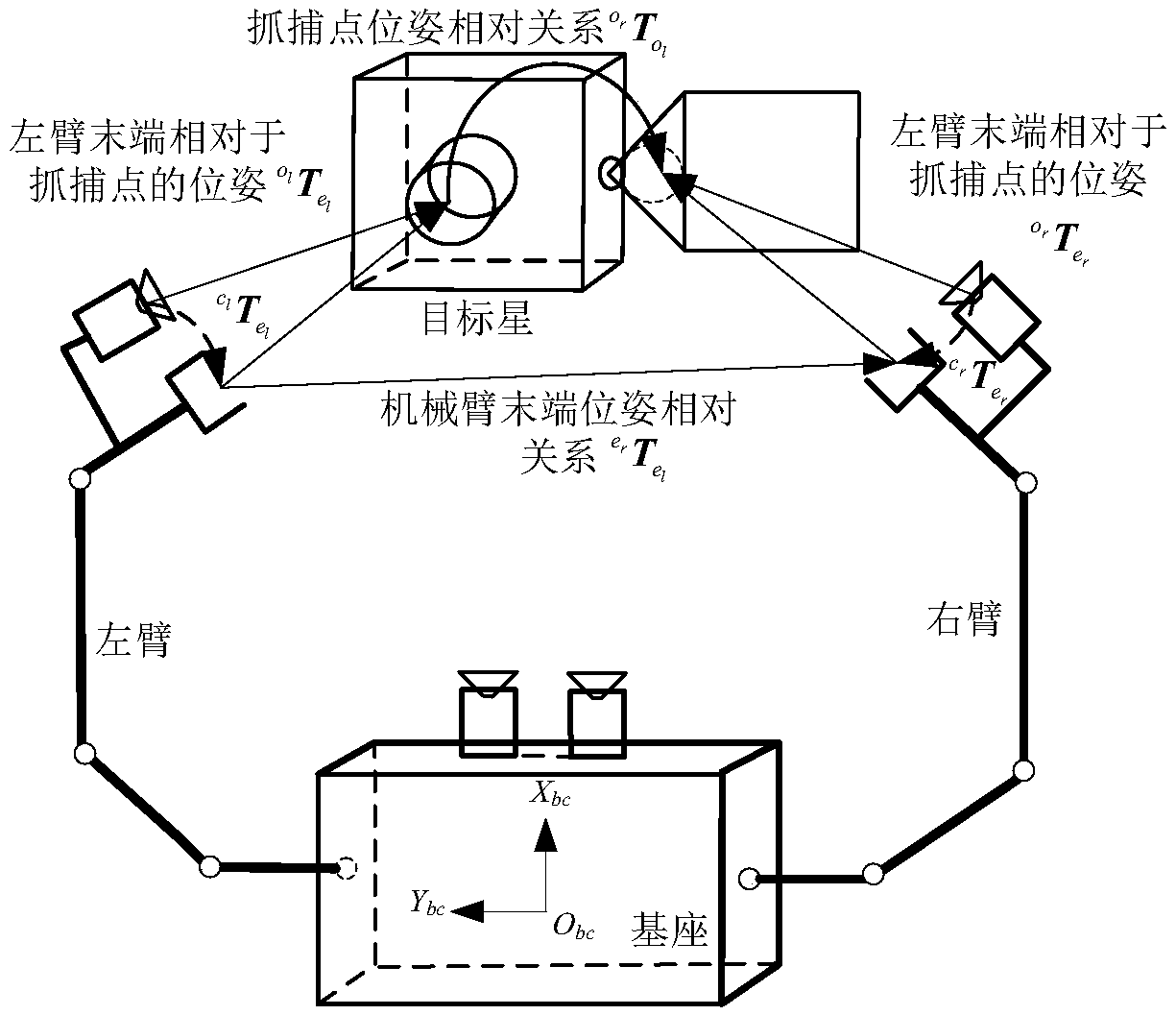

Virtual stereoscopic vision-based non-cooperative target cooperative measuring method and system

ActiveCN109115184AReduce in quantityImprove abilitiesToolsPicture interpretationVision basedPre treatment

The invention discloses a virtual stereoscopic vision-based non-cooperative target cooperative measuring method. The virtual stereoscopic vision-based non-cooperative target cooperative measuring method comprises following steps: three dimensional cloud of points of a non-cooperative tumbling target are obtained; the relative pose relation of a satellite nozzle center and an A-frame inscribed circle center is extracted; the obtained satellite nozzle and A-frame image are subjected to image pre-treatment processing; coordinate transition is carried out so as to obtain the pose relation at a specific coordinate system; the radius of the satellite nozzle and the A-frame inscribed circle are obtained, and the pose information of the nozzle and the A-frame center is obtained. The invention alsodiscloses a virtual stereoscopic vision-based non-cooperative target cooperative measuring system. The virtual stereoscopic vision-based non-cooperative target cooperative measuring method is capableof reducing the hardware numbers of the measuring system, improving the capacity of the measuring system, reducing sensor numbers, reducing space emission cost, expanding space measuring capacity, isrelatively high in calculation efficiency, and can be widely used in the technical field of space non-cooperative satellite vision measuring.

Owner:HARBIN INST OF TECH SHENZHEN GRADUATE SCHOOL

Data transfer apparatus

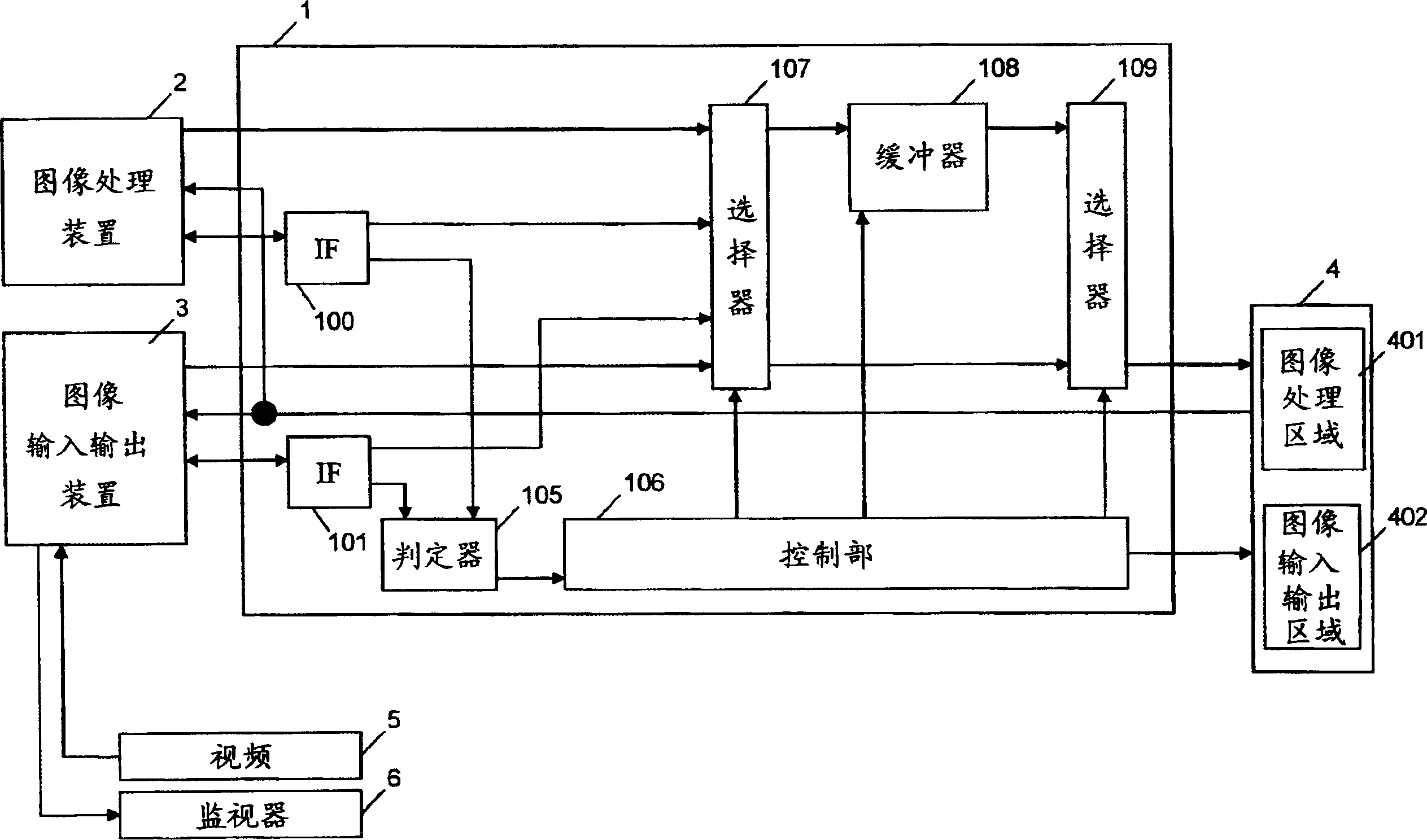

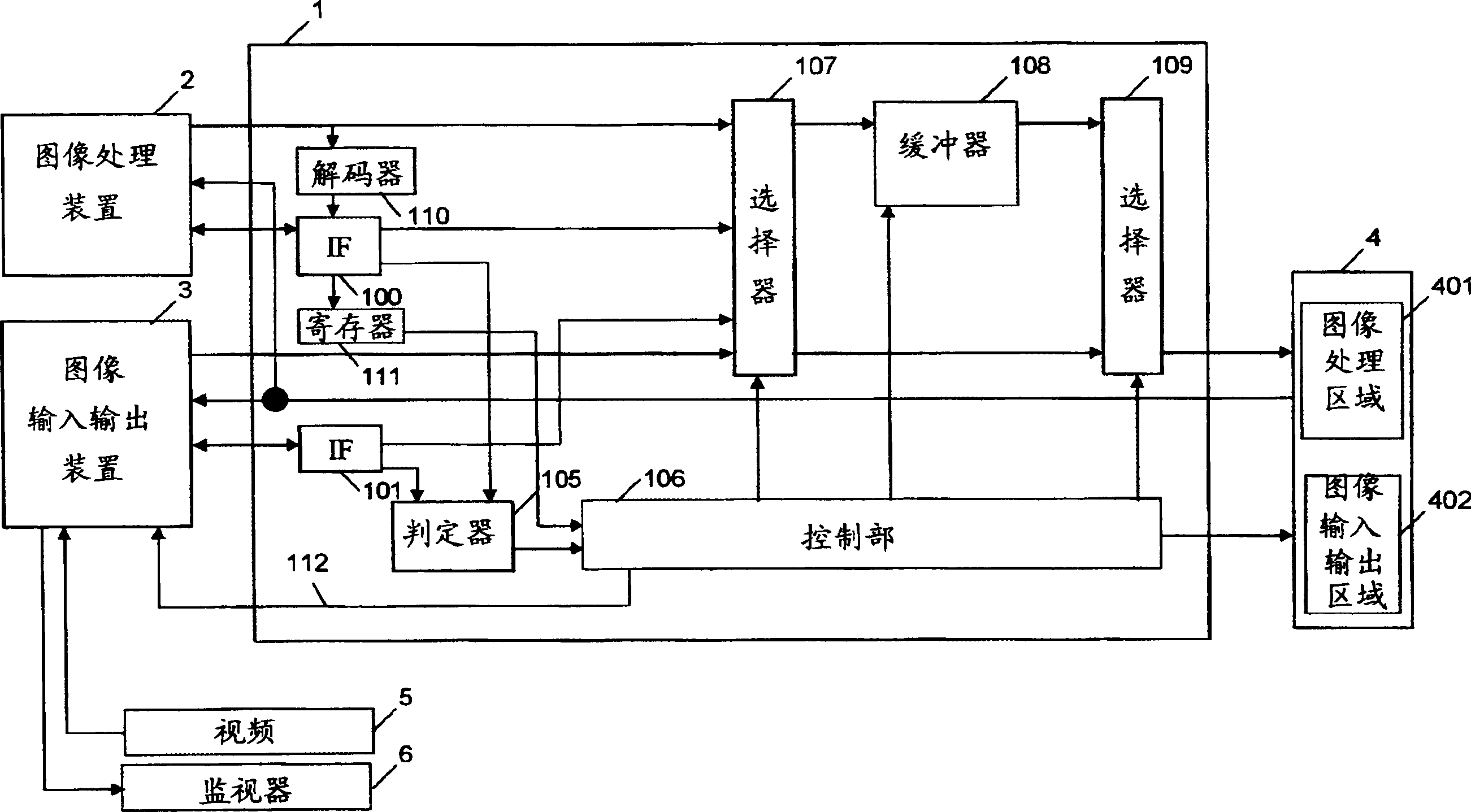

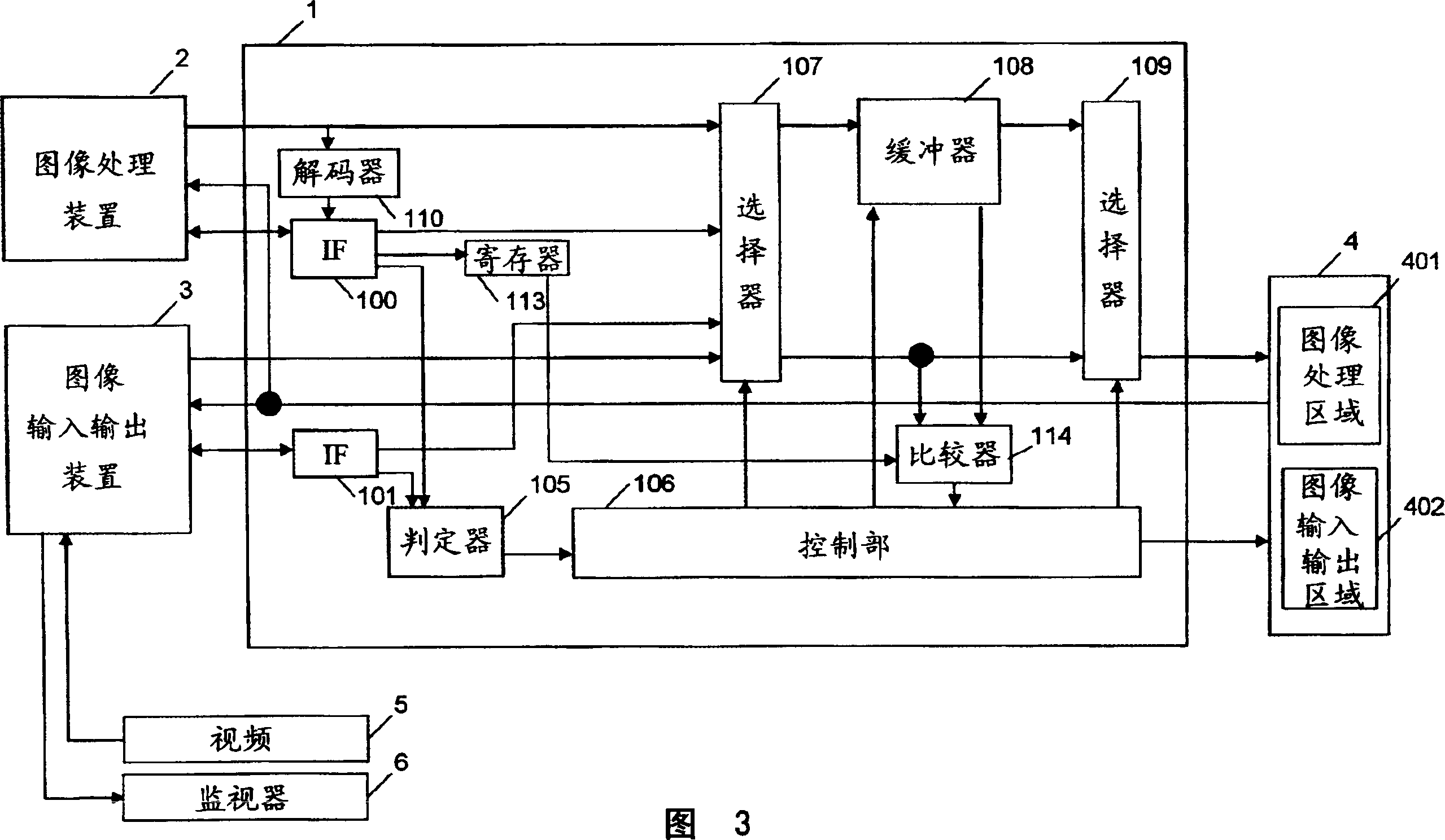

InactiveCN1624673AReduce capacityReduce the amount of hardwareTelevision system detailsTime-division multiplexBurst transmissionControl selection

Owner:PANASONIC CORP

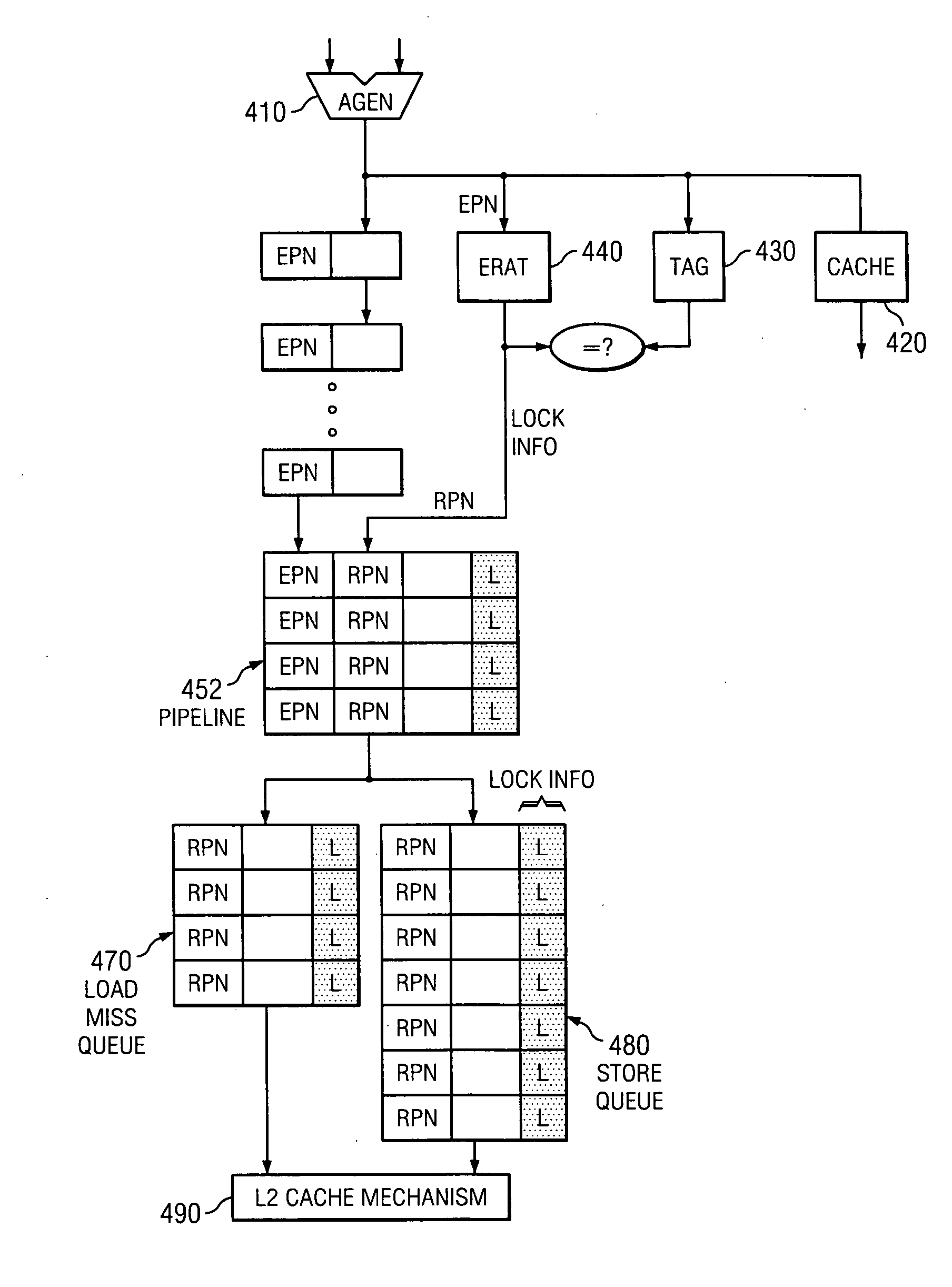

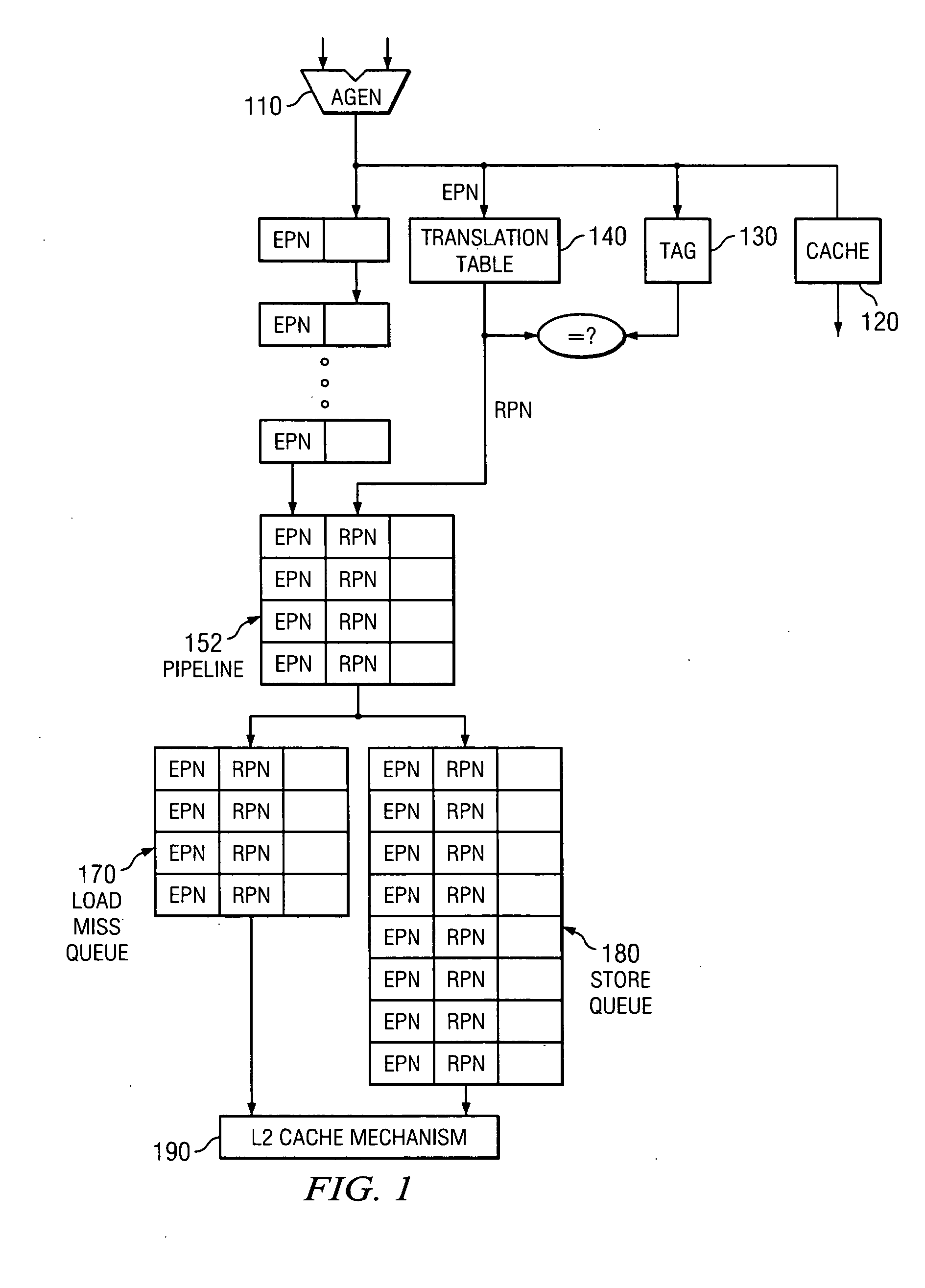

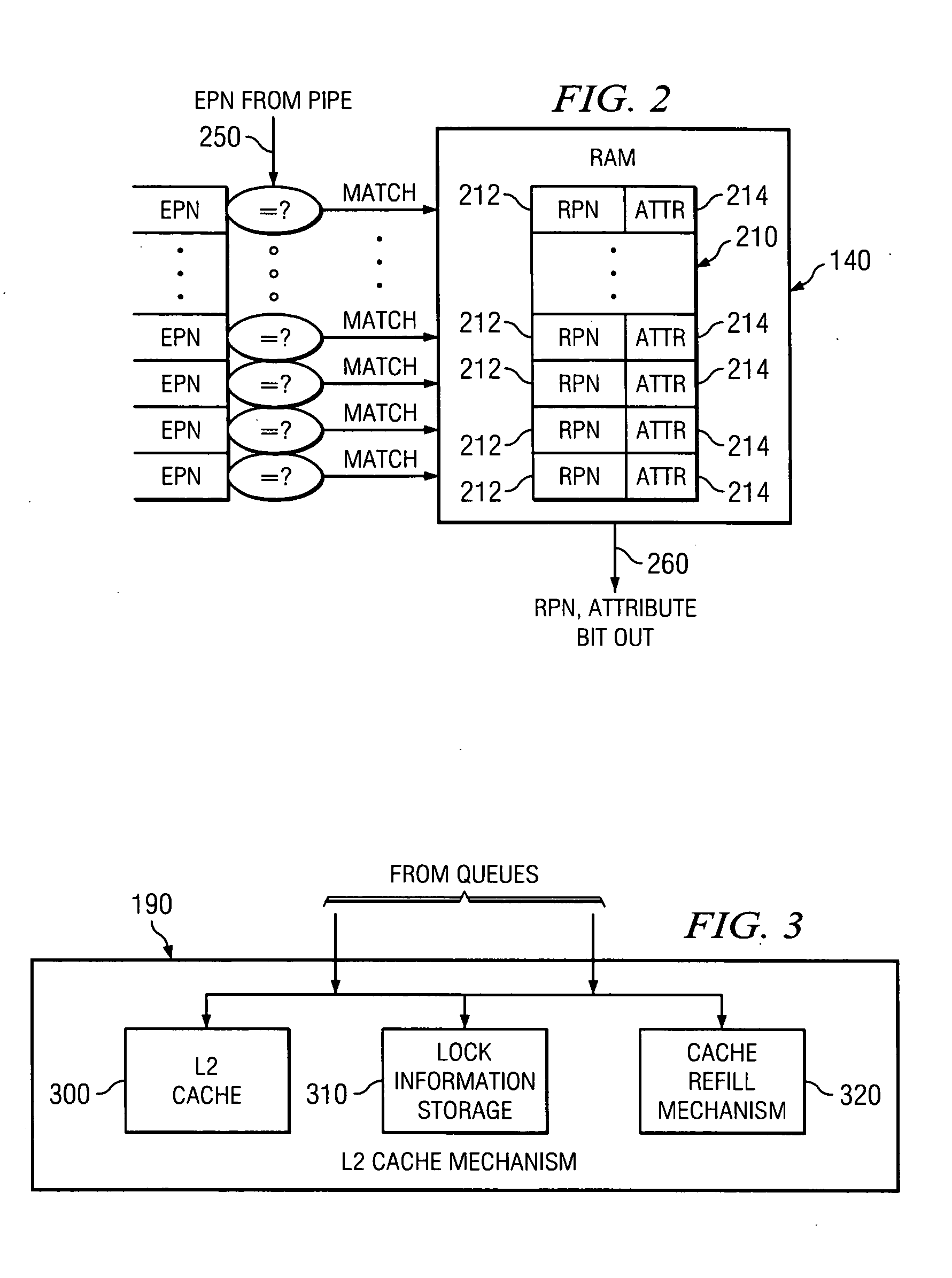

Method and system for efficient cache locking mechanism

ActiveUS20060277351A1Reduce the amount of hardwareEfficient locking mechanismMemory adressing/allocation/relocationUnauthorized memory use protectionPhysical addressData retention

Systems and methods for the implementation of more efficient cache locking mechanisms are disclosed. These systems and methods may alleviate the need to present both a virtual address (VA) and a physical address (PA) to a cache mechanism. A translation table is utilized to store both the address and the locking information associated with a virtual address, and this locking information is passed to the cache along with the address of the data. The cache can then lock data based on this information. Additionally, this locking information may be used to override the replacement mechanism used with the cache, thus keeping locked data in the cache. The translation table may also store translation table lock information such that entries in the translation table are locked as well.

Owner:TOSHIBA ELECTRONICS DEVICES & STORAGE CORPORARTION +1

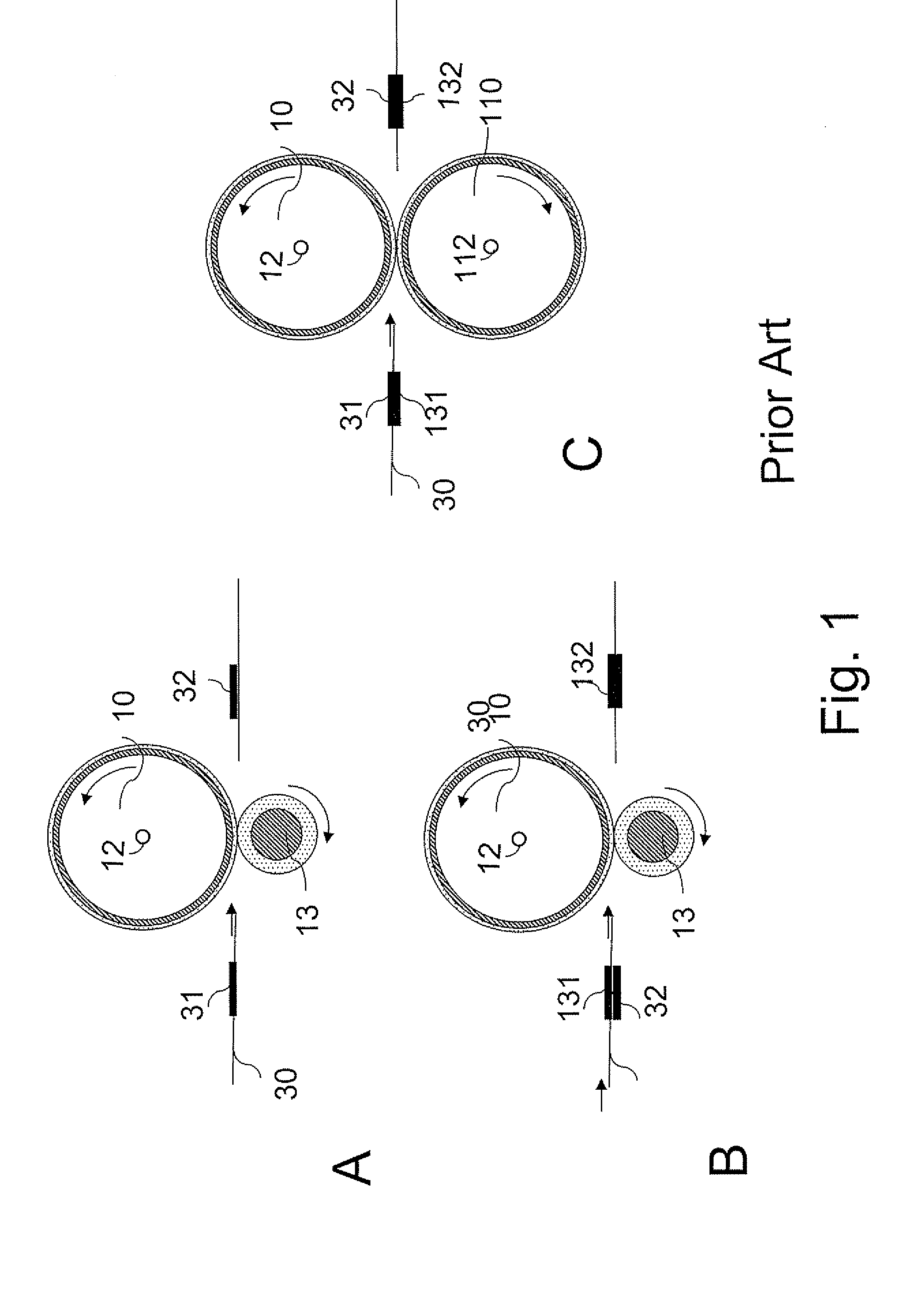

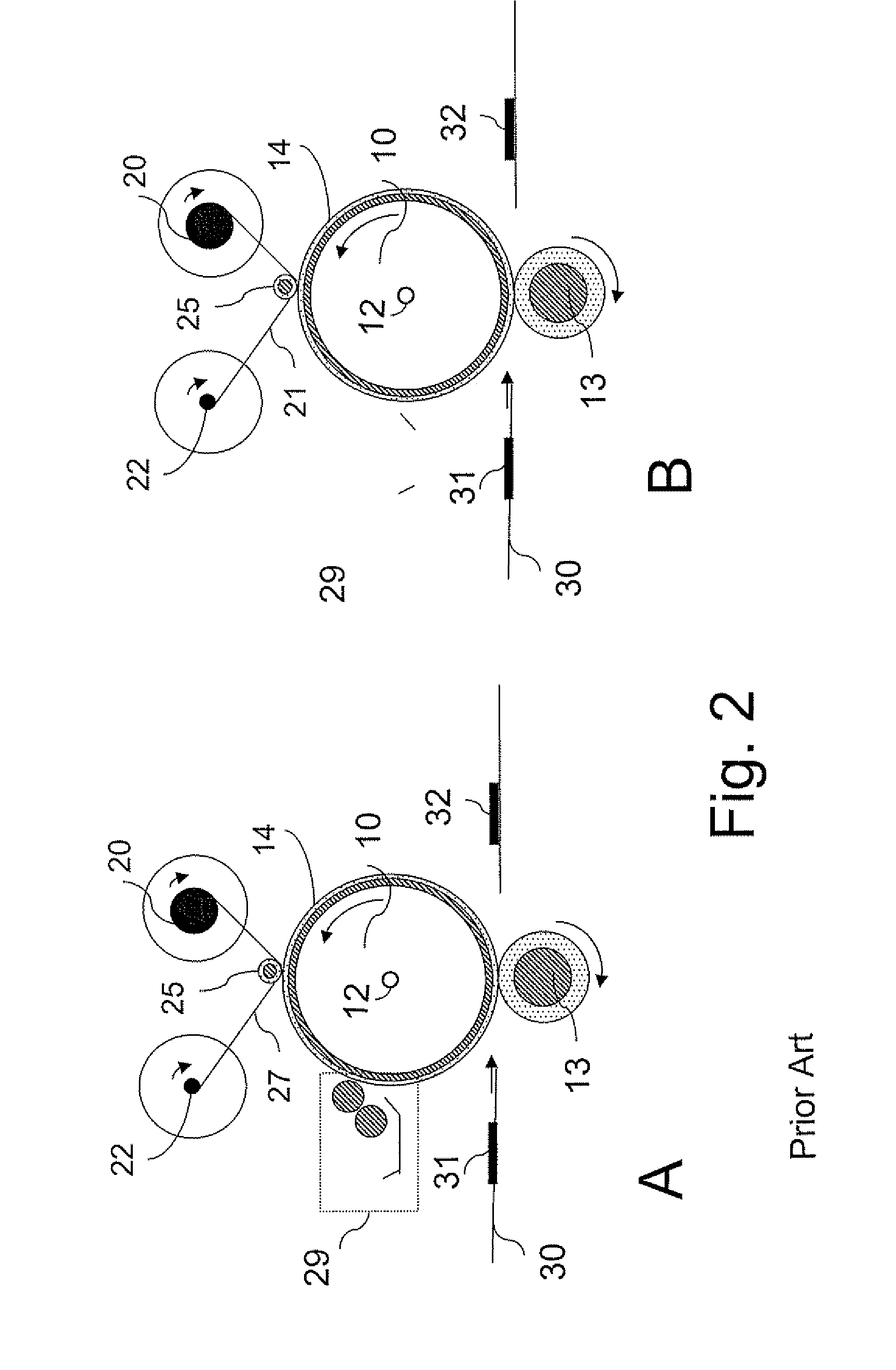

Apparatus and method for release agent application and cleaning of a fuser surface using a release agent impregnated web

ActiveUS20090123200A1Amount of release can be goodExtended service lifeElectrographic process apparatusPrint mediaSurface conditions

An apparatus and method to condition the fuser surface of a fusing or transfusing apparatus for a toner based printing system is described. The apparatus and method integrate the functions of cleaning paper debris and residual toner from the fuser (or transfuse) surface on one hand and the application of a release agent such as silicone oil on the other hand using a single release agent impregnated web. The inventive device includes a release agent application roller and a cleaning roller where the outer surfaces and are selected in preferred embodiments for their respective wetting properties with respect to the release agent used. The fuser surface conditioning device increases the useful life for a fusing or transfusing roll or belt even when low amounts of release agent are applied to the fusing surface such that the amount of release agent that is transferred to the print media is in the range of 0.5 to 5 mg / A4 sheet.

Owner:XEIKON MFG NV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com